简介

近年来,由于元件质量和性能方面的可靠技术进步、元件可用性以及性能改进带来的新兴应用,碳化硅的采用显著加速。UnitedSiC本着不断进行技术创新的策略,在650V-1200V范围内[1]打造了Rds(on)极低的功率元件,这些元件利用了我们专有的SiCJFET技术的出众特性和高产量。随着最新的第四代(G4)UJ4CSiCFET系列的推出,我们翻开了SiC采用量在功率转换和逆变器应用中扩张的新篇章,这些采用伴随着器件特性的大幅改善,旨在为用户带来更上一层的性能和系统成本优势。

可用技术的特性比较

UnitedSiC推出的首批UJ4C产品(见表1)的额定电压VDS(MAX)为750V,而不是650V,以便既能处理使用500V直流总线的应用,又能为传统的300/400V总线应用服务。这些器件的栅极额定值仍为+/-20V,内置静电保护,能够使用以5VVTH支持的简单单极栅极器件,这些都是SiCFET共源共栅结构的特性。在高频应用中,可以使用低至0至10V的栅极驱动电压,且对导通损耗的影响极小。此技术的超低导通电阻(SiCJFET0.7mohm-cm2)使它在给定封装尺寸中的电阻差不多是650VSiCMOSFET的一半。在给定电阻下,芯片体积会缩小,从而使电容显著降低。而这又使得开关损耗降低。TO247-3L和4L封装采用银烧结技术来增强结的热阻且芯片变薄,以降低JFET晶粒较小带来的影响,并支持实现出色的结壳热阻RTHJC。这些器件仍有能力处理雪崩事件,并且尤其擅长处理电流达到额定值2倍的能量较低的大电流雪崩事件。SiCFET的另一特性是出色的第三象限行为,其VFSD值低(<1.5V)且与温度无关的QRR也低,而受COSS降低影响,第四代器件的QRR比第三代器件低得多。

表2中比较了处于前沿的SiCMOSFET、超结器件和第四代SiCFET的技术参数。RDSA参数行表明了在25℃和125℃下有效芯片面积的电阻(mohm-cm2)。这是用于构建共源共栅SiCFET的JFET的电阻,而LVMOS带来的额外电阻可能会让此数字提高10%。采用0至12V栅极驱动的结中的第四代SiCFET的5VVTH非常独特,可实现栅极驱动损耗的最佳可用Qg*V性能表征。可以在500kHz-1MHz下运行这些器件,且不会让标准栅极驱动过热。共源共栅结构允许所有宽带隙选项实现极低的可用VFSD体二极管压降,因而可以在异步整流模式中使用这些器件。由于反向恢复性能QRR也很出色,第四代SiCFET的整体性能表征VF*QRR无可比拟。这能实现出色的硬开关性能,还能阻止当在有任何负载的情况下发生硬开关时零电压开关电路中出现器件故障。基于共源共栅净电阻的性能表征RDS*EOSS和RDS*COSS,TR可评估技术用于软硬开关应用的基本能力,且从表中可以看出,第四代SiCFET的这两个性能表征均为同类最佳。这些器件能更简单地实现更高频率的软开关电路,如LLC、CLLC、DAB和PSFB。

开关波形和管理开关速度

图1表明了TO247-4L封装中的60mohm和18mohm,750V器件的半桥开关波形,分别在400V,20A和400V,50A下测量得出。所示波形比较了采用大Rg来控制开关与使用跨器件的RC缓冲电路并在栅极处采用小Rg这两种情况。两种电路均在直流总线到接地之间采用RC缓冲电路,简称总线缓冲电路[2]。

图1的上面一行显示的是60mohm,750VSiCFETUJ4C075018K4S的开关行为。仅使用25ohm的Rg(171uJ)与同时使用1ohm的小Rg和10ohm,95pF的漏源RC缓冲电路(142uJ)这两种情况下,打开损耗的区别很小。在Rg=25ohm时,打开di/dt明显较慢,但是峰值恢复电流区别不大。打开期间的最大dV/dt类似,因为这是由SiCJFET决定的,而应用于SiCFET中的LVMOSFET的Rg不会改变该值。在Rg为25ohm时打开延迟较高。

使用20ohmRgoff(37uJ)与同时使用1ohmRgoff和10ohm,95pF漏源RC缓冲电路(17uJ)这两种情况下的关闭行为表明,使用缓冲电路时,损耗较低,同时保留关闭延迟短、VDS过冲略低和振铃减小的特性。所示损耗包括缓冲电路损耗,该损耗在数据表中单独列出,而且非常小[2、3]。然而,在电流较小(如20A)时,许多应用中都不需要缓冲电路,因为采用简单Rg控制所增加的损耗不会过大。不过,仍建议采用总线缓冲电路,因为它能提高振铃性能且损耗影响极低。

在50A电流下,使用缓冲电路的波形要远胜另一种情况的波形,且能让总开关损耗(EON+EOFF)降低近36%。使用小Rg时,也能降低延迟时间。图1的下方曲线对比了在两种情况下UJ4C075018K4S(18mohm,750V)在50A,400V下的开关数据:第一种使用25ohmRgon/50ohmRgoff,第二种使用1ohm的Rg并跨每个器件的漏源连接10ohm,300pF的RC缓冲电路。1ohm的小Rg只能在有缓冲电路可以管理过冲与振铃时使用。这种布局允许在更快的di/dt下进行开关,且打开延迟时间缩短。可以看到,现在的打开损耗(包括缓冲电路损耗)为418uJ,而在更快的运行di/dt的驱动下则为483uJ。但是,请注意,这个更快的di/dt没有让峰值恢复电流有任何显著提高。

类似地,图1右下角的50A,400V关闭波形表明,使用1ohmRg和RC缓冲电路实现了快得多的开关速度并减少了延迟时间,而没有过度的VDS过冲或开关节点振铃。关闭延迟时间也非常短。鉴于使用1ohmRg和RC缓冲电路时的EOFF仅为55uJ,而使用50ohm电阻器将电压过冲降低类似水平至时EOFF为255uJ,很明显,在超过20A的较大电流应用中,使用缓冲电路非常有优势。

可以依据应用、整体电路电感和关闭时的峰值电流量准确选择缓冲电路,而如果电流低于25A,可能不需要选择缓冲电路。缓冲电路电阻器的损耗最好通过整合打开和关闭时的V2/R损耗来直接测量。这些值在产品数据表[2]中已经列明,对于采用10ohm,95pF缓冲电路的UJ4C075060K4S而言,在20A,400V下损耗为1.7uJ,而对于采用10ohm,300pF缓冲电路的UJ4C075018K4S而言,在50A,400V下损耗为9.5uJ。

虽然通过相应更改RG值[4],-5V至15/18/20V和其他常用栅极电压轨均可使用,但是建议该器件简单地使用0至12V或15V栅极驱动。当开关频率超过300kHz时,通常采用0至10V电压。

图2比较了在TO247-4L与TO247-3L封装中的18mohm,750V器件与60mohm,750V器件的半桥开关波形,它们的栅极驱动电压为0-15V且仅使用总线缓冲电路。上面一行显示的是60mohm,750V器件开关波形,两个器件的Rgon=1ohm,Rgoff=20ohm。实线为3L封装波形,虚线为TO247-4L封装波形。当然,预计TO247-4L封装的打开di/dt较快,因为绕过了共源电感,因而虽然电流峰值较高,但是造成的EON较低。采用TO247-4L封装时,栅极VGS振铃得到大幅改善。虽然在此图中,3L封装的峰值VDS过冲较低,EOFF较高,但是在关闭时,TO247-4L封装的VGS振铃较好。

图2的下半部分着眼于半桥电路中使用两种封装类型的18mohm,750V器件在50A,400V下的开关行为,每个均采用10ohm,300pF缓冲电路,Rg=1ohm且栅极驱动电压为0-15V。现在,在3L和4L两种封装类型中,波形和开关损耗存在较大的差异。3L器件的打开损耗(1.67倍)和关闭损耗(4倍)明显较高,VDS过冲和dV/dts类似,而VGS振铃较大,尤其是在关闭时。很明显,对于在较大电流下采用TO247封装的情况而言,将4L封装与器件RC缓冲电路结合可实现最佳性能和能妥善管理的开关波形。

应用益处概述

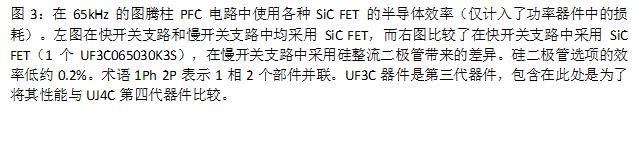

现在,我们可以看看第四代SiCFET的这些特性如何影响一系列器件应用。图3a显示的是在3.6KW图腾柱PFC电路中使用60mohm,750V器件的示例。图中的半导体效率是使用测量得到的器件导通损耗和开关损耗计算得出的,计入了温度上升的影响,但未计入控制器、电感或其他系统损耗。导通和开关损耗低、二极管恢复性能出色和栅极驱动简单这三个特性带来了此处可以看到的高效率。这一效率等于或超过了成本更高的SiCMOSFET选项所能实现的效率,后者需要的栅极驱动也更为复杂。3L和4L版本的TO247封装均可受到支持。图3b显示的也是这些数据,比较了此效率与用硅整流二极管而非SiCFET替换的图腾柱PFC慢支路的效率。硅二极管选项较为实惠,节省了两个晶体管和栅极驱动,但是在高压下效率会下降0.2%。对于1.5KW应用,一个60mohmFET就已足够,而对于3至3.6KW应用,最好使用一个18mohm元件或两个60mohm元件并联。采用一个18mohm器件时,需要的栅极驱动功率较低,占用的空间较少。

表3显示的是在3600WLLC应用中采用60mohm,750V和18mohm,750VSiCFET时对半导体损耗的类似估值。在估算每个器件在最大负载下的净损耗时,计算了导通损耗、栅极驱动损耗和二极管损耗。使用2个并联的60mohmSiCFET或一个18mohmSiCFET时,即使频率达到500kHz,也能将每个FET的损耗控制在6.3W以下,因而非常高效且散热需要极小。虽然损耗主要为导通损耗,但是表中也列出了关闭损耗、栅极驱动损耗和二极管导通损耗的大小,可以看出,由于第四代SiCFET的特性,这几个损耗都很小。

采用UnitedSiCFET是在此类软开关应用中提高效率的简单途径,而且无需对栅极驱动进行大幅更改。在此情况下,当不能执行零电压开关工作时,器件能进行硬开关而不会导致二极管恢复性能差,从而确保不会发生故障。在需要时,额外的电压裕度能延长现场使用寿命。

总结

在本文中,我们回顾了UnitedSiC的全新第四代UJ4C750VSiCFET的参数,并与600/650V等级的SiCMOSFET和超结FET进行了对比。之后,我们深入钻研了这些器件在TO247-4L和TO247-3L这两种封装中的开关特性,并证明了TO247-4L封装的多项优势,还证明了在电流超过25A时,RC缓冲电路在管理开关波形和尽量降低损耗方面的价值。我们运用已知器件参数得出图腾柱PFC电路和LLC电路示例中的损耗,表明了这些器件如何才能在简单的栅极驱动实施下实现80PlusTitanium效率。这些器件在软硬开关应用中的优势、较为简单的栅极驱动和额外的100V余裕使其成为快速扩张的适合600-750V应用的SiC晶体管领域中一颗引人注目的新星,这些应用包括电动车充电器、电动车直流转换器、数据中心、通信电源、可再生能源和能量存储领域的应用。有关其他详情,请参见UnitedSiC网站。

图1:第四代SiCFET产品的半桥开关波形。上面一行显示的是60mohm,750V器件在20A,400V下的行为,而下面一行显示的是18mohm,750V器件在50A,400V下的行为。左列显示的是打开波形,右列显示的关闭波形。虚线使用外部小RG并在PCB上各个器件的漏源之间使用RC缓冲电路,而实线使用外部大RG值来降低开关速度。在所有情况下均采用总线缓冲电路,即将一个电阻与总线去耦陶瓷电容器(2.5ohm,100nF)串联,且栅极驱动电压介于0至15V之间。

图2:在TO247-3L与TO247-4L封装中的第四代SiCFET产品的半桥开关波形对比。上面一行显示的是60mohm,750V器件在20A,400V下的行为,下面一行显示的是18mohm,750V器件在50A,400V下的行为。左列显示的打开波形,右列显示的关闭波形。虚线表示开尔文源K4STO247-4L封装,实线表示K3S标准TO247-3L封装。在所有情况下均采用总线缓冲电路,即将一个电阻与总线去耦陶瓷电容器(2.5ohm,100nF)串联,且栅极驱动电压介于0至15V之间。上面一行表示的是,在Rgon=1ohm,Rgoff=20ohm且没有任何RC器件缓冲电路的情况下测量了两个封装中的60mohm,750V器件。下面一行表示的是,在给定50A,400V开关的情况下,跨每个18mohm,750VSiCFET连接了一个10ohm,300pF的漏源缓冲电路,且使用了1ohm的Rg。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多