1 引言

的功能。

2 AD9911简介

3 FPGA控制AD9911的具体实现

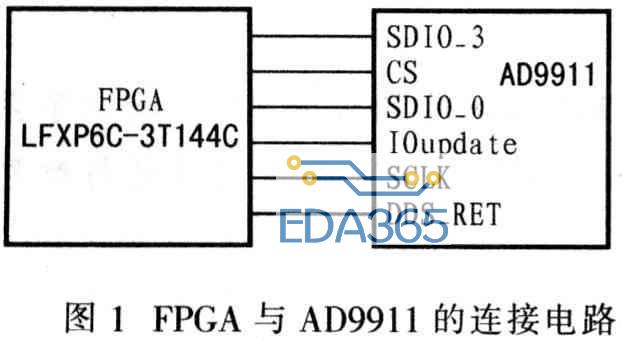

采用Lattice公司的FPGALFXP6C-3T144C控制AD99ll,该器件的外部时钟频率为25 MHz,内部自带2个锁相环,通过PLL倍频时钟频率高达500 MHz,10个RAM块,每一个RAM块的容量都是9 Kbit,提供分布式RAM,5 800个LUT,720个PFU,共有8个模块144位的I/O端口,其中单独输入/输出设置101个端口。一个I/O端口用作外部时钟的输入,另一个I/0端口用作系统上电复位中断输入。LatticeXP器件将非易失的Flash单元和SRAM技术组合在一起,无需配置器件提供支持“瞬间”启动和无限可重复配置的单芯片解决方案。上电时。该配置在1 ms内从Flash存储器中被传送到SRAM中,可提供瞬时上电的FPGA。

设置AD99ll的25个寄存器,其中地址为0X00~0X03的寄存器是控制寄存器,分别用于控制设置工作模式、比较器、输出度、系统时钟等。

首先,设置地址为0X00的寄存器CSR,用于选择通道及通道输入/输出模式。本系统设计选用最基础的SINGLE-TONE工作模式,数据输入方式定义为MSB,则0X00寄存器中的内容应为0X20。

地址为0X0l的寄存器FRl用于控制器件的工作模式,包括器件内部PLL倍乘器的开关与倍数、系统时钟开关、多芯片通信同步控制、Test—tone模式、Shift—Keying模式控制等。AD99ll外部采用25MHz的晶体振荡器,系统时钟设定为500 MHz,未使用Test—tone模式和Shift Keying模式,因此将0X0l寄存器中的VCO gain control位置为l,倍乘器倍数置为20,其他控制位全置为0。这样地址为0X0l寄存器中的内容应为0XDO_00_00。

此外,地址为0X02的寄存器主要控制多芯片通信模式和线性扫频。地址为0X03的寄存器CFR主要控制器件的输出波形和线性扫频。由于本系统设计无需对相位累加器清零,只需使输出波形正弦化,因此该寄存器内容应为0X00_03_01。然后再设置频率寄存器、幅度寄存器、相位寄存器。由于采用Single-Tone工作模式,且只利用频率调制,因此只需设置地址为0X04的寄存器即可。该寄存器又称CTW0寄存器,用于控制波形频率,精度为32位。因此,该寄存器可控制频率为0~250 MHz。

由于对输出波形的相位和幅度无特殊要求,因此,其他寄存器保存为默认值即可。

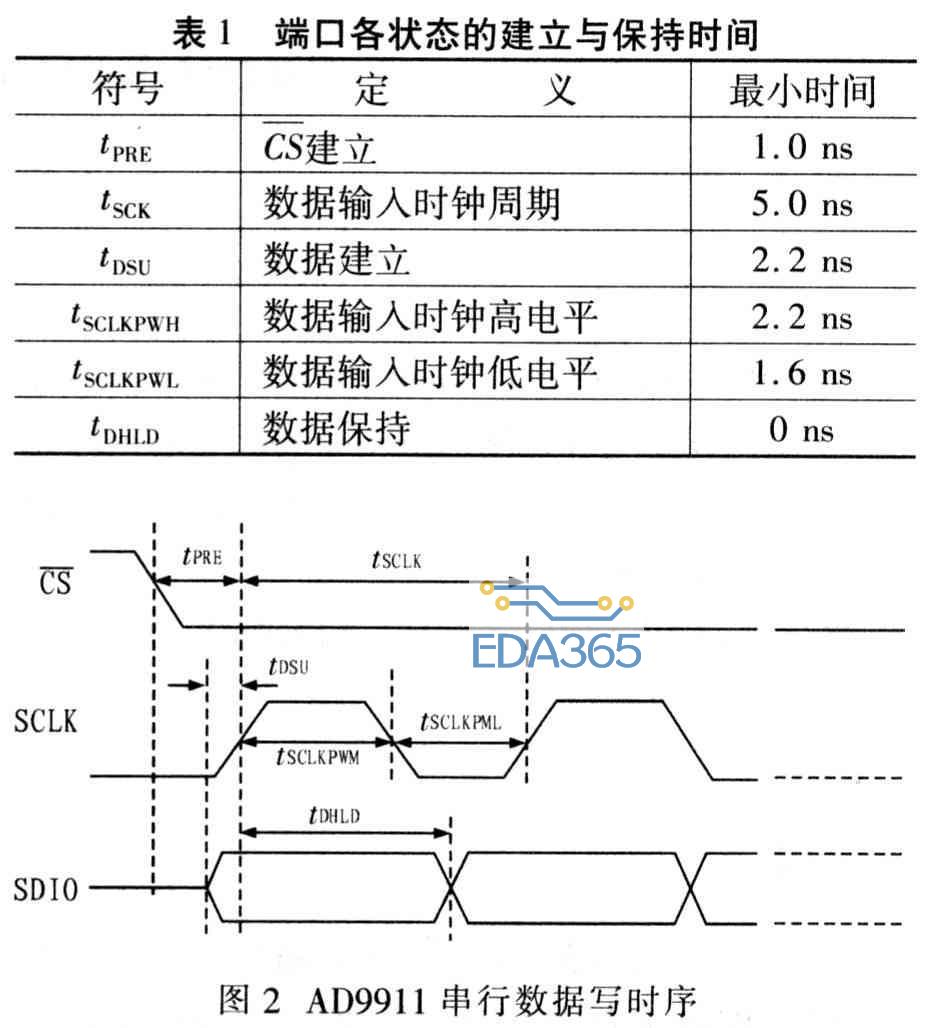

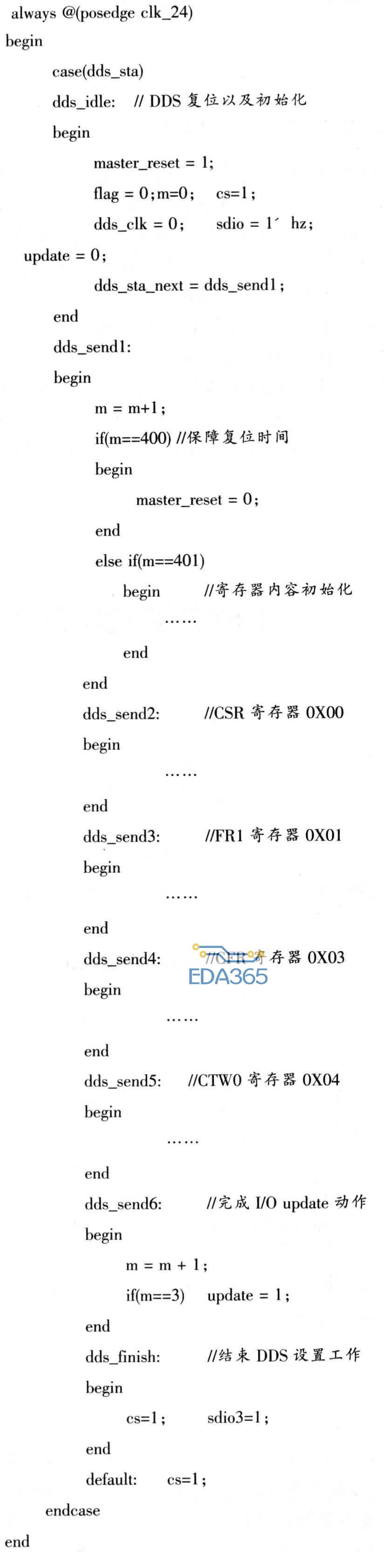

对AD991l读写操作时,需要注意AD9911的时序要求,如图2和表1所示。由于FPGA的系统时钟可在100~300 MHz范围内选择,执行一个指令需占用时间约为3.3~10 ns。鉴于AD9911的时序要求,要求在时间控制方面特别注意。[page]

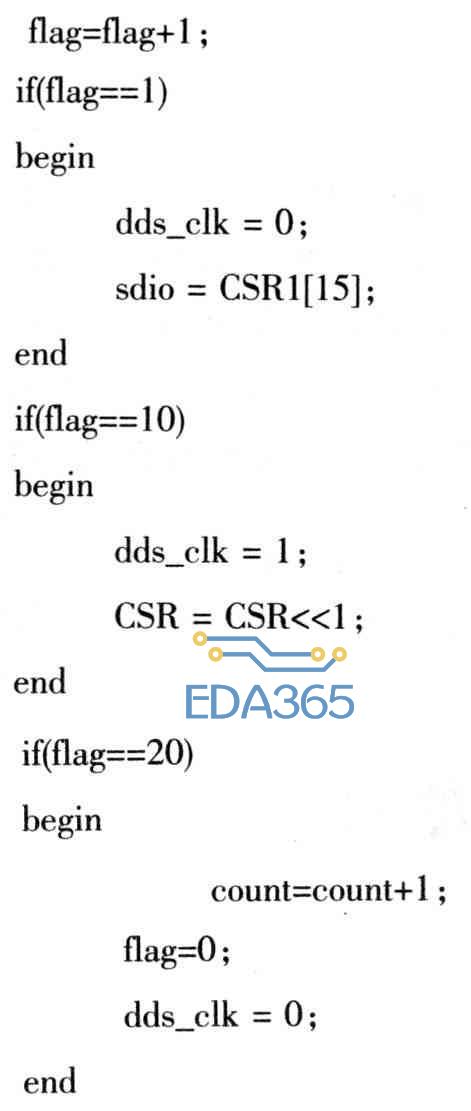

如图2所示,在SCLK上升沿,写入数据有效,FPGA控制SCLK信号的产生。SLCK的最大频率为200 MHz,即要求数据输入的最大频率不能大于200MHz。具体写入数据的程序代码(使用Verilog HDL编写)如下所示:

该指令用于对地址为0X00的通道选择寄存器CSR进行写操作,dds_clk控制SCLK。但鉴于FPGA的高速处理能力,在程序设计时需要注意一些特殊时序要求,如以下几方面问题。

(2)AD99ll开始工作时必须先将其复位,复位时间至少应保持lO个系统工作周期。

(3)如果系统工作需多次使用I/O Update,要注意I/O Update引脚置l的时间控制,这关系到系统是否能顺利设置各个寄存器。

4 例程

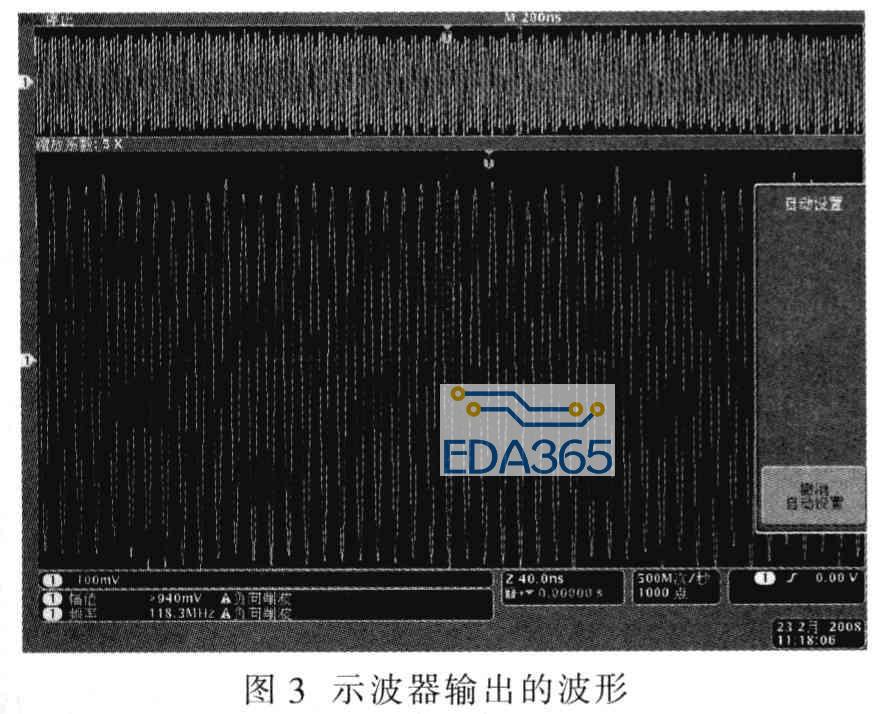

例程中,将update信号设置为手动,通过频率控制寄存器写入频率控制字0X3C91_D14E,此数字转换成十进制为1 016 189 262,代入频率控制字的公式,计算出频率为118.29 MHz。使用示波器测量观察,如图3所示,图像中显示的是激光光绘机激光扫描驱动信号,可以看出,输出波形的频率为118.3 MHz,与初始设定值一致。由此可见,程序符合设计要求。

5 结语

FPGA对AD9ll的控制是通过对其各控制寄存器进行相关设置来实现的。随着FPGA的广泛应用,以及更快的数据处理速度,基于FPGA+DDS在数据处理速度上的优势,FPGA控制DDS不仅可应用于雷达线性扫描和菲林产品的激光扫描驱动等领域。而且还将在更多领域得到广泛应用。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多