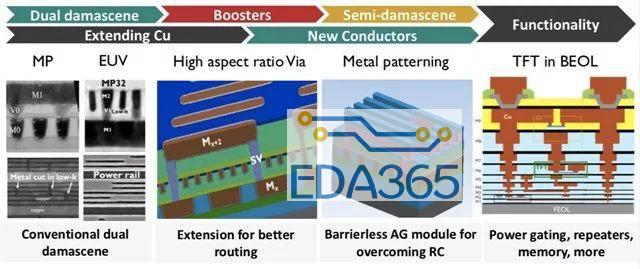

在上次的IEDM的一个星期天的短课程中,imec的Chris Wilson展示了适用于3nm节点以下的新型互连技术。

节点向前推进需要DTCO和微缩助推器,如自对准隔断(SAB,self-aligned block)、完全自对准通孔(FSAV, fully self-aligned via)、supervia和埋入式电力轨道(BPR)。Chris回顾了大部分上述微缩助推器的工艺精髓,但是我不会在这里重复所有的细节内容,况且我也不是一个工艺专家。

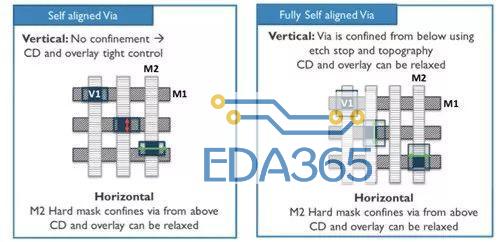

但这里有一个关于完全自对准通孔(FSAV, fully self-aligned via)的例子。完全自对准的意思是,通孔是同时被下面的互连层和上面的互连层所限制的,就像下图所示,所以通孔金属材料正好处在连接两个互连层所需要的位置。

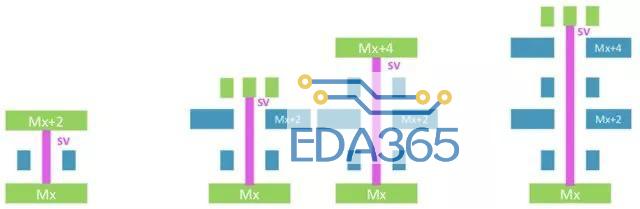

Supervia是另一种对设计极有意义的技术。第一代supervia可以从Mx连接到Mx+2(通常的via从Mx连接到Mx+1),这在SRAM中非常有用。第二代supervia可以从Mx连接到Mx+3或Mx+4,适用于埋入式电力轨道。然后第三代supervia从Mx直接连到Mx+5,允许它直接跳到低阻互连层。

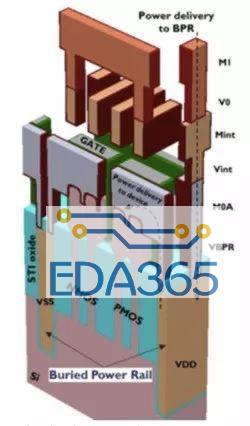

埋入式电源轨使采用单鳍器件或纳米片器件的标准单元从6-track可以微缩到5-track,因此在节距不微缩的情况下减少17%的单元面积。由于电源轨现在位于整个堆叠的底部,因此,supervia有助于将电源线连接到更高的互连水平,从而可以向芯片上的单元供电,如图所示。

使用钌(ruthenium)作为导电材料以及高深宽比的BPR可以达到50Ω/ um的电性指标。

铜制程的延伸

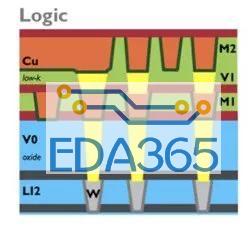

铜的一个很大问题是它需要一个阻挡层/衬垫层,否则铜会迁移到周围的氧化物中。但是,工艺上很难像微缩互连线本身那样微缩阻挡层和衬垫层,这意味着随着互连线的微缩,铜的占比会越来越小。而且在电流从上层通孔流向下层互连线的路径上,每个通孔的底部同样拥有这样一个不可微缩的阻挡层/衬垫层。当互连微缩达到16nm半节距及以下时,我们就需要低于2nm厚度的阻挡层/衬垫层。也许我们可以采用钌这个材料来制作2nm厚度的阻挡层/衬垫,但是在 1nm的厚度时,我们目前没有可选的材料。

混合金属化方案(钴,图像中的黄色部分,无阻挡层)使铜填充更容易,并且通孔底部没有阻挡层。

超越铜制程

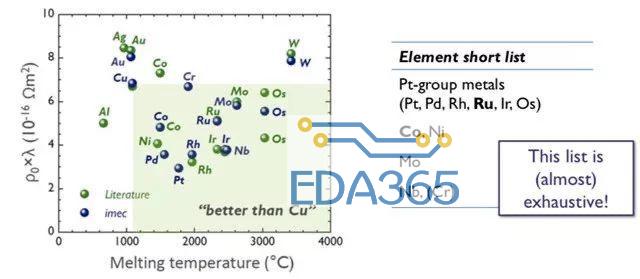

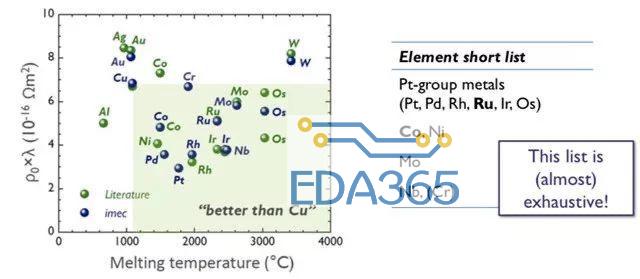

这张图表显示了所有“优于铜”的金属,因为它们的熔点更高,电阻率更低。我们想要更高的熔点,因为这有利于电迁移。

这里只有几个不错的金属材料选项。最具吸引力的金属是钴(Co)和钌(Ru)。对于具有相同沟槽横截面的无阻挡层Ru,其在16nm线宽处的性能优于Cu。对于无阻挡层的Co,其在12nm线宽以下的性能优于Cu。

钴制程的一个大挑战是CMP工艺,因为沟槽中的金属电化腐蚀,因此清洗后需要更换不同的碱洗工艺。CMP工艺对于钌制程也是一个挑战,它的大量运用取决于特征尺寸的最终选择。钌对氧化物的附着强度也存在挑战。但是imec已经制造出通过10年寿命指标的TDDB(经时介电层击穿)和电迁移测试的21nm节距钌金属线。

另一种方法是放弃双大马士革铜制程,转而采用金属蚀刻(铜制程之前的互连技术)。这对电阻率有好处,而且也适用于钌。而且由于晶界散射较少,该工艺具有电阻率优势。这可以使金属节距达到14nm的临界尺寸,并且退火还可以调节电阻。

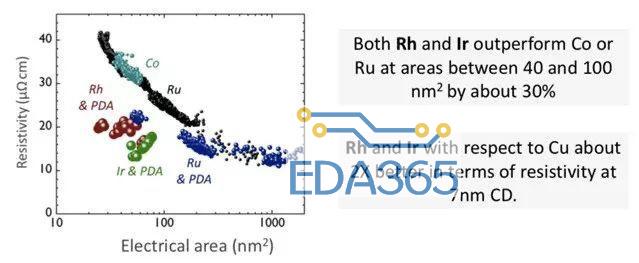

铑(Rh)和铱(Ir)的线电阻率优于钌和钴。还有一些复杂的化合物,它们表现出优异的性能,可能被用来解决电阻增加的问题。

总结

Chris的总结:

BEOL需要微缩助推器和DTCO来增强工艺能力以实现器件架构。

通过预填充(使用Co或Ru)可为替代金属提供垫脚石。

但是互连将需要诸如Co或Ru之类的替代金属。

钌金属的大马士革制程在21nm的节距下是可行的,并且通过了所有的可靠性指标,但在16nm节距上面临微缩极限。

钌的金属蚀刻工艺可以为16nm节距以下的互连提供20-30%的RC优势。

有一系列材料可以帮助对抗电阻的上升。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多