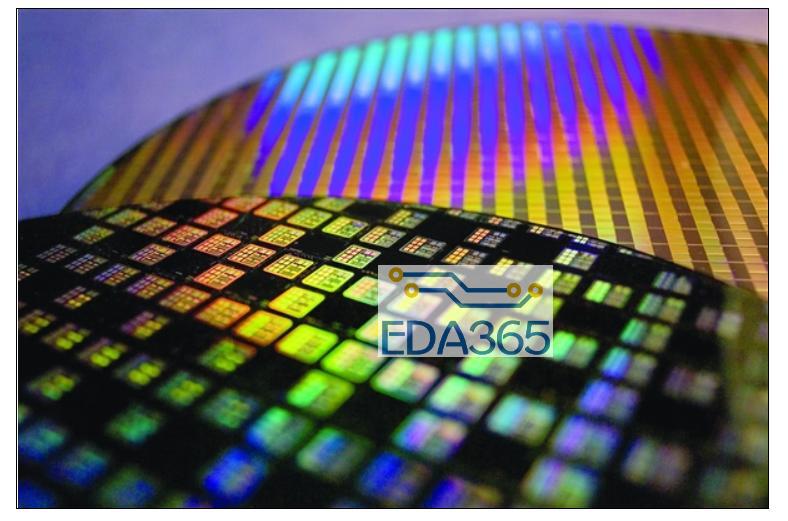

在芯片的大部分历史中,硅一直是其主要组成部分。这在很大程度上是因为硅拥有1.1电子伏特(eV)的“Goldilocks”带隙,这使得硅可以在低电压下运转集成电路,减少电流泄漏。

硅的另一个主要特征是,它可以用于制造氧化硅形式的实用“天然”绝缘体。在高介电薄膜十年前接管绝缘体这一工作之前,氧化硅一直成功用作多代芯片硅电路的绝缘体,分离组件并减少栅漏电流。

目前,斯坦福大学和SLAC国家加速器实验室的研究人员发现,一些最受欢迎的高介电质材料——即硒化铪(HfSe2)和硒化锆(ZrSe2)——在他们薄到二维(2D)材料时,都拥有与硅相同的完美带隙。因此,斯坦福大学的研究人员发现,便携硅/二氧化硅组合的二维材料版实现了世代的芯片设计。但在这种情况下,这种组合会缩小十倍。

Science Advances杂志的研究表明,斯坦福大学的科学家们发现,当知名优良的高介电薄膜HfSe2和ZrSe2被减薄到一个大约三个原子厚的单层时,它们会保持一个约1电子伏特的中等带隙。这与硅和其他“基极”3D半导体形成鲜明对比,当这些半导体被减薄到约5纳米以下时,它们的载流子迁移率开始降低,带隙开始增加。

“我们制造了几个装置(晶体管)”,斯坦福大学副教授兼研究合著者Eric Pop在IEEE Spectrum电子邮件采访中说,“高介电薄膜作为栅极绝缘层和保护层防止陷阱和缺陷。换句话说,‘原生’高介电薄膜为晶体管操作提供了改进的半导体界面。”

典型的金属氧化物半导体场效应晶体管(MOSFET)组成了大多数现代集成电路的基本构建块。MOSFET由栅极,源极和漏极组成。基本上,MOSFET是一个开关,来自栅极的电压导通或关闭源极和漏极之间的电流。

长期以来,MOSFET的设计包括在半导体的表面上放置绝缘层,然后将金属栅极放置在半导体顶部。当晶体管接通时,薄的绝缘层将晶体管的栅极与电流流过的沟道进行电隔离。硅用作半导体,氧化硅用作绝缘体。但随着芯片尺寸的不断缩小,不得不将硅氧化物制作的很薄,所以它不再是有效的绝缘体,就在这时,行业便将目光投向高介电薄膜。

“K”表示介电常数,指的是材料集中电场的能力。当绝缘体的介电常数更高时,它可以为相同厚度的绝缘体提供两个导电板之间增加的电流容量——存储更多的电荷。

随着芯片不断缩小,虽然高介电薄膜有助于克服绝缘体问题,但这些材料并非硅的“原生”材料(只有二氧化硅才是)。因此,为了处理每种材料原子结构之间的失配,在沉积之前仍然需要另一个“缓冲层”(如二氧化硅)。

Pop说:“在获得原生高介电薄膜之前,特别是与2D材料相结合的,我们可以设计极薄的(纳米)晶体管,这种晶体管也可以制造得非常短(就栅极长度而言)。高介电薄膜还可以确保,对于这种晶体管而言,低电压操作是毫无问题的。我们估计,使用这些2D材料的最短晶体管可能比使用硅,甚至是硅和高介电质材料的要小十倍。”

根据Pop的说法,为了让这种方法真正成为商业解决方案,HfSe2和ZrSe2薄膜需要达到大面积晶圆的规模,拥有均匀的厚度和结晶度。此外,需要更好地控制氧化步骤(或任何其他氧化物沉积),确保良好的均匀性,高质量绝缘的高介电薄膜。

Pop补充说:“最后,我们需要改进这种晶体管的电触点。这是不足为奇的,因为对于任何超薄材料(包括其他2D材料或非常薄的硅)而言,制作高质量的电触点是极具挑战性的。”

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多