类似的文章网上很多了,大都以软件分析为主,从U-boot到kernel。很多文章的分析也是非常详细以及精辟的。在这里,不想多说软件的机制,那样的机会留给大家吧。

记得07-08年一次去华为面试,主考官问了一些nand flash的操作的事宜,也算还好,没有太多刁难。面试结果还是没有被录取,这里有很多因素,有自己的,也有对方的。记得在面试的时候考官问了一个问题,flash的读写。还很详细的指了nand的操作。后来快面试结束的时候我问了考官一个问题:软件可以通过读写控制寄存器,或是把命令执行在data-bus上来模拟控制命令(理论上可以执行)。但是在还没有任何初始化外设(SDRAM,DRAM,RAM)的情况下,哪里的代码可以操作nand flash这样的设备。应为这样的设备,是要使用命令来控制flash的行为的。这样的状态也就是上电那一刹那,到mpu的第一条指令的开始地方,是如何过渡的。(注意:nand,cf-card,usb-storage不是唯一的掉电非易失的存储元器件,还有arm-xxx片内的rom和ram)

带着这样的问题看了很多资料,不乏芯片手册等等。现在在omap的板子上终于找到答案来验证自己的想法。所以想把它写下来。

话说这样的rom很不被人们重视,在开发过程中往往考虑两种因素:成本,开发周期。

成本显而易见,64M的换32M的,32M的换16M的,比起flash的操作,这里还是比较佩服broadcom的工程师居然可以把image控制在2M之内。

开发周期更显而易见,sdk包,解决方案全部采用ralink的。Demo板拿来直接调试就好了。很少有人会去关注上电之初flash的操作。那么,为什么没有一个完整的文档说明完成硬件拷贝的过程呢?我也不知道。

看了mpc860的用户手册,上面提及了一个概念HC。(HARDWARE COPY)。这样的HC是硬件完成的,那么硬件的逻辑是否就是和软件一样呢?再去看看了fpga的设计丛书,答案完全可以。硬件完全可以模拟软件的指令。这里有所不同的是软件是开发人员,要求cpu这么去做的。但是硬件是什么角色?这个角色可以这样认为:在软件无法涉及的领域,代替了部分软件(开发人员的逻辑)。这样的逻辑往往是单一,简洁的。说了半天,开始分析启动过程。

第一:概念

Rom ram sdram flash这些概念大家都不陌生了。也不解释相关的电器特性。只要知道相关操作特性:

ram可以通过地址直接访问。读写像sdram,掉电易失。直接经过行列地址译码。找到存储单元。并且把存储单元中的内容返回在数据线上。地址和数据线可以复用。

但是flash这样的设备,不是这样,特别是spi和nand类型的。直接给出的地址无法作用到数据线上。想要得到设备上的具体数据必须通过命令的形式来完成:read + 操作的设备地址;write + 操作设备的地址。数据线用于传输数据,指令线用于传输数据。复用的地址线通过锁存来表示读或者是写操作。

注意:这些设备的数据线和指令线是否复用,要看具体的datasheet。

第二:原因

CPU的行为只有两种:1取指令 2运算。那么保证在某一时刻cpu取得指令是正确的,这就是最重要的事情。保证在32位并行访问时候得到的数据是正确的,并且这上电之初在设备(可以进行直接地址访问)中的数据就是boot的代码。

第三:解决

如果CPU在上电之初可以访问片内的ram。并且ram中的内容就是存储boot的代码的设备中一部分内容。这样cpu就可以顺利的执行指令了。

那么是什么把flash的内容拷贝到片内的ram上呢?这就使上面提及的硬件代替了部分软件的逻辑。这样的逻辑往往是简单的。就是从flash上拷贝。拷贝到哪里?片内的ram。

在omap的芯片上片内的ram位于 0x40200000 ~ 0x4020ffff。Flash位于(GPMC)总线的接口上。在u-boot下使用简单的命令来比较一下flash中第一个page中的二进制内容,和ram中的内容,是否一样。

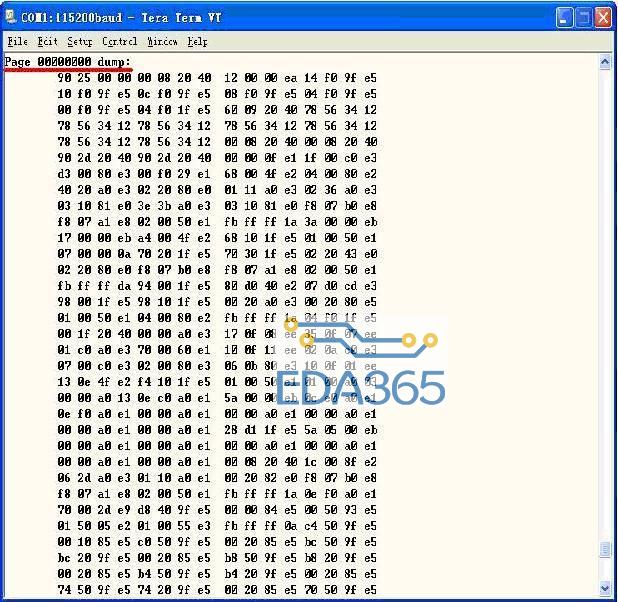

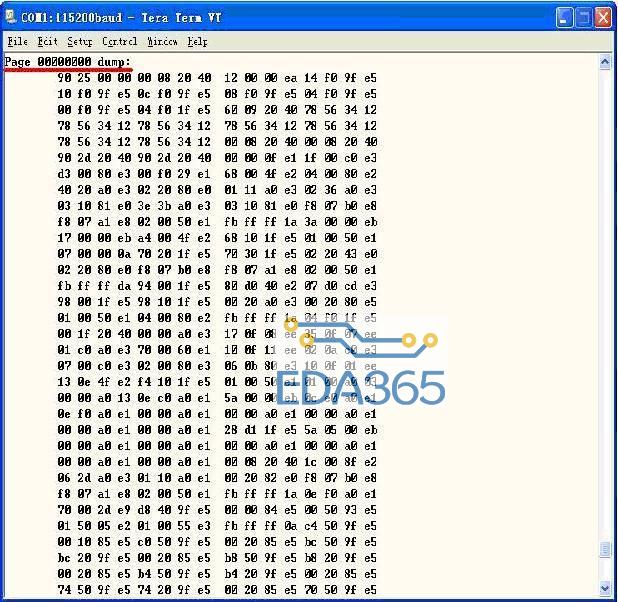

图 1 中显示的nand dump命令下page 0 offset 0的内容

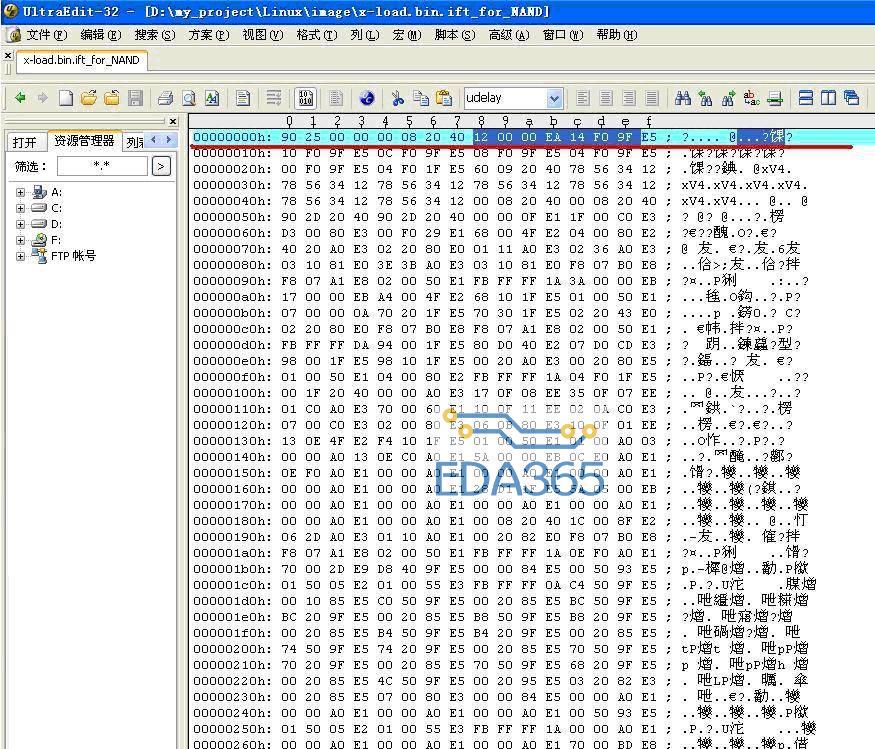

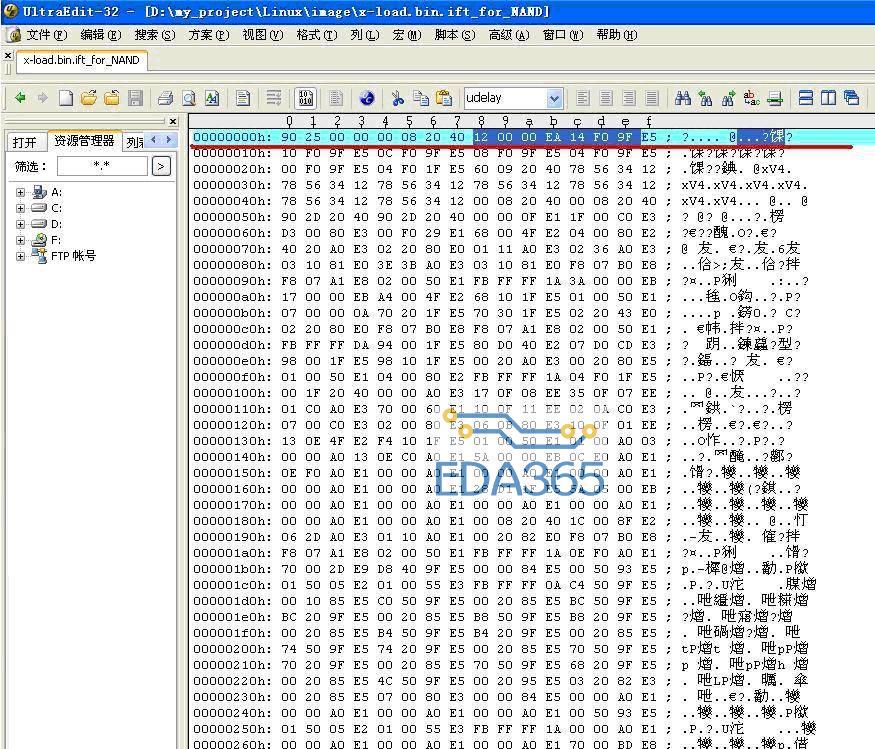

图 2 中显示的是x-load用UE打开始显示的二进制内容

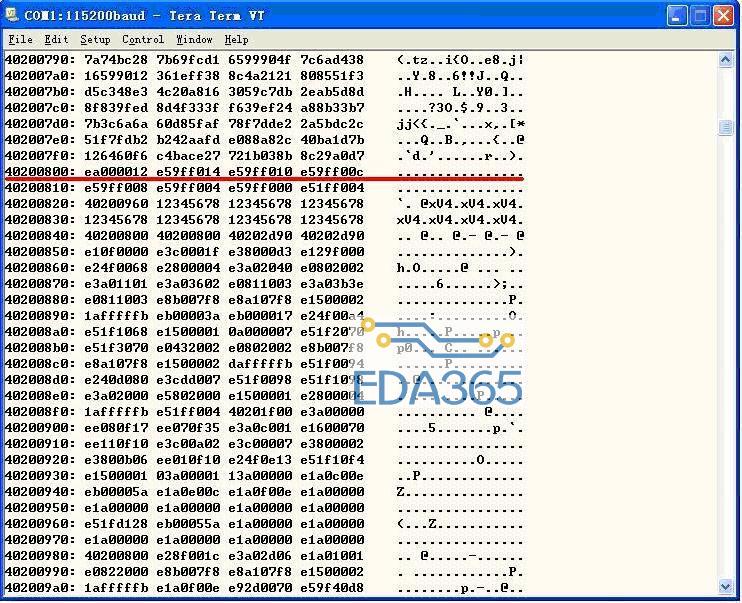

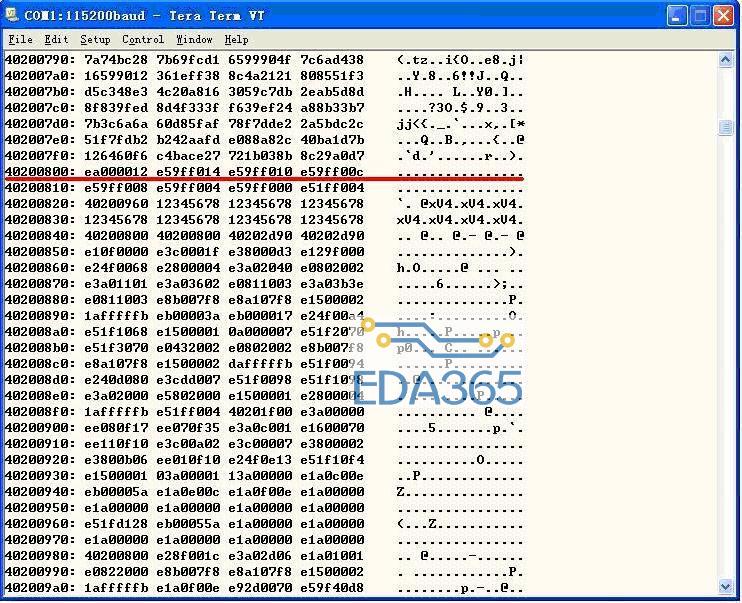

图3 中显示的是片内的ram中偏移量为0x800地址开始的内容

如上三图所示flash,ram中的内容是相同的。和ram中的内容作比较出了字节序不一样,其实内容都一样。那么为什么在偏移量的0x800的内容开始时一样的?这就是CPU上电以后的第一条指令了。要求在这个位置。这个位置和外设电路的(boot电路)安排相关。这个启动地址可以选择,但是开关的行为由外设电路决定。具体开发板要看具体的datasheet。软件上也可以控制,在编译的最后阶段,有连接脚本中指出偏移量。再有ld解析后组装成可以运行的image。

这样一来就可以看出来,上电后,并不是boot代码在运行。而是有其他的机制保证了代码出现在有效地上。而后CPU到事先按排好的地址去取指并执行。这就使所谓的HC,硬件拷贝。在artmel系列的开发板上还有称之为“step stone”的概念。就是存放flash里面前4k的代码的ram。具体的记不太清楚了,曾经有一次遇到过32M的flash。往往在较大容量的flash上,前面的4k或是64k的访问方式上存在区别。有的遵循CFI标准,有的则是JEDC的标准。看芯片的设计而定。不光是软件的设计按照这些标准,硬件的逻辑设计也要满足这样的标志。

其实上电指出还有cpu的clock也是很重要的因素。有机会再聊聊这个clock和PLL。

关键字:arm 上电 第一条指令

热门文章

更多

热门文章

更多