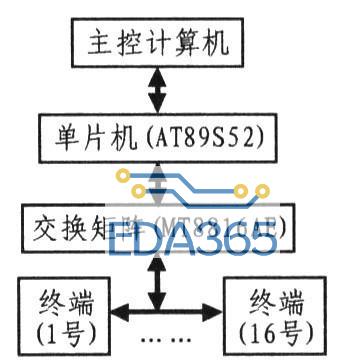

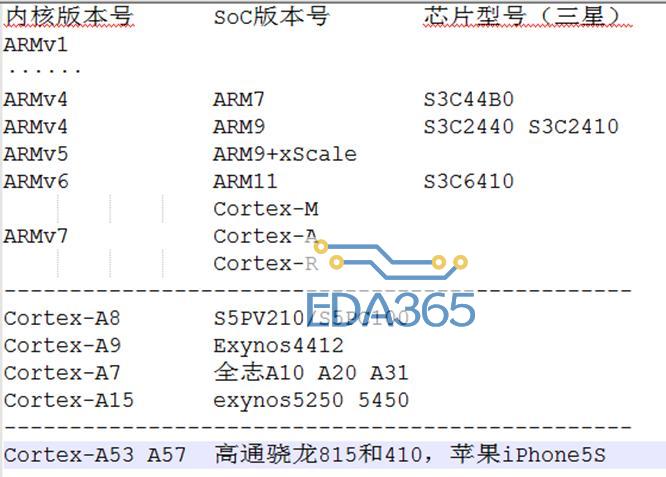

1.cpu与soc

内核版本号与soc版本号由arm公司确定。

芯片型号由各半导体公司确定。

soc包括cpu与一些基本内设。(一般提到CPU都指的是soc,实际上cpu只是soc的一部分)。

RISC与CISC

RISC复杂指令集:指令繁多,但是效率高。Intel等桌面pc使用这种指令集。功耗大。

CISC精简指令集: 指令少,但是效率略低。优点是功耗低适合嵌入式设备。

统一编址&独立编址

内存通过CPU的地址总线来寻址定位,然后通过CPU数据总线来读写。CPU的地址总线的位数是CPU设计时确定的,因此一款CPU所能寻址的范围是一定的,而内存是需要占用CPU的寻址空间的。内存与CPU的这种总线式连接方式是一种直接连接,优点是效率高访问快,缺点是资源有限,扩展性差。

CPU访问各种外设有2种方式:一种是类似于访问内存的方式,即把外设的寄存器当作一个内存地址来读写,从而以访问内存相同的方式来操作外设,叫IO与内存统一编址方式;另一种是使用专用的CPU指令来访问某种特定外设,叫IO与内存独立编址。

由于内存访问频率高,因此采用总线式连接,直接地址访问,效率最高。

IO与内存统一编址方式,优势是IO当作内存来访问,编程简单;缺点是IO也需要占用一定的CPU地址空间,而CPU的地址空间是有限资源。

IO与内存独立编织方式,优势是 不占用CPU地址空间,缺点是CPU设计变复杂了

哈佛结构&冯诺依曼结构

程序和数据都放在内存中,且不彼此分离的结构称为冯诺依曼结构。譬如Intel的CPU均采用冯诺依曼结构。

程序和数据分开独立放在不同的内存块中,彼此完全分离的结构称为哈佛结构。譬如大部分的单片机(MCS51、ARM9等)均采用哈佛结构。

冯诺依曼结构中程序和数据不区分的放在一起,因此安全和稳定性是个问题,好处是处理起来简单。

哈佛结构中程序(一般放在ROM、flash中)和数据(一般放在RAM中)独立分开存放,因此好处是安全和稳定性高,缺点是软件处理复杂一些(需要统一规划链接地址等)

ARM体系总结

常用ARM汇编指令只有二三十条

ARM是低功耗CPU

ARM的架构非常适合单片机、嵌入式,尤其是物联网领域;而服务器等高性能领域目前主导还是Intel

大部分ARM(M3 M4 M7 M0 ARM9 ARM11 A8 A9等)都是32位架构

32位ARM CPU支持的内存少于4G,通过CPU地址总线来访问

SoC中的各种内部外设通过各自的SFR编程访问,这些SFR的访问方式类似于访问普通内存,这叫IO与内存统一编址。

常见ARM(除ARM7外)都是哈佛结构的

哈佛结构保证了ARM CPU运行的稳定性和安全性,因此ARM适用于嵌入式领域

哈佛结构也决定了ARM裸机程序(使用实地址即物理地址)的链接比较麻烦,必须使用复杂的链接脚本告知链接器如何组织程序;对于OS之上的应用(工作在虚拟地址之中)则不需考虑这么多

CPU和外部存储器的接口

内存 内部存储器 用来运行程序的 RAM 举例(DRAM SRAM DDR)

外存 外部存储器 用来存储东西的 ROM 举例(硬盘 Flash(Nand iNand···· U盘、SSD) 光盘)

CPU连接内存和外存的连接方式不同。内存需要直接地址访问,所以是通过地址总线&数据总线的总线式访问方式连接的(好处是直接访问,随机访问;坏处是占用CPU的地址空间,大小受限);外存是通过CPU的外存接口来连接的(好处是不占用CPU的地址空间,坏处是访问速度没有总线式快,访问时序较复杂)

SoC常用外存:

NorFlash 总线式访问,接到SROM bank,优点是可以直接总线访问,一般用来启动。 //小容量

NandFlash: 分为SLC和MLC //

eMMC/iNand/moviNand eMMC(embeded MMC) iNand是SanDisk公司出产的eMMC,moviNand是三星公司出产的eMMC //手机内部

oneNAND oneNand是三星公司出的一种Nand

SD卡/TF卡/MMC卡

eSSD

SATA硬盘(机械式访问、磁存储原理、SATA是接口)

外部总线接口(EBI)被用作S5PV210外围。它依赖于内存控制器释放 外部请求外部总线空闲内存控制器时,因为它没有当内存的知识 访问将开始或完成。它使一个SROM控制器、一个OneNAND控制器和一个快闪记忆体 控制器、分享外部内存总线、内存端口0。

启动过程详解

内存:

SRAM 静态内存 特点就是容量小、价格高,优点是不需要软件初始化直接上电就能用

DRAM 动态内存 特点就是容量大、价格低,缺点就是上电后不能直接使用,需要软件初始化后才可以使用。

单片机中:内存需求量小,而且希望开发尽量简单,适合全部用SRAM

嵌入式系统:内存需求量大,而且没有NorFlash等可启动介质

PC机: 内存需求量大,而且软件复杂,不在乎DRAM的初始化开销,适合全部用DRAM

外存:

NorFlash:特点是容量小,价格高,优点是可以和CPU直接总线式相连,CPU上电后可以直接读取,所以一般用作启动介质。

NandFlash(跟硬盘一样):特点是容量大,价格低,缺点是不能总线式访问,也就是说不能上电CPU直接读取,需要CPU先运行一些初始化软件,然后通过时序接口读写。

所以一般PC机都是:很小容量的BIOS(NorFlash)+ 很大容量的硬盘(类似于NandFlash)+ 大容量的DRAM

一般的单片机: 很小容量的NorFlash + 很小容量的SRAM

嵌入式系统:因为NorFlash很贵,随意现在很多嵌入式系统倾向于不用NorFlash,

直接用:外接的大容量Nand + 外接大容量DRAM + SoC内置SRAM

S5PV210使用的启动方式是:外接的大容量Nand + 外接大容量DRAM + SoC内置SRAM

实际上210的启动还要更好玩一些,210内置了一块96KB大小的SRAM(叫iRAM),同时还有一块内置的64KB大小的NorFlash(叫iROM)。210的启动过程大致是:

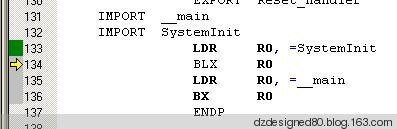

第一步:CPU上电后先从内部IROM中读取预先设置的代码(BL0),执行。这一段IROM代码首先做了一些基本的初始化(CPU时钟、关看门狗···)(这一段IROM代码是三星出厂前设置的,三星也不知道我们板子上将来接的是什么样的DRAM,因此这一段IROM是不能负责初始化外接的DRAM的,因此这一段代码只能初始化SoC内部的东西);然后这一段代码会判断我们选择的启动模式(我们通过硬件跳线可以更改板子的启动模式),然后从相应的外部存储器去读取第一部分启动代码(BL1,大小为16KB)到内部SRAM。

第二步:从IRAM去运行刚上一步读取来的BL1(16KB),然后执行。BL1负责初始化NandFlash,然后将BL2读取到IRAM(剩余的80KB)然后运行

第三步:从IRAM运行BL2,BL2初始化DRAM,然后将OS读取到DRAM中,然后启动OS,启动过程结束。

思路:因为启动代码的大小是不定的,有些公司可能96kb就够了,有些公司可能1MB都不够。所以刚才说的2步的启动方式不合适。三星的解决方案是:把启动代码分为2半(BL1和BL2),这两部分协同工作来完成启动。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多