Open-Silicon采用微捷码的SiliconSmart ACE进行标准单元和I/O单元特征化与建模,最大程度提高先进节点设计的性能,加速电路引擎(ACE)通过实现特征化流程的全面自动化,提供了数量级吞吐量改善

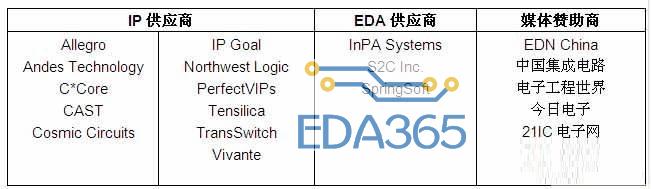

美国加州圣荷塞 2011年8月25日– 芯片设计解决方案供应商微捷码(Magma®)设计自动化有限公司(纳斯达克代码:LAVA)日前宣布,Open-Silicon公司采用SiliconSmart ACE作为标准单元和I/O单元特征化与建模标准工具。作为SiliconSmart的长期用户,Open Silicon升级用了SiliconSmart ACE,充分利用了该工具公认快速精确的多个工艺、电压和温度(PVT)角点库特征化的能力,这将让他们能够对采用先进工艺的设计最大程度地降低功耗并提高性能。Open-Silicon使用SiliconSmart ACE对他们专利技术CoreMAX™特定设计库增强流程中新单元进行特征化并用于Open-Silicon的VanMAX™反馈偏压库单元的再特征化。

“我们多年来一直在使用SiliconSmart,并受益良多,” Open-Silicon公司工程经理Shrikrishna Mehetre 表示。“随着我们向更先进工艺技术发展,哪怕提取每微微秒的性能,都需要多个PVT角点的快速精确特征化。拥有了SiliconSmart ACE的卓越功能和微捷码持续的世界级支持,我们对使用SiliconSmart ACE进行下一代设计充满信心。

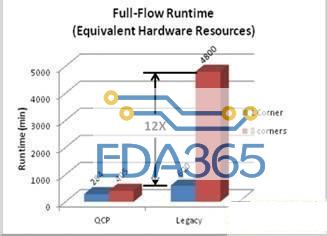

“拥有更高的精度、更快的速度和更好的易用性,SiliconSmart ACE较其它解决方案提供了数量级的吞吐量提升,”微捷码定制设计业务部总经理Anirudh Devgan表示。“公认的显著缩短时间和减少工作量的能力让SiliconSmart ACE成为了特征化与建模领域真正领导者。”

SiliconSmart ACE:数量级吞吐量改善

具有业界领先的精度、吞吐量和易用性,SiliconSmart ACE提供了适用于所有主流设计流程的标准单元、I/O、定制宏和存储器特征化与建模,支持所有先进时序、功耗、噪声和统计建模规格。其专有的加速电路引擎(Accelerated Circuit Engine,ACE)全面自动化了特征化流程、部署了最先进电路功能识别技术及矢量生成和优化算法,可在无损精度的前提下有效完成单元特征化。为获得最高性能,SiliconSmart ACE还嵌入了微捷码精确且超快速的SPICE仿真器——FineSim™ SPICE,实现了数量级的吞吐量提升。此外,它还包括了一个闭环模型验证流程,让用户能够无缝地在微捷码系统内启动第三方工具来验证所生成的模型。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多