摘要:本文介绍了几种65纳米以下芯片内分区的平面布局技术。这些技术可帮助我们在相对短时间里完成切实可行的平面布局,包括:分析逻辑连接、找出拥塞的根本原因以及控制局部密度。同时,我们还将分享有关zigzag缓冲区的技巧,这些缓冲区往往带来额外的时序和布线问题。本文中,我们会一一为您呈现‘如何通过微捷码Tcl界面来实施这些技术’的实例。

关键词索引:平面布局、逻辑锥体、拥塞、局部密度、Zigzag缓冲区

第I章:引言

随着芯片设计发展至65纳米及65纳米以下,对于设计师来说按时完成设计变得更加困难重重、更具挑战性。一方面,我们需采取额外步骤减少功耗问题(特别是在65纳米以下的漏电功耗),如:预置功率门控以及预定义多电压域;所有这些都需耗费额外面积,需在设计中早早进行规划。另一方面,对设计的要求提高了,包含的功能更多、性能更高,而这通常意味着更多的RAM、特殊IP和预布局信号。此外,用于寻找最适合特定设计的平面布局的时间极为有限。本文介绍了几种方法,可帮助设计师发现平面布局阶段关键问题,想出质量相当好、速度相对快的解决方案。介绍每种方法后,我们都将以实例进行说明。

第II章:分析平面布局的逻辑连接

逻辑连接情况的掌握对平面布局来说非常重要。通过这类信息,我们能够知道逻辑组是如何相互连接以及今后它们所在的相对位置。

通常情况下,我们是从前端人员处获得初始平面布局信息。他们手中有关逻辑组连接的信息大多类似于数据流。但随着设计规模的日益扩大,这类信息的实现变得更为困难。完成全芯片综合后,前端模块难以被映射到后端物理域中。它只能给你提供一个大体方向,但难以完全指望它来完成平面布局。为了获得更好的平面布局,我们必须对物理域中逻辑连接进行分析。

对平面布局有影响的逻辑连接一般有下列几种:第一种是RAM与标准单元间连接;第二种是标准单元与标准单元间连接;第三种是模拟宏;第四种是分区引脚连接。由于模拟宏位置和引脚连接有可能在设计初期阶段就事先确定,因此前两种逻辑连接才是我们要关注的重点,设计师对这两种逻辑连接拥有最大的控制自由。

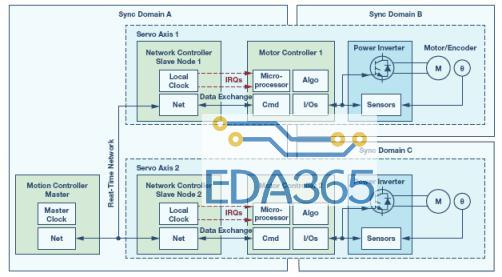

分析逻辑组的逻辑锥体(logic cone)就是一种有效的逻辑连接分析方法。逻辑锥体会显示出往返特定节点的所有连接,在计算逻辑组内连接时它可起到很好作用。微捷码提供了一个有效命令,可显示出一个节点的逻辑锥体——“Query node subgraph”。这个命令的输出就是一张节点逻辑锥体中所有单元/引脚列表。您也可采用此命令的选项来指定来回或通过一个节点的逻辑锥体。但此命令只能处理一个节点且不能输出可视化信息。要想改变这种状况,我们可使用微捷码的TCL界面来实施它。这样做旨在依次通过逻辑组每个节点,分化逻辑锥体列表,强调GUI内的这些网络和单元。通过这种方式,逻辑组的所有逻辑锥体均可在GUI内显示出来,为我们提供了有关逻辑组内连接的可视化信息。图1显示了一个RAM的逻辑锥体:浅蓝色部分显示的是RAM的逻辑锥体的开始节点和结束节点;深蓝色部分显示的是其它单元。从图片上,我们可以知道有一些逻辑组可将RAM拖到左边。因此我们能够通过将这个RAM移到左边来调整平面布局。

图1:一个RAM的逻辑锥体

有时,一层的逻辑锥体并不能为我们提供清晰的平面布局图。我们必须强调多层的逻辑锥体。图2显示了一例来自RAM的3层逻辑锥体。蓝色部分显示的是第1层,粉色部分显示的是第2层,黄色部分显示的是第3层。这个RAM在顶部拥有与所有RAM的连接,在右边也有一些到逻辑组的连接。我们可以向上移动RAM。

图2:一个RAM的3层逻辑锥体

上述的两个例子向我们展示了,如何通过分析逻辑组的逻辑连接来获得信息,进而对平面布局进行调整。由Tcl脚本所产生的可视化信息易于为设计师所阐释和使用。[page]

第III章:分析平面布局的拥塞情况

平面布局阶段面临的另一个问题是如何减少或去除拥塞。我们必须在进行平面布局调整前找出拥塞的根本原因。我们通常的做法是找出对拥塞贡献最大的连线。如果我们解决了这些问题,那么拥塞情况将会有很大改善。

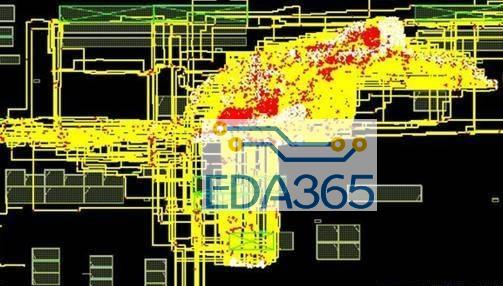

为了实现这一目标,我们开发了一个脚本。脚本是选择通过一个横截面的所有连线。如果该区域存在水平拥塞,那么这就一个垂直截面;如果该横截面存在垂直拥塞,那么这就是一个水平截面。我们可使用下述微捷码命令来逮住这些连线:data list “model_box –window {$x0 $y0 $width $hight} –layer_type segment –no_pin_boxes” $m。该命令会选定窗口中所有连线。我们可将窗口设定为横截面的形状。从下方例子中,我们能够看出这一点。图3显示了横截面,而图4显示了通过横截面的所有连线。

图3:横截面

图4:通过横截面的所有网络[page]

在知道通过横截面的所有连线后,我们就可找出这些连线横跨拥塞区域的原因所在。我们可使用在第II 章中介绍的方式来对这些连线的逻辑锥体进行分析。这就为我们提供了‘有哪个逻辑组通过这些连线连接到拥塞区域中’的相关信息。通过这类信息,我们能够有选择地调整平面布局,降低局部密度,或将非关键时序路径从拥塞区域移出,或最大可能完成上述所有这些任务。

局部密度控制我们将在第IV章讨论到。在这章中,我们主要讨论如何将非关键连线移出拥塞区域。这项技术类似于将试验性布线结果返回到平面布局中,其要旨是让这些非关键时序路径避开拥塞区域:首先,我们可使用“query node slack”来找出所有非关键时序路径;接着,我们可对其相关逻辑单元的组和区域添加控制,强制它们离开拥塞区域。完成这些步骤后,非关键时序路径将被从拥塞区域移开,从而释放出布线资源给其它连线。以下就是我们如何分析并解决拥塞问题的一个例子。

图5:标准单元面积上的拥塞情况

图6:连线导致拥塞

图5显示了一份平面布局的拥塞情况。我们要做的是,找出在红圈部分中什么连线导致了拥塞。在输出该区域中所有连线后,我们发现一组总线是造成该区域拥塞的最大祸首。图6显示了该总线的逻辑锥体。基于这一信息,我们缩小了底部的RAM以增宽标准单元的中央区域;同时我们也在一个逻辑组上设定了区域,将这一区域从拥塞区域移开。完成这2个步骤后,拥塞问题也就得以解决了。 [page]

第IV章:局部密度控制

有时完成初始布局后,我们必须降低标准单元区域的局部密度以解决布线或时序问题,通过减少迂回布线从而改善特定区域的布线资源并降低互连线延迟,特别在逻辑组拥有很强的内部连接时这项技术尤其有用。在这种情形下,平面布局工具会将单元放置的尽可能近,以满足时序要求并降低总线长。这可能造成其单元密度太高,从而导致布线问题。

在这章中,我们将讨论两种局部密度控制方式。一种是微捷码为我们提供的局部密度控制方式,使用带有阻挡百分比的标准单元布局阻挡(placement blockage)方式。我们可在拥塞区域添加这类布局阻挡功能并设定阻挡百分比。阻挡百分比可确定在这种阻挡范围内可设置多少个标准单元。如果我们设定的百分比低于平均密度,那么平面布局工具将会扩散所有标准单元。下方就是采用这种方式的一个例子。

图7:带有阻挡百分比的布局阻挡

图8:布局的结果

图7显示了带有阻挡百分比的布局阻挡,而图8显示了布局的结果。首先,我们必须选择一个适合的阻挡百分比,而这并不容易做到。出于多方面考虑,我们必须几次尝试才可获得适合的百分比,这会影响到设计师生产率。其次,密度在阻挡边缘会发生剧烈变化。这是个大问题,它会导致边缘出现新的拥塞情况。换句话来说,它可能将拥塞情况向周围扩散。这个结果并不符合我们的本意。[page]

为了解决这个问题,我们介绍了另一种方式。这种方式能够解决我们上面提到的问题。这种方式旨在让平面布局工具可在布局的同时发现拥塞并在拥塞区域插入更少标准单元。因此,我们可在拥塞区域添加布线阻挡并运行布局功能。具体例子如下 :

图9:无控制的布局结果

图10:添加布线阻挡后的布局结果

图9显示了无特殊控制的单元布局结果。而图10则显示了添加布线阻挡后的结果。相比微捷码的默认方式,边缘附近的密度很顺利地得到改变。然而,这种方法也要求多次迭代才可找出布线阻挡的最佳尺寸或密度。 [page]

第V章:Zigzag缓冲区技巧

随着设计中宏数量的增多,它通常会不断在布局中创建狭长通道,且那些通道有可能在布局中被阻挡。我们常在堆叠的macro附近发现Zigzag缓冲区。Zigzag缓冲区意味着一个缓冲区的输入输出方向发生了小角度的旋转,它会带来了总线长的增加,这对布线和时序来说都极为不利。基本上,它算是个设置得不好的缓冲区。我们不会想在我们的设计中看到它们。例如:

图11: Zigzag缓冲区

在图11中,红箭头显示了一个缓冲区的输入输出连线方向;绿箭头显示了输入/输出连线的飞线。两条绿线组成一个锐角。在这个例子中,缓冲区并未改善任何问题,反而带来了一些转换问题。有时,单使用工具是难以解决这个问题,而且反而增加了一条缓冲链。为解决这个问题,我们可开发脚本并有选择地在通道中设置一些缓冲区。

该脚本要旨是找出输入/输出连线的飞线间锐角。既然我们知道zigzag缓冲区、驱动单元和接收单元的坐标,那么我们就可使用类似下方的基本三角形计算方式来得出所要结论。同时,这3个点也组成一个三角形(图12)。根据三角函数,如果我们知道一个三角形的三边长,那么我们就能够算出这个三角形的每个角的角度为多少:公式为:Cosθ = (a² + b² – c²)/2ab; Θ = acos(cosθ)/π*180

图12:三角函数

如果Θ<90 度,我们可把其视为zigzag缓冲区。这可帮助设计师在布局后快速地识别Zigzag缓冲区,在进一步优化前正确设置好缓冲区。

总结:

尽管平面布局变得困难重重、极富挑战性,但好的设计分析总能使您的布局工作变得轻松些。在本文中,我们虽然分享了一些可达成这一目标的技术,但一份好的平面布局,其要求远不止这些。每份设计都有其独特问题存在,我们应充分利用Talus可编程界面,让任务的完成成为可能。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多