意法半导体(纽约证券交易所代码:STM)宣布,针对设计研发最先进的网络专用集成电路(ASIC)的32nm技术平台已正式上市。这款全新32nm系统级芯片设计平台采用意法半导体的32LPH(低功耗高性能)制程,是业内首款采用32nm体硅上实现串行器-解串行器(SerDes) IP。

实现晶圆面积大于200mm2的超大ASIC设计,意法半导体全新的32nm 32LPH ASIC设计平台可实现前所未有的高性能、高复杂性以及低功耗,同时降低每个功能模块的尺寸。该平台可加快针对企业交换机、路由器、服务器以及光交换机和无线基础设施等高性能应用的下一代网络ASIC芯片的研发速度。

意法半导体部门副总裁兼网络与存储产品部总经理Riccardo Ferrari表示:“随着32LPH设计平台的推出,意法半导体实现了下一代通信基础设施的应用概念,新一代通信基础设施需要高集成度ASIC芯片以满足不断提高的性能要求,同时达到降低功耗和提高硅片集成度的挑战性目标。客户对这个赢得重要设计的平台展现出浓厚的兴趣,使我们对平台的前景更充满信心。”

意法半导体SerDes IP模块S12是一款拥有知识产权的关键器件,并已向几家主要客户成功展示。S12 IP模块对于研发网络ASIC芯片有关键性的影响,在网络设备设计内实现芯片对芯片、芯片对模块以及模块对背板的通信。

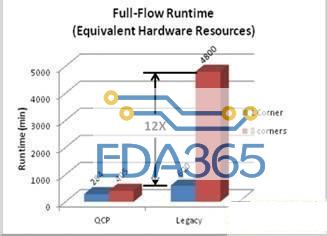

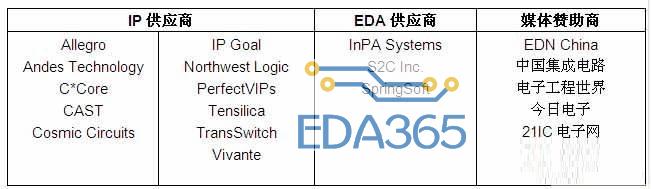

意法半导体技术研发部副总裁兼中央CAD与设计解决方案总经理Philippe Magarshack表示:“意法半导体率先在通信基础设施市场上推出采用32nm体硅制程技术的完整设计平台,包括下一代可预测ASIC的自上而下设计方法,以及一套经验证的IP,包括SerDes 和嵌入式DRAM,这些都是意法半导体在上一代技术制程的多年研发成果。32LPH平台需通过低功耗技术技术满足网络应用的高性能要求,同时拥有规模制造的成本效益,意法半导体法国Crolles技术研发中心对加快平台研发进度有很大贡献。此外,我们与EDA(电子设计自动化)厂商携手为网络设备厂商提供可预测的ASIC研发周期,包括快速虚拟物理层原型设计和32nm级时序、信号以及功率的一致性测试分析。”

采用意法半导体的 32LPH制程技术的首款ASIC原型预计于2011年初上市,并于2011年下半年开始量产。

详细技术信息

意法半导体针对网络应用的32LPH(低功耗高性能)设计平台可支持多达10个金属层,以提高芯片布线效率。该平台基于ISDA联盟框架协议内开发的 32nm 高K金属栅工艺,同时整合意法半导体独有的专用IP和单元,如密度达10-Mbit/mm2的嵌入式DRAM和三重内容寻址存储器 (TCAM)。

正常情况下,一个SerDes(串行器-解串行器)要在一颗ASIC单芯片内整合多次以上(通常达200次)。该模块可实现以下串行通信:

• 同一印刷电路板上的IC或ASIC之间的通信(芯片对芯片);

• 用于连接遥控设备的ASIC和光纤模块的通信 (芯片到模块);

• ASIC和物理层接口模块(芯片到模块);

• ASIC和系统背板——背板是设备内部装有各种系统板卡的物理机架。

S12 IP基于意法半导体经验证的SerDes架构,可扩展至8条 12.5-Gbit/s收发(Tx/Rx)通道。S12设计优化封装面积,可使用倒装片BGA封装。意法半导体将很快推出传输速度高达14-Gbit/s的 S14 IP。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多