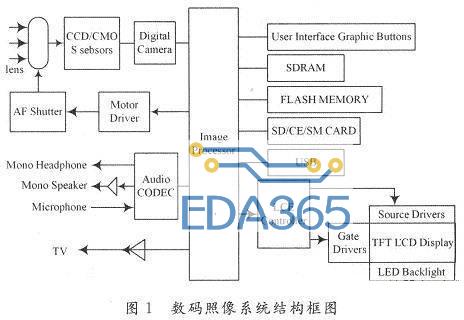

在软件开发领域,最关键但也是最无法预料的阶段是调试阶段。在软件调试的过程中有很多要素都举足轻重,而其中最重要的则是时间。设置和调试软件所需的时间对于软件的上市时间以及是否满足客户期望都有着巨大的影响,同时还影响着一个在市场取得成功的优秀产品的销售业绩。一个应用的集成必须经过一个由构建、加载、调试/调谐到更改等多个阶段构成的过程,如图1 所示。

图1:集成和调试周期。我们的目的是要将这一周期的次数以及在每个部分花费

嵌入式实时系统的调试既是一门艺术,又是一门科学。用于调试和集成这些系统的工具和技术对于在调试、集成和测试阶段上所需时间的长度有着重要影响。对运行中的系统越了解,我们就能越快发现并修正缺陷。

要了解系统有一个最传统也是最简单的方法,即在软件中的某些点添加消息,以便输出有关系统状态的信息。这些消息可以是输出到显示器的“打印”指令,也可以通过LED 或者LED 组闪烁的形式来系统状态和健康度。每个功能或任务都可以通过输出一个状态信息来开始指示是系统将之安排到程序中的某个点。如果系统在某个点出现故障,对于这一输出信息的诊断就可以帮助工程师了解到系统最后一次正常状态点的所在,从而确认问题所在。当然,这种方式会导致系统过载,进而影响系统性能。因此,工程师必须在测试完系统后清除这些数据并在销售之前对系统重新验证,或者将系统和系统中测得的代码一起销售。他们必须确保所工程师可以利用更先进的调试方法来减少集成和测试阶段的时间。其中一个方法就是利用“调试监视器(debug monitor)”。调试监视器是一种嵌入到目标应用或集成到微控制器或DSP 内核的相对较小的代码,通过一个串行接口和主机进行通信。调试监视器可以下载代码、读写DSP 存储器和计数器、设置简单和复杂的断点、单步执行程序并绘制源代码概图。

另一种名为ROM 仿真器(ROM emulator)的调试监视器则常被用于带有基于ROM的软件程序的系统中。ROM 仿真器是一个用来代替目标系统ROM 设备的插件。这一插件和主机相连(通过串行、并行、以太网等连接方式),让工程师可以缩短调试过程的周期时间。工程师不需要在每次软件迭代时都通过ROM 编程程序对ROM 设备进行重新编程,而是可以将这个代码下载到ROM 仿真器的快速RAM 上。

接着,系统就会以代码脱离ROM 设备运行的状态运行。

调试监视器和ROM 监视器对嵌入式系统调试阶段无疑能带来很大的益处,但是,随着嵌入式处理器变得越来越快,而且系统不断转向单片系统方案,处理器的透明度就形成了更大的挑战,要求更加尖端的调试方案。

集成和调试复杂的数码系统也需要简短而复杂的调试工具,如逻辑分析仪等。系统集成商可以通过逻辑分析仪来捕捉数字信号,并以位、字节和文字格式显示出来,还能分析以下设备的活动:

数字计数器

复杂状态机

缓冲器和FIFO

系统总线

另外,逻辑分析仪还可以分析FPGA、ASIC 和标准单元执行等其它片上系统功能。它不需要太大的学习曲线,但要求较高的初始投资(取决于对于它的能力的要求以及需要什么样的时钟率)。系统集成商可以在逻辑分析仪中采取触发机制,来将数据捕捉到大型缓冲器中。这种数据可以是预触发数据或后触发数据,也可以是二者的结合体。数据轨道可以被保存并打印出来,数据也可以通过各种不同方式进行过滤。

应用逻辑分析仪的一个主要缺点在于,它虽然可以用来进行软件调试,本身却是复杂的硬件调试工具。对逻辑分析仪的运用是否成功,取决于系统集成商对于硬件的了解程度,因为这一工具是基于硬件调试的,而且需要通过复杂的设置和配置才能获得正确的信息以进行调试。

逻辑分析仪的另一个缺点,则是信号的可见性。逻辑分析仪需要连接到DSP 设备的管脚上,才能深入了解系统,而这会受到DSP 管脚的类型的限制。随着DSP设备被越来越多地集成到片上系统中,设备内部的运行情况的可视性也不断减弱。

日益降低的可视性

1988 年,由于设计时间压力的增大,而且嵌入式设备上有了用于片上仿真的新空间,嵌入式系统行业经历了一场从传统的在线仿真到扫描式仿真的变革。目前业界普遍认为扫描式仿真(即JTAG)要好于更古老而且更昂贵的“在线仿真”(即ICE 技术)。

DSP 在调试上的问题

有数个源自业界的因素在不断改变着DSP 系统的开发:

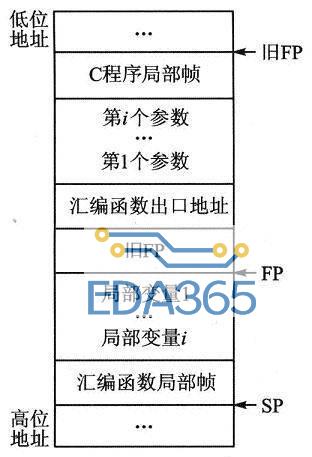

系统级集成;由于应用复杂性的增加和片上系统面积的缩小,系统元件的可视性也降低了。(图2)嵌入式系统总线会带来测量上的难题,而系统总线过宽则会导致系统带宽问题。在这些情况下要控制程序是很难的。

图2:系统级集成导致系统可视性降低

为了保持可视性,DSP 厂商采取了多项措施:

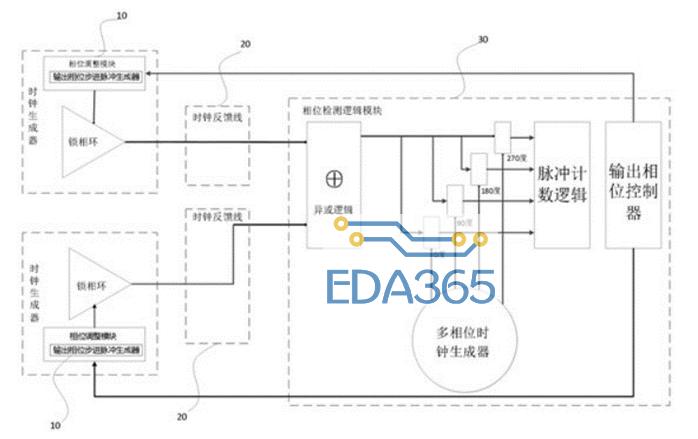

片上测量( On-chip instrumentation):由于系统集成度越来越高,工程师无法了解到设备的工作情况(图3)。工程师于是把总线监视逻辑分析仪功能加到片上逻辑中,比如,通过触发逻辑来他们想要了解的事件、整理线索并导出逻辑,以便可以浏览事件,并使DSP 内核上每个管脚输出的带宽都最大化。调试控制则是通过1 个仿真器来进行的,可以进行信息抽取。

图3 日益降低的可视性要求先进的片上调试逻辑

片外数据采集:一旦数据被从DSP 内核中导出,就必须被以适当的方式存储、处理、过滤并格式化,以使测试工程师能够准确地理解这些数据。

数据可视性:DSP 的集成能力包括能够很轻易以不同的配置浏览数据。图4 展示了整个关系链。其中逻辑分析仪的功能已经被集成到片上,控制和测量数据采集主要通过仿真控制器来进行,而数据则显示在主机上的一个可视容器中。这样一来,恰当地配置系统,在正确的时间采集正确的数据以恰当地发现问题,就成了主要挑战。

图4:DSP 工具被用来显示抽取自DSP 的调试数据

应用空间差异:DSP 应用越来越多,给DSP 测试和集成工程师带来了困难。应用不同,调试的成本就不同:DSP 基站应用要求高带宽高频率调试。

VoIP 应用要求较高的MIPS 密度,并需要每块板上有多个同类处理器。

手机和其它无线应用则需要不同类的多处理器以及极高的系统级集成。

汽车DSP 应用只需低成本的调试方案,其中DSP 芯片管脚非常重要。

用户开发环境;DSP 开发商的开发环境在改变,而DSP 调试技术也在改进,以适应这些新的开发环境。DSP 工程师正在将调试平台从台式电脑系统向笔记本电脑系统过渡,以便能带到现场在客户的场所下进行调试。便携式远程应用要求便携式DSP 调试环境。

时钟率不断升高:随着DSP 内核时钟速率的升高,调试所需的数据量也不断扩大。

实际上,这个数据量是直接和DSP 内核时钟率成比例的。工程师需要增加DSP管脚,并扩大每个管脚的数据量,以确保能够了解到设备的运行情况。

各种级别的DSP 调试在集成过程中提供了各种作用。用户的体验使之能够尽快地提高生产力。基本的调试让DSP 开发人员可以配置好应用并使之运行,实时捕捉高带宽数据等高端调试让开发人员能使应用实时运行,而基本调整则帮助开发人员调整代码大小和性能。

片上和片外仿真的结合则能带来很多好处。实时执行控制可以带来移动、运行、断点(程序计数器)和数据观察点等标准功能。更高端的事件触发可带来设备可视性,并控制程序员模式。实时数据采集可通过调节一个稳定的程序来提供算法的实时可视性。而追踪功能则让工程师可以在整个调试不稳定程序过程中实时了解程序装况。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多

.jpg)