VXI总线测试平台是仪器测量领域的前沿技术,可以灵活地组建自动测试系统,其模块化、灵活性强、即插即用、数字吞吐能力强的特点使VXI总线测试平台的应用越来越广泛。

在自动控制、智能检测、数字系统故障诊断领域,经常需要非周期性地产生任意编码的数字序列,作为激励信号源。基于VXI总线的任意数字信号发生器,是一个B尺寸、单槽、A16/D16、寄存器基模块,它能够产生任意编码的数字信号,8路数字信号均可独立地任意编辑,输出信号最小脉宽为25ns。采用Altera公司的FLEX系列的FPGA,可实现寄存器基接口电路和部分功能电路。用LabWindows/CVI软件设计了虚拟仪器软面板,界面友好,操作方便。

1 系统组成及工作原理

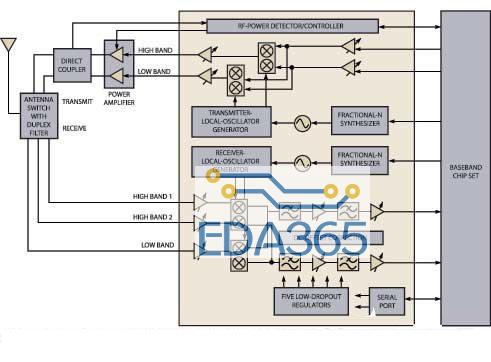

数字信号发生器采用VXI总线测试平台,有8路独立的输出信号,均可预先存储在容量为64K的静态存储器中,可以独立地编辑各种输出信号;时钟频率最高可达40MHz;输出信号支持高电平、低电平和高阻态三种状态;输出电平兼容CMOS/TTL电平;输出信号摆率不超过±5ns;采用可编程分频器,实现对时钟的任意分频;输出电平脉冲宽度可编程调节。系统的组成框图如图1所示。

在PC机上将编辑好的8路波形数据文件和1路三态控制数据文件分别装载到64K×8的静态存储器和64K×4的静态存储器中。波形文件的装载是通过VXI总线的地址译码选择A1~A5中某一配置寄存器的地址,再结合写操作来完成的。由于VXI总线每进行一次写操作,都会产生一个低电平有效的脉冲信号LATCH*,LATCH*信号将8路信号的8位编码波形数据和1位三态控制数据存入寄存器,同时LATCH*信号将16位地址计数器的地址加1,当进行下一个写操作时,完成下8位编码波形数据和三态控制数据的装载,如此反复,直至所有的波形数据装载完毕。波形数据文件的装载在LabWindows/CVI所开发的驱动程序作用下工作,当系统加电或软件复位时,16位地址计数器的初始地置为0000H,在16位地址计数器的作用下,能够实现0000H~FFFFH或任一指定地址范围的数据加载。

当驱动程序输出波形文件时,指定某一起始地址作为16位的地址计数器的当努、当发出允许输出信号时,由可编辑分频器所分频的时钟信号同时加到16位地址计数器、输出触发器74ACT11825以及D触发器SN74ACT74上,在时钟信号的作用下,16位地址计数器开始计数,输出的16位地址作用在静态存储器上。静态存储器采用的是CYPRESS公司的CY74194芯片,从地址有效到数据输出的最小延迟时间为12ns,存储器输出的8路波形数据DAIN[7..0]和1路三态控制信号CIN作用在输出芯片74ACT11825上,如图2所示。当三态控制存储器输出的信号为低电平时,74ACT11825的时钟允许信号线有效,输出的波形数据与静态存储器中选通的波形数据;当三态控制存储器输出的信号为高电平时,则74ACT11825的时钟允许信号线无效,此时的高电平信号经过SN74ACT74触发器的输出端,作用在74ACT11825的输出使能端上,使输出信号为高阻态。

2 任意可编程分频器的实现

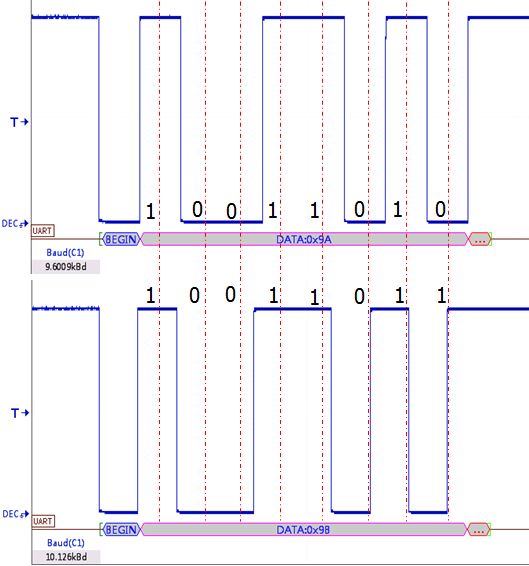

任意可编程分频器是用来实现对40MHz时钟信号的任意分频,它实现的分频值由输入的初始值d[WIDTH-1..0]所决定。这里取WIDTH=10,则能实现2~1024的分频。也可以根据电路的不同要求,选择不同的WIDTH值,实现不同的分频。由于采用ALTERA公司的可编程器件,用AHDL硬件语言描述的分频器代码如下:

PARAMETERS

(MIDTH=4);--定义数据宽度,来确定分频值

INCLUDE "lpm_counter"; --MAX PLUS II自带的函数

INCLUDE "lpm_compare"; --MAX PLUS II自带的函数

SUBDESIGN var_div1

(SysClk :INPUT;--被分频的时钟,这里为40MHz

cnt_en :INPUT=VCC;--分频允许,这里用作波形输出的使能信号

sclr :INPUT=GND;--清零信号,使输出时钟清零,这里用作波形输出结束信号

d[WIDTH-1..0] :INPUT;--定义分频值

EVEN :OUTPUT;--输出已被分频的时钟信号

q[WIDTH-1..0] : OUTPUT;)

VARIABLE

Counter :LPM_COUNTER WITH (LPM_WINDTH=WIDTH);

Max_cnt :NODE;

Dlitch :DFF;

BEGIN

Max_cnt = LPM_COMPARE(d[]-1,counter,q[], , ,)-所计脉冲数与初始设定值相等时,产生的高电平信号

WITH(LPM_WIDTH=WIDTH)

RETURNS (.aeb);

counter.clock = SysClk;

counter.cnt_en = cnt_en;

counter.sclr = (max_cnt AND cnt_en)OR sclr;

Dlitch = max_cnt AND cnt_en;

Dlitch.clk=SysClk;

EVEN = Dlitch; --输出产生的高电平信号

q[]=counter.q[];

END;

在MAX PLUS II软件中进行仿真,设定DATA[7..0]的值为5,即为5分频,输出波形EVEN如图3所示。

3 VXI总线接口设计

采用Altera公司的FLEX系列的EPF10K20RC208-3的FPGA实现寄存器基接口芯片。由于该器件集成度高,可方便地改变逻辑,而且对逻辑设计可事先进行功能模块和定时模拟,因而使得接口设备更轻松,调试更方便。接口电路实现了如下功能:①内部集成了VXI总线所需的寄存器,由地址信号A1~A5为各个寄存器译码分配地址,寄存器类型分别为ID寄存器、仪器类型寄存器、状态/控制寄存器、控制寄存器。②数据总线驱动器,其功能为将P1连接器上的16位数据线D0~D15送至模块内部数据总线DBD~DB15或反之。可用两个8位三态双向缓冲器组成。用READ控制数据传递方向,用DBEN*选能。③总线握手控制,其功能为利用P1连接器上的信号控制DS1*、DS0*、WRITE*和地址线译码输出地址信号共同产生DBEN*、LATCH*和DTACK*信号,LATCH*可用来参与选择模块内需要写数据的寄存器。DTACK*信号输出到P1连接器上,使VXI总线系统能正常工作并按规定时序读*写数据。DBEN*用来控制模块内地址及数据的有效周期。这部分电路在MAX PLUS II中。分别用AHDL硬件描述语言和原理图方式进行描述。用AHDL硬件描述语言实现读状态机、写状态机和中断状态机,产生的DBEN*、LATCH*、DTACAK*信号应符合VXI总线系统中数据读/写的时序规范。④译码16位VXI总线地址,具有16位数据线的传送能力,采用LabWindows/CVI软件,实现对某一地址的读写操作,完成波形数据文件的加载、控制波形文件的输出、停止输出等操作。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多