1 引言

动态信号分析仪在电子测量领域中称为频域中的“射频万用表”,可见其重要性和宽泛应用。动态信号分析是将时域信号转化为频域进行处理,一般要求使用时窗技术,如快速傅氏变换(FFT)、离散傅氏变换(DFT)等。如果采样点为N,直接DFT运算需要N2次乘法操作,需用大量运算时间。而FFT运算可将运算减少到(N/2)log2N次乘法,因此,FFT成为动态信号分析的核心算法。

这里提出一种基于TMS320F2812的便携式动态信号分析仪设计方案,以数字信号处理为基础,利用数字信号处理器强大的数据处理能力分析所采集的信号,优化动态信号的FFT算法.从而实现对各频率成份和功率谱的计算分析以及失真度的测量,其分析结果在液晶显示器(LCD)上显示。

2 动态信号分析原理

动态信号分析方法有时域分析法、频域分析法等。其中频域法最适合动态信号分析FFT算法。该系统采用FFT算法.其本质是DFT的快速算法。FFT算法是将长序列DFT根据其对称性和周期性分解为短序列的DFT之和。N点的DFT先分解为2个N/2点的DFT,每个N/2点的DFT又分解为N/4点的DFT。最小变换的点数即所谓FFT的“基数”。因此,基数为2的DFT最小变换是2点DFT(或称蝶形运算)。在基数为2的N点FFT中,设N=2,则总共可分成M级运算,每级中有(N/2)log2N个蝶算,则N点FFT总共有(N/2)log2N个蝶算,1个蝶算只需一个复数乘法对N点FFT需计算(N/2)log2N个复数乘法、(N/2)log2N个复数加法。一般来说,FFT比DFT运算量要小得多,N点的FFT需做(N/2)log2N次乘法运算,而N点DFT需要做/N2次乘法运算,由此看来N点DFT运算量大约是FFT的2N/log2N倍,分析动态信号频率成份,首先以采样频率fs采样N点(N=2M),经快速傅立叶变换得到其频谱。

由谱分辨率F=fs/N,如果保持采样点数N不变,提高其分辨率(F减小),必须降低采样频率,采样频率的降低会引起谱分析范围的减少。如果保持fs不变,为提高频率分辨率,可增加采样点数N,因为NT=Tp,T=fs-1,只有增加对信号的观察时间Tp,才能增加N。Tp和N可以按照的条件选择。

3 系统硬件电路设计

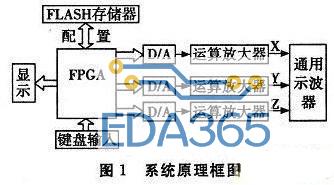

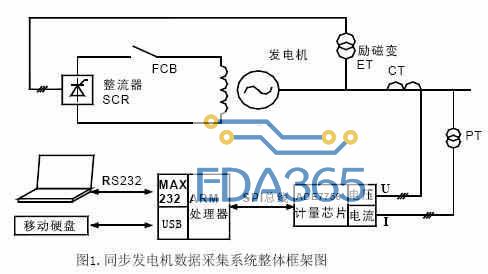

便携式动态信号分析仪的硬件结构图如图1所示。被检测输入信号经以运算放大器LM358为核心的调理电路后送至TMS320F2812 DSP内部自带的12位A/D转换器采样后,其数字输出信号送至DSP内核处理单元进行FFT处理。经过DSP运算处理后,实现各分量频率值和功率值的计算,信号失真度的计算和周期信号的检测,其分析结果由屏幕式LCD显示。键盘采用键盘查询方式中断处理,实现各种工作模式和显示界面的切换。

3.1 调理电路

在设计调理电路时,由于要将被采样信号的电压幅度调理到A/D转换器所能接收的范围内并滤除高频噪声信号,因此采用级联方式。其中第一级选择高精度集成运算放大器LM358组成电压跟随器,具有隔离作用;而第二级放大电路实现信号的比例放大和低通滤波,如图2所示。图2中运算放大器LM358构成反向比例放大电路,Ui是经第一级电压跟随器隔离后的电压信号,R1、R3构成反向比例电路,将输入信号按比例缩小4.7倍,C3、R3构成RC低通滤波网络,其电路截止频率f=1/2πR3C3=1/2π×1 kΩ×0.01 μF=15 923 Hz,符合设计要求(其信号频率范围0~10 000 Hz)。引脚7和引脚4分别接一只0.1μF的瓷片电容,用于滤除高频。为了减少失调电流,引脚3接R2(其阻值约为R1和R3的并联电阻);输出信号U0送至第三级加法电路。第三级加法电路可将信号升高0 V以上,满足A/D转换需求(该系统采用TMS320F2812内部自带A/D转换器)。调理完成后送至DSP进行数字信号处理。

3.2 系统控制单元

系统控制单元采用32位定点数字信号处理器TMS320F2812。该器件采用高性能的静态CMOS技术,主频达150 MHz,使得指令周期缩短6.67 ns,从而提高控制器的实时控制能力。其高性能32位CPU,单周期32x32乘法累加运算操作特性,能够完成64位的数据处理,实现高精度的处理任务。高效的代码转换功能(支持C/C++和汇编)并与TMS320F24x/LF240x程序代码兼容。片内存储器资源包括:片内128 K×16位的Flash,128 K×16位ROM,18 K×16位的SARAM,1 Kxl6位一次可编程的存储器OTP。片上Flash/ROM具有可编程加密特性,便于现场软件升级。TMS320F2812带有128位保护密码,防止非法用户通过JTAG仿真接口查看Flash/OTP/L0/L1的内容,访问外设和装载某些不合法的软件,保证相关数据的安全性。A/D转换器有16个通道,可配置成2个独立的8通道模块,便于服务事件管理器A和事件管理器B。这2个独立的8通道模块可级联成一个16通道的模块。A/D转换器虽具有丰富的输入通道和2个排序器,但只有1个转换器。2个8通道模块自动排序转换,通过多路开关选择任意一个8通道模块。在级联模式下自动排序器作为一个16通道的排序器。每个排序器一旦转换完成,就将所选择通道的值存储在各自的ADCRESULT寄存器中。自动排序允许对同一通道多次转换,允许用户使用过采样算法,相对传统单次采样转换,这将提高结果的精度。

为了获得规定的A/D转换器精度,须采用正确的线路板布局。为了获得最佳效果,引脚ADCINxx要尽量远离数字信号线,可最大程度地消除数字电路中开关噪声与A/D转换器输入之间的耦合;同时,A/D模块的电源引脚与数字电源之间需采用适当隔离。

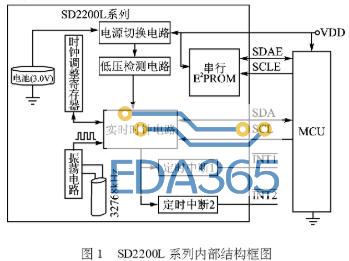

3.3 显示模块LCD

CMl2864-10是一种图形点阵液晶显示器,它主要由行驱动器/列驱动器及格128x64全点阵液晶显示器组成,可实现显示图形以及8×4个汉字(16×16点阵)。LCD与DSP的接口电路如图3所示,由于TMS320F2812DSP是低功耗设计,所有的数字输入都与TTL兼容,所有输出都是3.3 V CMOS电平,不能接收5 V输入,而显示模块LCD接口为5 V的输入输出,所以在实际应用时还需电平转换器SN74ALVCl64245。

4 系统软件设计

系统软件包括主程序,捕获中断服务子程序,T1的周期中断服务子程序、A/D转换中断服务程序,FFT运算子程序和LCD显示子程序。主程序主要完成系统初始化,包括CPU、PIE寄存器、PIE中断向量表、LCD液晶屏,A/D转换器初始化等,以及查询工作模式设定。根据不同的工作模式进入相应的服务子程序,其主程序流程如图4所示。

设置两个断点,当程序执行到断点时,观察接收数据和显示图像。运行到第一个断点处,A/D采样完成,此时可设置图像观察A/D采样的结果(即显示Ad_data1数组);运行到第二个断点处,FFT变换完成,可设置图像观察FFT变换后没有取模时的结果(即显示ipcb数组);继续运行程序,停止运行后,程序会停在循环语句处,同样可设置图像观察取模后的结果,即显示mod数组,图5从上至下分别为1 024点的Ad_datal数组,ipcb数组,mod数组的图像显示,其中,横坐标是采样点数.纵坐标是信号幅度。

5 结论

针对频谱分析。设计基于TMS320F2812 DSP动态信号分析仪.并在此基础上采用一系列数据处理措施实现实数的FFT变换。对于动态信号分析,A/D的采样速率决定处理信号的频率为20 kHz以下.在分析频谱前需估计信号频率范围估计,然后调整采样速率保证1 024点能够采样一个以上的周期.同时还要满足香农采样定理。该系统采用TMS320F2812DSP控制,外围电路少,系统稳定,功能强,操作方便,低成本.具有广泛使用价值。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多