1 引 言

运算放大器是许多模拟系统和混合信号系统的一个完整部分,伴随着每一代CMOS 工艺,由于电源电压和晶体管沟道长度的减小,为运算放大器的设计不断提出新的挑战。在采样保持电路的设计中,运算放大器是最关键的模块之一,其带宽,摆率,增益,噪声,失调等性能直接决定了采样保持电路模块的速度,精度等性能。

2 折叠共源共栅结构

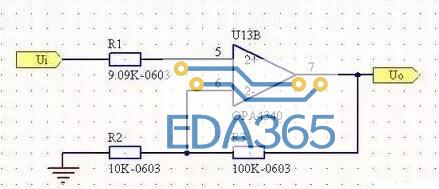

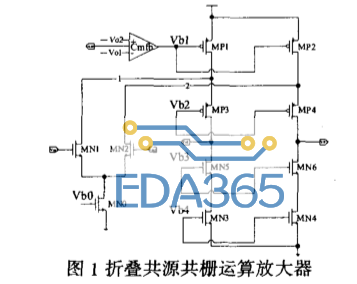

电路结构如图1 所示。

图1 折叠共源共栅运算放大器

运算放大器采用折叠共源共栅结构,采用NMOS 输入差分对MN1 和MN2。MN0 为输入差分对的尾电流源,向MN1 和MN2 提供直流偏置。MP1 和MP2 为电流源,向输入管和共源共栅管提供直流偏置。MP3 和MP4 为共源共栅管,用来提高运算放大器的增益。MN3,MN4,MN5 和MN6 是共源共栅电流镜负载,采用共源共栅结构可以提高输出阻抗。

与套筒式结构相比,折叠共源共栅结构放大器输出摆幅增大了一个过驱动电压,另外较大的共模输入范围是我们选择折叠共源共栅结构的主要原因。

3 开关电容共模反馈(CMFB)电路

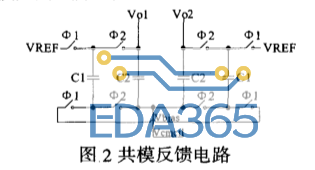

由于采用全差分结构,而在高增益的全差分运算放大器中,输出共模电平对器件的特性和适配相当敏感,而且不能通过差模反馈来达到稳定,因此设计时增加了共模反馈电路模块,来稳定输出共模电平。共模反馈电路如图2 所示。共模反馈电路与主运放的连接如图1 所示。

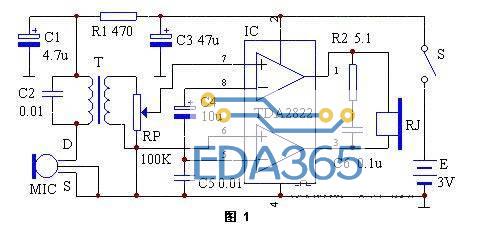

图 2 共模反馈电路

该结构与电阻检测方式,运用MOSFET 作为源级跟随器和可变电阻的检测技术相比有明显优点。其工作流程如下,时钟信号在Φ1 相位时,为C1 充电,确定C1 两端的电压,在Φ2 相位时,将C1 与C2 并联,根据Vo1 和Vo2 平均值的大小确定输出共模电平。例如,(Vo1+Vo2)/2>VREF,则输出共模电平cmctl bias v > v ,从而使尾电流减小,最终导致输出(Vo1+Vo2)/2 减小,连续几个周期调整后,将使(Vo1+Vo2)/2≈Vref。从而达到控制输出共模电平的目的。

4 偏置电路

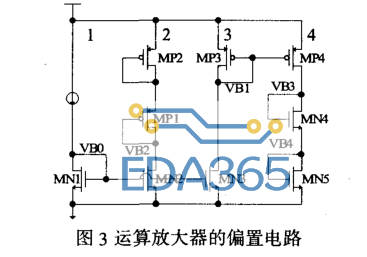

如图3 为放大器的偏置电路。MN1,MN2 及MN1,MN3 组成NMOS 电流镜,2,3 支路将镜像1 支路的电流,MP3,MP4 组成PMOS 电流镜,这样,4 支路的电流将镜像自3 支路。MP2,MP1,MN4,MN5 采用二极管连接方式,以提供主放所需要的偏置,1 支路所用电流源,在电路设计中已替换成沟道长度L 较大(可以提供高阻抗)的管,调整此PMOS 管的尺寸可以调整偏置电流,进而控制运放的增益,带宽及摆率等特性。

图 3 运算放大器的偏置电路

5 仿真验证

5.1 放大器的AC 特性分析

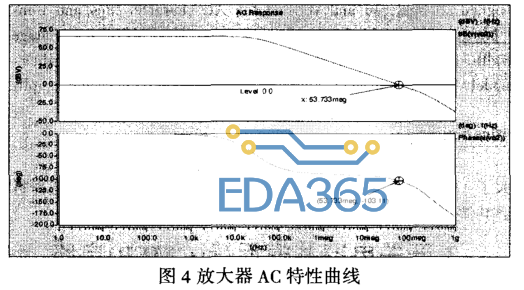

采用Cadence Spectre 仿真工具,CSMC0.6um 工艺模型进行仿真。得到如图4 的仿真结果。

图4 放大器AC 特性曲线

从而可以得到运算放大器的AC 特性,可以看出运算放大器是稳定的。

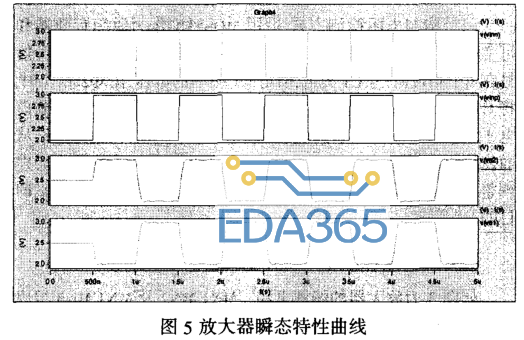

5.2 放大器的瞬态特性验证

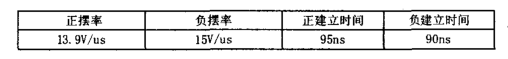

在输入端加阶跃信号图,得到放大器瞬态特性验证结果曲线,如图5 所示。其中,图中上半部分两条曲线为输入差分信号(方波信号),下半部分两条曲线为输出信号。从而可以确定放大器的瞬态特性如表2所示。

5 放大器瞬态特性曲线

表放大器的瞬态特性

6 结论

在5V 电源电压下,基于CSMC0.6um 工艺模型,驱动1pF 负载时,运算放大器功耗为6.2mW,开环增益70dB,带宽54MHz,相位裕度77,摆率15V/us,建立时间95ns。可用于采样保持电路中。本文作者创新点:采用折叠共源共栅结构、开关电容共模反馈电路以及低压宽摆幅偏置电路,实现了在高稳定下的高增益、大输出摆幅和较大的共模输入范围。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多