摘要:分析了功率MOSFET雪崩击穿的原因,以及MOSFET故障时能量耗散与器件温升的关系。和传统的双极性晶体管相比,反向偏置时MOSFET雪崩击穿过程不存在“热点”的作用,而电气量变化却十分复杂。寄生器件在MOSFET的雪崩击穿中起着决定性的作用,寄生晶体管的激活导通是其雪崩击穿的主要原因。在MOSFET发生雪崩击穿时,器件内部能量的耗散会使器件温度急剧升高。

关键词:双极性晶体管;功率MOSFET;雪崩击穿;寄生晶体管

1 引言

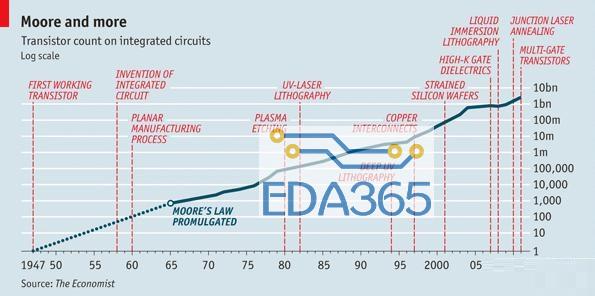

功率MOSFET在电力电子设备中应用十分广泛,因其故障而引起的电子设备损坏也比较常见。分析研究功率MOSFET故障的原因、后果,对于MOSFET的进一步推广应用具有重要意义。在正向偏置工作时,由于功率MOSFET是多数载流子导电,通常被看成是不存在二次击穿的器件。但事实上,当功率MOSFET反向偏置时,受电气量变化(如漏源极电压、电流变化)的作用,功率MOSFET内部载流子容易发生雪崩式倍增,因而发生雪崩击穿现象。与双极性晶体管的二次击穿不同,MOSFET的雪崩击穿常在高压、大电流时发生,不存在局部热点的作用;其安全工作范围也不受脉冲宽度的影响。目前,功率器件的故障研究已经从单纯的物理结构分析过渡到了器件建模理论仿真模拟层面。因此,本文将从理论上推导MOSFET故障时漏极电流的构成,并从微观电子角度对MOSFET雪崩击穿现象作详细分析。同时,还将对故障时器件的能量、温度变化关系作一定的分析。

2 功率MOSFET雪崩击穿理论分析

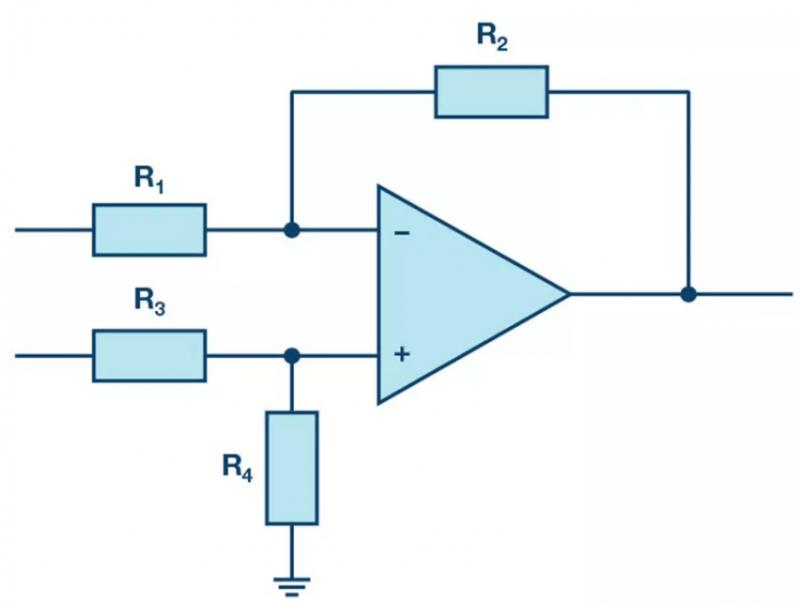

图1(a)为MOSFET的体内等效电路,其中含有一个寄生的双极性晶体管V2,它的集电极、发射极同时也是MOSFET的漏极和源极。当MOSFET漏极存在大电流Id,高电压Vd时,器件内电离作用加剧,出现大量的空穴电流,经Rb流入源极,导致寄生三极管基极电势Vb升高,出现所谓的“快回(Snap-back)”现象,即在Vb升高到一定程度时,寄生三极管V2导通,集电极(即漏极)电压快速返回达到晶体管基极开路时的击穿电压(增益很高的晶体管中该值相对较低),从而发生雪崩击穿,如图2所示。

下面利用图1的等效电路来分析MOSFET的雪崩击穿。

假设三极管Vb≈0.6V,Vb=IbRb,则可得MOSFET源极电流

Is=Ido+γVb=Ido+γRbIb(1)

式中:Ido为漏极电压较低时的饱和漏极电流;

γ为大信号体偏置系数(Large Signal Body-bias Coefficient),定义为

γ=ΔId/ΔVb(2)

当Vb很高时,漏极的强电场引起电子沟道电流的雪崩式倍增,产生的空穴向基极流动。

如果增益为M,则基极电流为

Ib=Id-Is=MIs-Is=(M-1)(Ido+γRbIb)(3)

可得

当发生击穿时,有

IbRb≈0.6V(5)

由式(4)及式(5)可得击穿时的关系式(下标SB为雪崩击穿标志)为

M的经验表达式为

式中:BV为漏极同p-基极间电压;

n为常数。

由式(4)及式(7)可得

在“快回”点,由式(8a)和式(8b)得

由式(6)及式(7)得

由式(10b)得

式(11)说明,ID,SB为MOSFET漏极寄生三极管集电极在二次击穿时的电流的总和。式(10a)表明,雪崩击穿电压随着Ido或Rb增大而减小。式(10b)则给出了雪崩击穿的边界电压。大量的研究和试验表明,Ic,SB很小。

另外,由于寄生三极管的增益较大,故在雪崩击穿时,三极管基极电子、空穴重新结合所形成的电流,以及从三极管集电极到发射极空穴移动所形成的电流,只占了MOSFET漏极电流的一小部分;所有的基极电流Ib流过Rb;当Ib使基极电位升高到一定程度时,寄生晶体管进入导通状态,MOSFET漏源极电压迅速下降,发生雪崩击穿故障。

3 功率MOSFET雪崩击穿的微观分析

双极性器件在发生二次击穿时,集电极电压会在故障瞬间很短时间内(可能小于1ns)衰减几百伏。这种电压锐减主要是由雪崩式注入引起的,主要原因在于:二次击穿时,器件内部电场很大,电流密度也比较大,两种因素同时存在,一起影响正常时的耗尽区固定电荷,使载流子发生雪崩式倍增。对于不同的器件,发生雪崩式注入的情况是不同的。对于双极性晶体管,除了电场应力的原因外,正向偏置时器件的热不稳定性,也有可能使其电流密度达到雪崩式注入值。而对于MOSFET,由于是多数载流子器件,通常认为其不会发生正向偏置二次击穿,而在反向偏置时,只有电气方面的原因能使其电流密度达到雪崩注入值,而与热应力无关。以下对功率MOSFET的雪崩击穿作进一步的分析。如图1所示,在MOSFET内部各层间存在寄生二极管、晶体管(三极管)器件。从微观角度而言,这些

寄生器件都是器件内部PN结间形成的等效器件,它们中的空穴、电子在高速开关过程中受各种因素的影响,会导致MOSFET的各种不同的表现。导通时,正向电压大于门槛电压,电子由源极经体表反转层形成的沟道进入漏极,之后直接进入漏极节点;漏极寄生二极管的反向漏电流会在饱和区产生一个小的电流分量。而在稳态时,寄生二极管、晶体管的影响不大。

关断时,为使MOSFET体表反转层关断,应当去掉栅极电压或加反向电压。这时,沟道电流(漏极电流)开始减少,感性负载使漏极电压升高以维持漏极电流恒定。漏极电压升高,其电流由沟道电流和位移电流(漏极体二极管耗尽区生成的,且与dVDS/dt成比例)组成。漏极电压升高的比率与基极放电以及漏极耗尽区充电的比率有关;而后者是由漏-源极电容、漏极电流决定的。在忽略其它原因时,漏极电流越大电压会升高得越快。如果没有外部钳位电路,漏极电压将持续升高,则漏极体二极管由于雪崩倍增产生载流子,而进入持续导通模式(Sustaining Mode)。此时,全部的漏极电流(此时即雪崩电流)流过体二极管,而沟道电流为零。

由上述分析可以看出,可能引起雪崩击穿的三种电流为漏电流、位移电流(即dVDS/dt电流)、雪崩电流,三者理论上都会激活寄生晶体管导通。寄生晶体管导通使MOSFET由高压小电流迅速过渡到低压大电流状态,从而发生雪崩击穿。

4 雪崩击穿时能量与温度的变化

在开关管雪崩击穿过程中,能量集中在功率器件各耗散层和沟道中,在寄生三极管激活导通发生二次击穿时,MOSFET会伴随急剧的发热现象,这是能量释放的表现。以下对雪崩击穿时能量耗散与温升的关系进行分析。

雪崩击穿时的耗散能量与温升的关系为

雪崩击穿开始时,电流呈线性增长,增长率为

di/dt=VBR/L(13)

式中:VBR为雪崩击穿电压(假设为恒定);

L为漏极电路电感。

若此时MOSFET未发生故障,则在关断时刻之前,其内部耗散的能量为

式中:E为耗散能量;

Io为关断前的漏极电流。

随着能量的释放,器件温度发生变化,其瞬时释放能量值为

式中:

到任意时刻t所耗散的能量为

在一定时间t后,一定的耗散功率下,温升为

式中:K= ,其中ρ为密度;k为电导率;c为热容量。实际上耗散功率不是恒定的,用叠加的方法表示温升为

则温升可以表示为

由上面的分析过程可以看出,在功率MOSFET发生雪崩击穿时,器件温度与初始电流,以及器件本身的性能有关。在雪崩击穿后如果没有适当的缓冲、抑制措施,随着电流的增大,器件发散内部能量的能力越来越差,温度上升很快,很可能将器件烧毁。在现代功率半导体技术中,MOSFET设计、制造的一个很重要方面就是优化单元结构,促进雪崩击穿时的能量耗散能力。

5 结语

与一般双极性晶体管的二次击穿不同,MOSFET的雪崩击穿过程主要是由于寄生晶体管被激活造成的。MOSFET由于工作在高频状态下,其热应力、电应力环境都比较恶劣,一般认为如果外部电气条件达到寄生三极管的导通门槛值,则会引起MOSFET故障。在实际应用中,必须综合考虑MOSFET的工作条件以及范围,合理地选择相应的器件以达到性能与成本的最佳优化。另一方面,在发生雪崩击穿时,功率器件内部的耗散功率会引起器件的发热,可能导致器件烧毁。在新的功率MOSFET器件中,能量耗散能力、抑制温升能力的已经成为一个很重要的指标。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多