由于人眼只能看到 390nm(蓝光)至 700nm(红光)波长之间的可见光谱,但成像设备凭借各种传感器能捕获到更宽泛波长的图像,包括 X 光、紫外线、红外线以及可见光谱,因此基于成像传感器的嵌入式视觉成为先进最热门的技术之一,应用包括无人驾驶、无人机、机器人、医疗诊断等很多领域,现在,嵌入式视觉正结合了机器学习向自主智能视觉系统发展,但机器学习需要针对应用场景优化,且传统开发时间长,现在,FPGA领头羊赛灵思就放了一个大招,它推出的一个产品不但可以大大简化视觉导向机器学习,更可以提升视觉智能系统的响应时间,并实现软硬件可重配置。

1、reVISION堆栈横空出世,它有多牛?

3月13日,赛灵思在全球同步推出Xilinx reVISION? 堆栈,它能够支持更广泛的没有或者很少硬件设计专业知识的嵌入式软件和系统工程师,使其与机器学习、计算机视觉、传感器融合,从而可以更快速地开发视觉导向的智能系统。

“reVISION 支持以最快速度打造响应最快的视觉系统,相比最具竞争力的计算嵌入式 GPU 和典型 SoC,将机器学习推断的单位功耗图像捕获速度提升了 6 倍,将计算机视觉处理的单位功耗帧速度提升了 42 倍,时延降低为 1/5。”在赛灵思媒体发布会上,Xilinx公司战略与市场营销部高级副总裁Steve Glaser指出,“即便是没有硬件专业知识的开发人员也能通过结合使用 C/C++/OpenCL 开发流程、业界标准的框架,以及 Caffe 和 OpenCV 等库,用单个 Zynq SoC 或 MPSoC 芯片开发出嵌入式视觉应用。”

以下图关于开发易用性和和开发时间为例,如果采用传统的RTL流程,如果采用赛灵思FPGA则,赛灵思提供了20%解决方案用户解决剩下的80%工作,而自从赛灵思推出软件定义开发环境以后,开发效率大大提升,例如软件定义数据库开发SDSoc,可以把以前需要三周的开发缩短为4天。现在,如果采用赛灵思 reVISION? 堆栈,则机器学习开发时间可以大大缩短!

“我们有大约1100家SDSoC开发环境付费用户,其中半数都是在开发视觉应用。我们了解到,客户希望能够应用行业标准的库和行业应用框架来帮助他们进一步提高工作效率,所以我们推出了reVISION堆栈,它可以大大减少开发时间,采用了这个堆栈,用户能有80%的高起点,他们只需要做剩下20%就能够完成的应用开发。”Steve Glaser强调,“而且,我们的效率更高,在机器学习方面最主要的一个指标就是图像/秒/瓦,在这方面赛灵思的产品比业内最佳的其他方案要高出6倍,其他方案包括英伟达Tegra、高通的So等,在计算机视觉方面,我我们图像/秒/瓦指数比竞争对手高出42倍。”

另外,在机器学习领域,很多的应用性能不仅仅取决于推断,还取决于响应时间时延,在这方面,Steve 表示赛灵思的reVISION堆栈方案只有竞争对手的1/5,就凭这点,在很多汽车应用中,就可以拯救更多的生命!

以下图为例,如果前车急停,如果用reVISION堆栈,它只需要2.7毫秒就可以让后车停止。而如果是英伟达的GPU,则需要49毫秒甚至320毫秒才能停住,如果汽车的时速是65英里,则停车的距离差可能就会从1.5米到100米,而这个差距就是发生了事故和没有发生事故的差别。

2、客户如何评价reVISION? 堆栈?

对于这个简化机器学习开发的革命性产品,赛灵思客户如何评价呢?

“我们的Dobby 口袋无人机-AI版集成了复杂的计算机视觉和机器学习技术,通过手势控制和对象及主题跟踪为消费者提供独特的体验,”零度智控CEO杨建军说,“这些功能,直到最近还只属于更昂贵的系统,而我们借助Zynq All Programmable器件将这些复杂的算法实现到了Dobby AI中。我们非常高兴看到赛灵思推出reVISION堆栈平台,它将支持我们的团队更容易地提升这些关键计算机视觉和机器学习算法,从而助力我们为Dobby AI赋予更加独特的个性。拥有像Xilinx这样不断深耕技术的合作伙伴,将确保我们可以在这个领域持续开发突破性的解决方案。”

深鉴科技(DeePhi)创始人兼CEO姚颂表示:“深鉴科技致力于为机器人/无人机和安防监控等行业应用提供先进的嵌入式视觉解决方案。我们已经开发了一个完整的工作流程,用于在FPGA上部署深度学习算法,实现算法、软件和硬件的协同优化。reVISION 堆栈中所包含的完整的工具包,可以让我们的客户更加轻松容易地利用全可编程FPGA 和SoC —即使是没有任何FPGA开发背景的算法工程师也能有效地部署经过训练的模型。这对于利用FPGA搭建智能解决方案有莫大的好处。”

“Vrvana enables truly immersive Mixed‐Reality experiences by leveraging Xilinx’s All Programmable technology, which provides the flexibility and throughput capability important for a low‐ latency, high‐resolution, camera‐based Mixed‐Reality solution that is unique on the market,” said Bertrand Nepveu, CEO. The release of the reVISION stack for Xilinx will give us the ability to more rapidly integrate new computer vision and machine learning features into our headsets.”

此外很多从事机器学习的厂商对reVISION 堆栈表示了欢迎这里不一一列举了。据透露目前在无人驾驶、无人机、工业视觉、医疗诊断领域已经有大量客户采用了赛灵思的FPGA嵌入式视觉方案,因此,赛灵思能洞悉客户需求,及时推出加速视觉导向的机器学习堆栈。

3、为什么reVISION 堆栈性能如此突出?

机器学习从应用端走向云端是必然发展趋势,赛灵思一直深耕这个领域,面向云应用,赛灵思推出了可重配置加速堆栈(2016年11月推出详见《FPGA 成超级数据中心主流应用,赛灵思5年转型见成效》),目标直指包括机器学习推断在内的各种计算加速应用。 而reVISION? 堆栈则是面向端应用机器学习加速工具。

Steve 表示reVISION? 堆栈性能突出赢在赛灵思FPGA的独特工艺和架构。例如在响应速度快方面,“在嵌入式GPU和典型的SoC中,需要传输的数据以及需要用于计算机视频视觉处理和机器学习的数据是需要经过外部存储,但赛灵思SoC经过了优化,可以简化数据流是从传感器到视觉处理、机器学习甚至到控制的处理无需经过外部存储。所以系统响应速度会快很多。”Steve解释说,“另外一方面响应还可以预知,每次都可以知道系统对于外部事件作出响应的时间,而我们的竞争对手并没有办法去预知响应时间。”

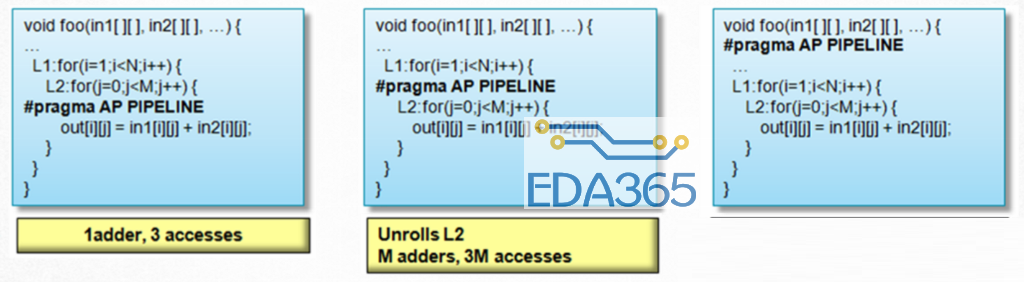

另外,他强调在开发下一代DSP内核时,赛灵思定义了一种高效的DSP内核,赛灵思的 DSP48E2 设计用于在一个时钟周期内高效地完成一个乘法累加算法 , 多达 18x27 位的乘法和多 达 48 位的累加,如下图所示。

在运行 INT8 深度学习时,Altera较宽的 27 位宽自然占有优势。在传统应用中,预加法器一般用于高效实现 (A+B) x C 计算,但这类计算在深度学习应用中很少见。将 (A+B) x C 的结果拆分为 A x C 和 B x C,然后在独立的 数据流中进行累加,使之适用于典型深度学习计算的要求。

对 INT8 深度学习运算来说,拥有 18x27 位乘法器很占优势。乘法器的输入中至少有一个必须为最小 24 位,同时进位累加器必须为 32 位宽,才能在一个 DSP Slice 上同时进行两个 INT8 MACC 运算。27 位输 入能与 48 位累加器结合,从而将深度学习求解性能提升 1.75 倍(1.75:1 即为 DSP 乘法器与 INT8 深度 学习 MACC 的比率)。而其他厂商如Altera所提供的 FPGA 在单个 DSP 模块中只提供 18x19 乘法器,DSP 乘法器与 INT8 MACC 之比仅为 1:1。

“Altera早做下一代DSP开发的时候,本来它的DSP定点效率就要低于赛灵思,它后来做出的决定使得它比原来落后赛灵思的差距又扩大了,比赛灵思的效率低了100%,所以在8位一个周期里我们可以操作运算两次,而它只能一次,所以在DSP架构方面,赛灵思的比它的效率提升两倍,但实际上我们最高效率可以比它大6倍,所以除了这个DSP以外,我们还有其他两个优势。”Steve 表示,“在我们存储器层级上,我们引入一个XRAM架构,另外一个优势是我们的工艺领先Altera一代。”这是一个对比。

他也表示神经网络理论是不断发展的,过去两年里取得的进展几乎要等于之前45年的技术进步 因此赛灵思的方案还可以了重配置性。“通过这样可重配置的功能,就可以应用最新的关于视觉和机器学习方面的最新的技术和进展,而无需来改变自己系统的硬件。”他表示。

另外,在嵌入式视觉领域,越来越多的传感器技术需要融合进来,例如以前是环境传感器,而现在则融合了更多化学、机械、光学、成像、雷达等等,融合的驱动就是人工智能,所以赛灵思的reVISION也考虑到了传感器的融合发展。“传感器融合很重要,例如工业机器人在工作时,除了视觉处理还需要压力处理,因为曾经发生或工业机器人伤害人类的事件,所以需要度传感器信号做融合处理。”他指出。

它的驱动力量在于人工智能,也就是人工智能在所有AI扩展驱动了传感器融合的渠道。所以我们推出的reVISION,它能够实现非常独特的可重配置的功能,不仅仅是能够支持不同的类型和技术传感器,而且还能够支持这些传感器的集成和融合。

从响应速度和可重配置来看,赛灵思的reVISION都非常出众

4、reVISION 堆栈如何使用?

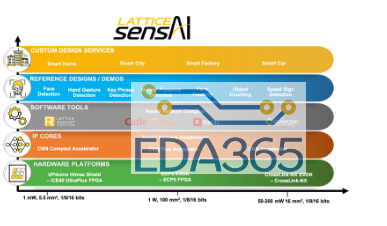

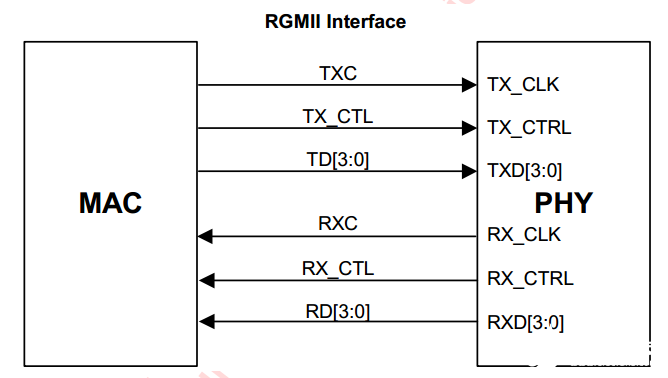

针对客户的视觉应用机器学习,赛灵思除了提供软件堆栈以外,还有硬件的平台和传感器,使得客户可以很快上手。如图的嵌入式视觉开发套件,从28nm的Zynq到最新的16nm MPSOC都有覆盖。

“赛灵思有几百家客户在做基于视觉的系统,还有几十家客户在做机器学习,要把机器学习与计算机视觉相结合。客户需要投入特殊的开发资源,随着reVISION的推出,能够消除机器学习广泛采用所面临的很多障碍。”Steve 强调。

赛灵思 reVISION 堆栈包括用于平台、算法和应用开发的丰富的开发资源,支持最流行的神经网络(诸如 AlexNet、GoogLeNet、SqueezeNet、SSD 和 FCN)以及库元素(如 CNN 网络层的预定义优化型实现方案,这也是构建定制神经网络 DNN/CNN 所需的)。配合丰富的满足加速要求的 OpenCV 功能,支持机器视觉处理。

对应用层面的开发来说,赛灵思支持流行的框架,包括用于机器学习的 Caffe 和用于计算机视觉的 OpenVX(将于 2017 年下半年推出)。reVISION 堆栈还包括赛灵思和第三方提供的基于 Zynq SoC 和 MPSoC 的开发平台。

reVISION 开发流程从 熟悉的C、C++ 和/或 OpenCL 语言及相关编译器技术的基于 eclipse 的开发环境(即 SDSoC 开发环境)启动。在 SDSoC 环境中,软件工程师和系统工程师能以 reVISION 硬件平台为目标,并采用大量的加速就绪型计算机视觉库,很快还能采用OpenVX框架,从而快速构建应用。

对于机器学习,可用 Caffe 等流行的框架来培训神经网络,用 Caffe 生成的 .prototxt 文件对基于 ARM 的软件调度器进行配置,从而驱动专门为可编程逻辑预先优化的CNN 推断加速器。

对计算机视觉和其他专有算法来说,用户可对软件代码进行特征分析,发现瓶颈,并在代码中标出希望加速并进行“硬件优化”的特定功能。“系统优化编译器”则用来创建加速的实现方案,包括处理器/加速器接口(数据移动器)和软件驱动器。结合计算机视觉和机器学习功能,该编译器能创建优化的融合实现方案。

实际开发流程

Steve 介绍了利用reVISION堆栈的开发流程。

reVISION堆栈的开发流程

客户可以首先获得我们的reVISION堆栈,然后有一个带有Zynq和MPSoC的开发板,开发板有传感器,且都是经过预先验证的。在机器学习方面,赛灵思会预装比特流或者配置定制神经网络层用于应用和Zynq器件的快速优化。

客户的应用和算法的工程师会选择他们非常熟悉的框架,赛灵思首要支持的Caffe框架来支持他们的开发应用。然后客户可以使用本地的数据中心来进行训练,做到合适的网络配置,Caffe输出文件就会进入到解决方案当中,然后创建出一个优化的实施方案用于虚拟技术,然后会有一个非常快速的编译过程,对预优化的CNN层进行定时,定制的神经网络层是由ARM处理器来控制,整个编译过程会非常快,之后整个机器学习的应用会非常快的在目标器件上运行。

这个流程是把视觉类机器学习简化了很多

Steve表示未来的智能视觉系统不仅要会思考,而且还能对情境立即做出“响应”。因此机器学习开发方案要适应神经网络理论和算法的不断演化,要具备软硬件的可重配置和升级,此外还要支持广泛的互联性,能进行云端通信,赛灵思的方案都支持上述需求。通过高效的推断和控制,赛灵思实现了传感器的最快响应时间,支持最新的神经网络,算法和传感器的可重构性,并支持与传统或新机器、网络和云的任意连接。

期待机器学习领域赛灵思推出更多有差异化的细分方案。

针对reVISION堆栈的福利活动

庆祝赛灵思reVISION堆栈推出,本微信号特别推出福利活动,凡是转发本条微信,将转发截图发到我微信号朋友将可以进入“FPGA技术交流群”参加红包抽奖,奖品为赛灵思独家制作的reVISION堆栈纪念款T恤!

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多