在“SEMICON Japan 2012”(2012年12月5~7日,幕张MESSE国际会展中心)开幕当天,台积电研发副总经理侯永清(Cliff Hou)登台发表了主题演讲,公布了该公司关于16~10nm FinFET工艺及CoWoS(chip on wafer on substrate,晶圆基底芯片)型3D IC技术的提供日程。

候永清介绍说,SoC(system on a chip)工艺技术方面,台积电将于2013年1~3月启动基于平面晶体管的20nm工艺的风险性量产,在6~9个月以后的2013年底开始提供基于立体晶体管(FinFET)的16nm工艺,再过两年以后,也就是“2015年底,开始10nm FinFET工艺的风险性量产”。

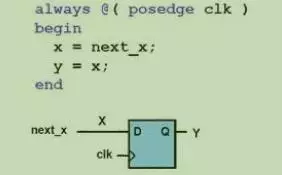

台积电将提供的16nm工艺的金属布线部分直接沿袭20nm工艺,将晶体管部分换成16nm工艺的FinFET。与20nm工艺相比,可使晶体管的工作速度提高20%~25%,使耗电量降低35%。由于金属布线部分在20nm工艺和16nm工艺间通用,因此两工艺的芯片面积相同。

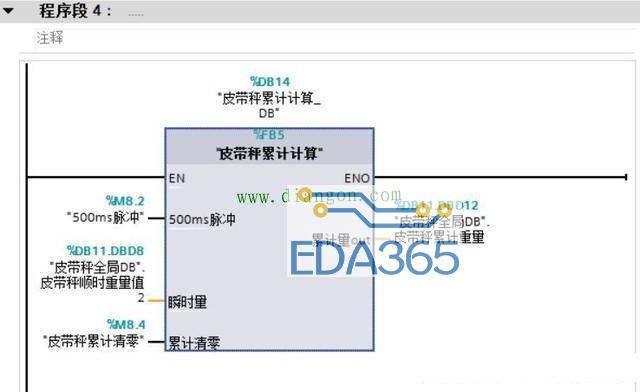

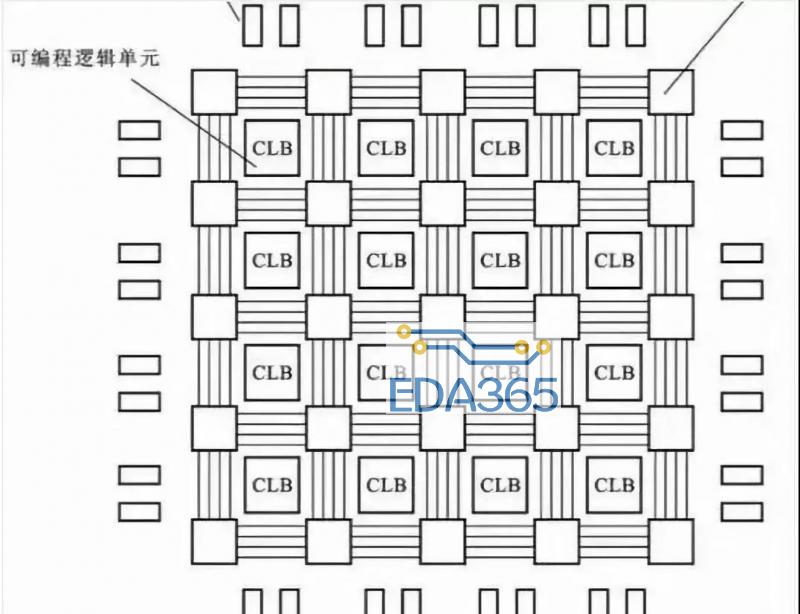

16nm工艺要使晶体管立体化,因此SoC的设计及验证工作需要的时间比以前更长。为了解决这一问题,台积电将建立能够尽快利用支持FinFET的EDA工具及单元库的环境。具体而言,将从2013年1月开始提供测试芯片,从10月开始提供产品芯片的设计环境。

在CoWoS型2.5D及3D IC技术方面,台积电已从2012年9月开始量产。该公司计划2013年1~3月“推出真正的3D IC的第一代技术”(侯永清),该技术将采用将SoC与具备Wide I/O接口的移动DRAM立体层叠起来的设计。(记者:大下淳一,《日经电子》)

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多