隔离模块应用于各类复杂的工业环境中,以提升总线的抗干扰能力,但设备接口可能会采用端子与外部连接,可能会在安装、维修过程中有静电等能量输入,从而导致隔离模块损坏。那么该如何避免这样的问题呢?本文为您揭秘。

带隔离通信接口的设备,在不同的使用、安装状态下,接口会表现出完全不同的ESD特性,了解设备在不同的使用状态下,ESD对接口的影响的机理,才能有针对性地增加保护器件,提升隔离接口的ESD能力。下面以带有隔离CAN或RS-485通信接口为例,对常见的设备状态下,ESD的作用机理进行分析,并提出相应的改善措施。

1. 设备控制侧有接保护地,总线侧悬空

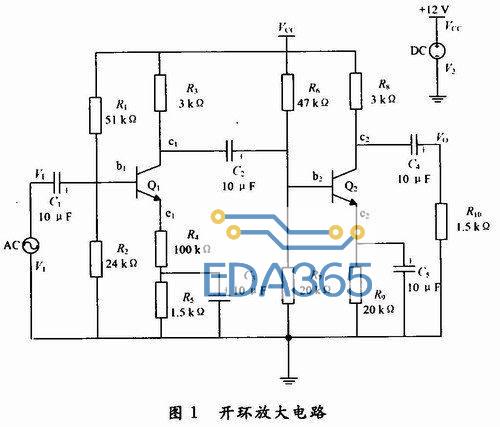

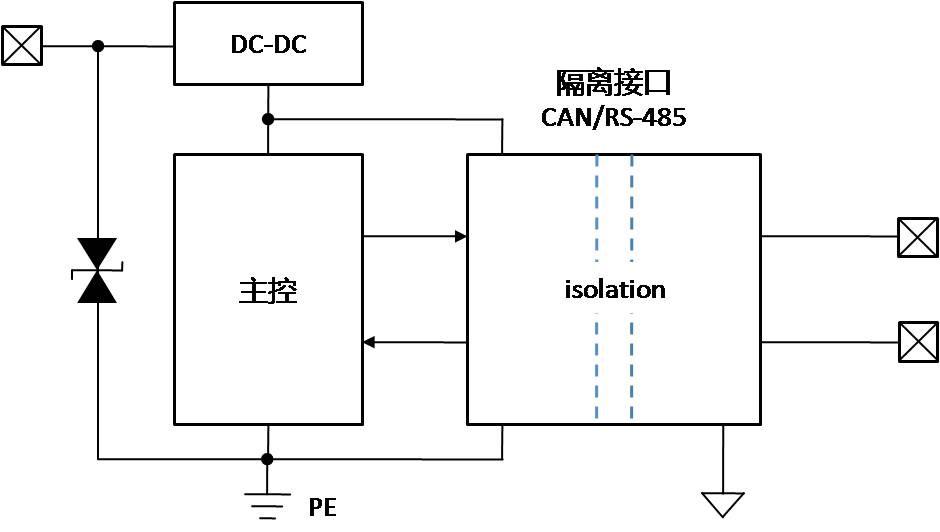

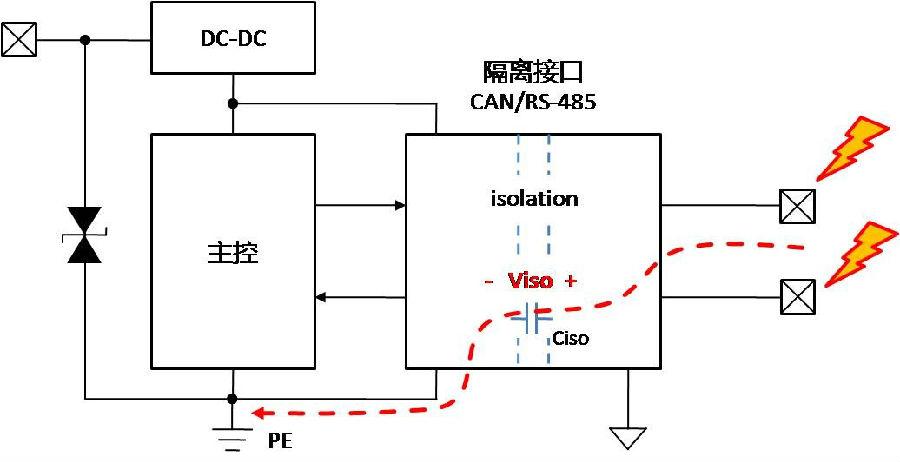

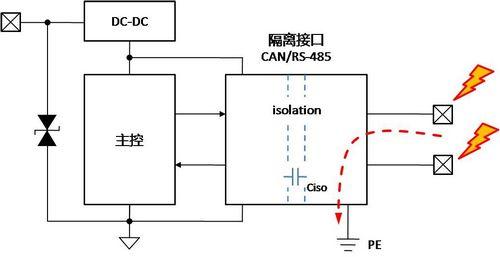

如图 1,此状态下,设备控制侧有接入保护地(PE),总线侧参考地悬空,与PE无任何连接。

图 1

此状态出现的可能场景:

1. 产品开发测试过程中;

2. 单个产品进行ESD测试时;

3. 设备组网时,控制侧已接入保护地,正在进行总线接入或断开操作时;

4. 设备组网后,总线侧未进行接地处理的。

静电分析:

假设控制侧均做了足够的保护措施,当控制侧接口受到静电放电时,能量通过控制侧保护器泄放至PE,对隔离通信接口基本无影响,如图 2。

图 2

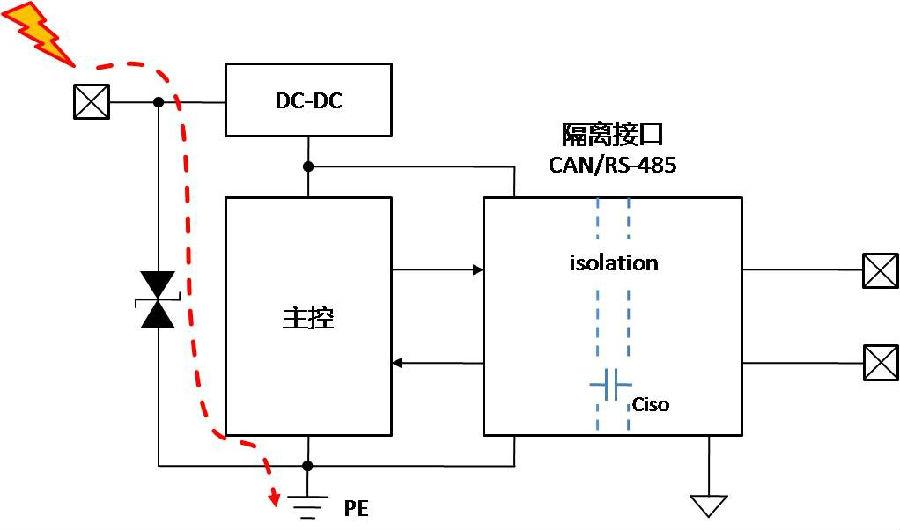

当总线接口受到静电放电时,由于总线侧悬空,能量只能通过隔离栅的等效电容Ciso进行泄放,由于Ciso非常小,仅有几皮法至十几皮法,Ciso被迅速充电,两端电压Viso会非常高,几乎等同于放电电压,如图 3。电压全部施加在隔离接口模块的隔离栅,若电压超出了隔离栅的电压承受范围,则会导致内部隔离栅损坏。

图 3

对于一般的隔离接口模块,隔离栅可承受的静电放电电压只有4kV,对于更高等级的6kV或8kV的静电来说是非常脆弱的,极易出现损坏情况。

改善方法:

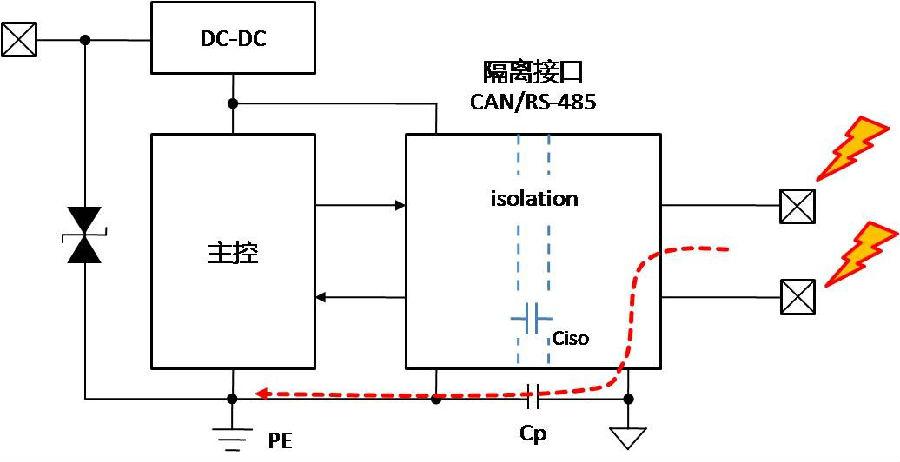

为了减轻隔离栅的压力,可以在隔离栅两边增加一个电容Cp, 为静电能量提供一个低阻抗的路径。如图 4,总线侧的静电能量大部分通过此电容泄放至PE,并可以有效降低隔离栅两侧电压,从而起到保护隔离接口模块的作用。

图 4

为了达到良好效果,Cp容值应远大于Ciso,建议取100pF~1000pF之间。若无安规要求,可与Cp并联一个大阻值泄放电阻,如1M,以防静电积累;若有安规要求,一般需要去除泄放电阻,同时选择安规电容。器件选择时,注意阻容耐压需要满足设备指标要求。

2. 设备控制侧悬空,总线侧有接保护地

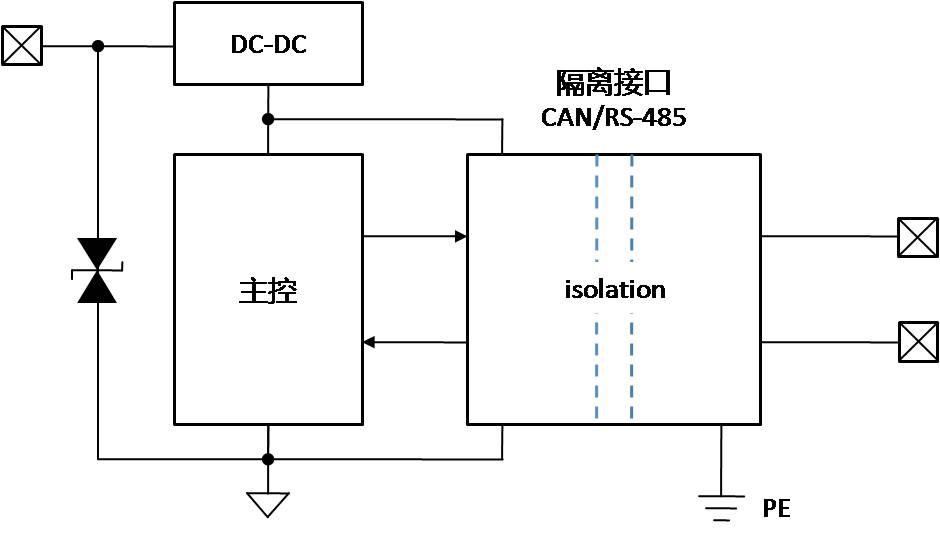

如图 5,此状态下,设备控制侧参考地悬空,与PE无任何连接,总线侧有接入保护地(PE)。

图 5

此状态出现的可能场景:

1. 产品开发测试过程中;

2. 单个产品进行ESD测试时;

3. 设备组网时,总线侧先接地,控制侧未接地时;

4. 设备组网后,控制侧未进行接地处理的。

静电分析:

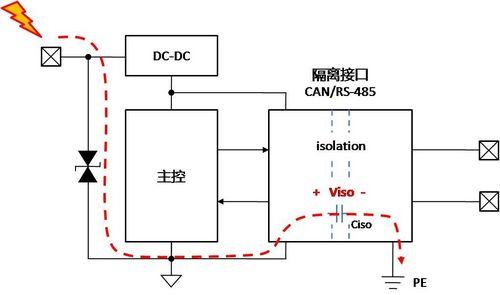

类似的,当控制侧接口受到静电放电时,由于控制侧悬空,能量只能通过隔离栅的等效电容Ciso进行泄放,由于Ciso非常小,两端电压Viso会非常高,如图 6。电压全部施加在隔离接口模块的隔离栅,若电压超出了隔离栅的电压承受范围,则会导致内部隔离栅损坏。

图 6

当总线侧接口受到静电放电时,静电能量通过隔离接口模块内部总线侧器件泄放至PE,如图 7。若ESD能量超出了接口模块内部总线侧器件的ESD抗扰能力,总线接口则可能损坏。

图 7

APP下载

APP下载 登录

登录

热门文章

热门文章