摘要:基于DSP设计了一种采样频率可控的数字锁相放大器。针对数字锁相放大器对低通滤波器性能的要求,采用CIC和降采样的方法,实现了一种高效的窄带低通滤波器。测试结果表明,在采样频率为500 kHz时,低通滤波器的通带截止频率可达0.5 Hz;当输入信号幅度为5~150 mV时,系统测试的相对误差小于0.5%;当输入信号幅度为1~50μV时,系统测试的相对误差小于2%;同时系统在1~120 kHz的工作范围内,具有较好的一致性。

关键词:锁相放大器;采样率;积分梳状滤波器;降采样

0 引言

弱信号检测一直是测量领域的重点研究问题。锁相放大器是一种能够检测微弱周期信号的精密仪器。它利用相关检测的方法,能够测量μV(甚至nV)量级信号的幅度和相位,并且具有极强的抗干扰能力,因而在很多测量领域(如电学、光学、热学及生物学等)得到了广泛的应用。早期的锁相放大器都是基于模拟电路设计的。由于模拟器件在带宽、温漂、直流偏置以及器件老化等方面的限制,模拟锁相放大器在测量精度、测量稳定性和抗噪声能力等方面均受到很大的限制;数字锁相放大器通过数字信号处理器(Digital Signal Processor,DSP),将模拟信号转换到数字域进行检测和处理,具有动态范围大,测量误差小,不受运放温漂和偏置影响等优势。近年来随着数字信号处理器的飞速发展,模拟锁相放大器逐渐被数字锁相放大器所取代。本文对数字锁相放大器的硬件结构和相关算法进行了研究,设计了一种采样频率可控的系统结构,并利用积分梳状滤波器和降采样的方法实现了高效的窄带低通滤波器,满足了系统实时性要求。测试结果表明,该系统能够达到较高的测试精度。

1 数字锁相放大器的基本原理

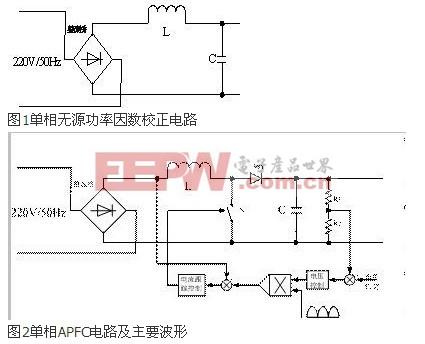

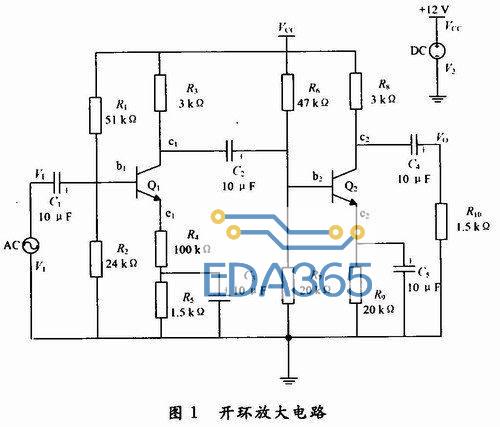

数字锁相放大器利用输入信号与参考信号的相关性、待测信号与噪声的互不相关性来完成测量。其基本原理如图1所示。

将输入信号定义为:

X(t)=Asin(ωt+φ)+n(t) (1)

式中:A为输入信号的幅度;ω是输入信号的角频率;φ是输入信号的相位;n(t)是输入信号中混入的噪声(噪声强度可以远大于信号强度)。参考信号由两路相互正交的正弦信号构成。输入信号和两路正交的参考信号相乘之后,对应的输出分别为:

将两路输出信号各经过一个理想的低通滤波器后,二倍频和噪声成分都会被滤除,此时两路的输出分别为:

由以上分析可知,数字锁相放大器实际上是利用一个低通滤波器,实现了中心频率为ω的带通滤波器。低通滤波器的带宽越窄,相应地,带通滤波器的带宽也越窄,滤除噪声的能力也越强。低通滤波器的截止频率决定了系统的抗噪声能力,通带内波动决定了输出的稳定性。由于系统对线性相位的要求,滤波器需采用FIR型低通滤波器来实现。而采用传统的单级FIR滤波器来实现窄带低通滤波器需要很高的阶数,运算量较大,难以实时实现,并且滤波性能易受滤波器系数的影响。低通滤波器的性能好坏,直接决定着数字锁相放大器滤除噪声的能力。如何设计和实现高性能的低通滤波,是影响数字锁相放大器性能的关键。

2 数字锁相放大器的结构设计

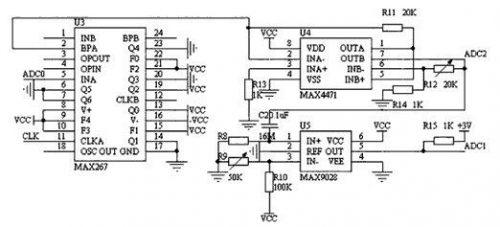

微控制器采用了德州仪器(Texas Instrument,TI)公司的MSP430F149,其主要功能包括系统控制和状态检测。待测的输入信号经过放大、滤波后进入ADC。其中,ADC的采样速度决定了系统能够测试信号的最高频率。本系统采用了TI公司的AD8329,这是一款16 b的高精度串行模/数转换器,最高采样速率可达1 MSPS。

为了防止ADC的转换数据丢失,系统必须对采集到的大量数据进行实时处理。数字锁相放大器的实时性对数字信号处理器的速度提出了很高的要求。虽然目前市场上主流的定点和浮点DSP器件的数据处理速度相比以前有了很大提升,但是它仍然是制约数字锁相放大器测量频率范围进一步增加的主要原因。为了降低系统对DSP处理速度的要求,提高检测的最高频率,一些系统甚至将DSP的部分功能通过外围电路来实现,比如采用中心频率可控的模拟滤波器来滤除输入信号的带外噪声,利用FIFO结合CPLD来缓冲ADC数据等。这些方法虽然减轻了DSP的运算负荷,但是也增加了系统的硬件成本和复杂度。

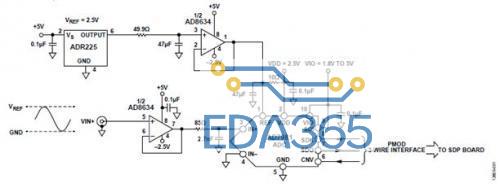

本系统以TI公司的TMS320VC5502为核心,设计了一种采样频率可控的数字锁相放大器,不仅满足了系统实时性的要求,简化了系统结构,而且具有较好的准确度和稳定性。数字部分接口示意图如图2所示。

TMS320VC5502的片上定时器Timer0配置成输出工作方式,产生频率恒定的脉冲信号。此脉冲信号作为模/数转换器采样开始的控制信号。采样频率可由定时器产生脉冲的频率来控制;多通道缓冲串口(Multichannel Buffered Serial Port,McBSP)被配置成SPI模式,用于控制命令的发送和采样数据的接收。ADS8329的转换结束信号作为DSP的外部中断。采样数据的接收和存储、控制命令发送以及对ADC转换结束的响应均采用DMA控制器来完成,这样不但保证了采样数据的完整性,而且DSP可以专注计算而不被外部事务频繁中断,极大地提高了DSP的运算效率。

为了保持采样数据的连续性,并防止原有数据被新数据覆盖,系统在DSP内部开辟了两块长为1024×16 b的缓冲区,用于暂时存放ADC的采样数据。两块缓冲区交替存储和计算,以保证系统的实时性。当ADC的转换结果向缓冲区A存放时,系统处理缓冲区B中的数据;当转换结果向缓冲区B存放时,系统处理缓冲区A中数据。其数据流图如图3所示。

假设系统的采样率为fs,每块缓冲区的长度为N(本系统为1 024×16 b),处理每块缓冲区数据所需的时间为TCAL。若三者满足TCAL Nfs,则系统可以实现实时处理。测试证明,本系统最高采样速率可达640 kHz。

APP下载

APP下载 登录

登录

热门文章

热门文章