2. 与其它出口方法相比,DPD收敛性得到改善,因为在所有DPD工作条件下都可以利用转换器的全部分辨率。

3. DPD环路可以立即响应峰值状况,因为在DPD工作条件下可以利用转换器的全部范围和带宽。

出口管制使得只有某些国家和地区才能使用数据转换器。然而,日益壮大的商用电信市场要求利用更快速、更高分辨率的转换器技术来构建这些平台,尤其是针对功率放大器的数字预失真。这种应用会测量并以数字方式校正非线性误差,使得总体交调性能显著优于内核信号链,同时提升放大器效率。根据实施和系统要求,在某些新型放大器拓扑结构中,末端邻道功率比(ACPR)可以达到80 dB至85 dB,效率接近50%。

典型DPD应用

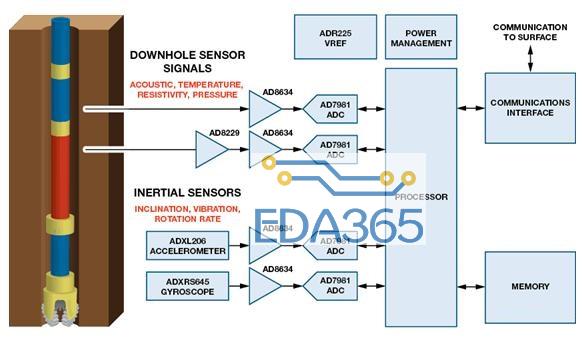

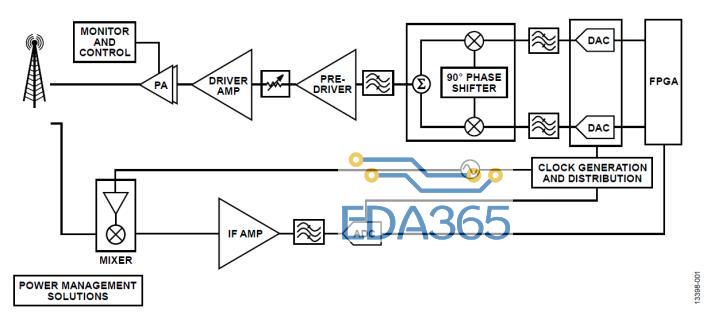

图1所示为一个典型DPD应用。虽未显示,但零中频(ZIF)和复中频(CIF)采样架构也很常见。典型的发射机输出包括20 MHz到100 MHz范围的有用信号信息,但新设计已经能够支持100 MHz以上的带宽。

除了有用信号信息之外,发射机还会产生相当多的谐波和交调产物。令此类线性度问题进一步加剧的是,PA设计通常是针对效率而优化,因而线性度会有所牺牲。不过,总体直流效率为33%是很常见的,也就是说直流功率是输出RF功率的3倍。这意味着对于50 W输出,要消耗150 W功率。较新的设计在向50%的效率目标前进,这说明核心放大器的交调会更差。

为使总线性度处于可接受水平,并使杂散处于邻带之外,通常利用数字技术让基带信号发生预失真(Morgan、Ma、Kim、Zierdt和Pastalan,“RF功率放大器数字预失真的一般存储器多项式模型”,IEEE信号处理学报,第54卷第10期,2006年10月),即寻求对发射数据进行建模并产生反失真,使得最终频谱显著优于核心放大器本身。

图1. 典型DPD系统图

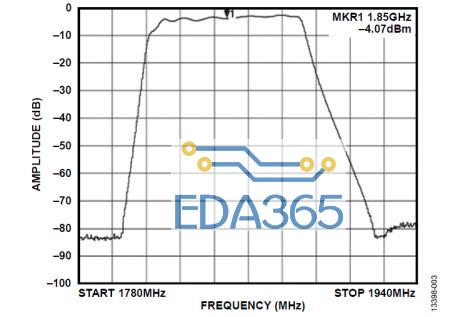

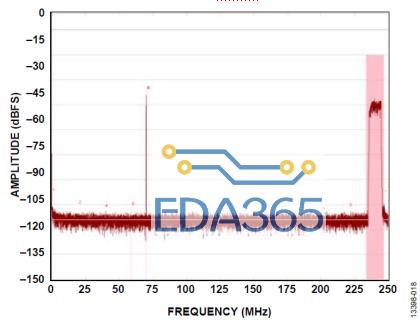

典型PA输出

图3. 典型发射滤波器响应

核心ADC要求

DPD应用的ADC有三个基本要求:采样速率、无杂散动态范围(SFDR)和信噪比(SNR)。SNR也可表示为有效位数(ENOB)。

转换器的采样速率决定可以校正的带宽。给定带宽时,经常引用奈奎斯特准则作为要求来确定采样速率。如果带宽须为x,则奈奎斯特准则规定:采样速率须为2x。还有其它现实考量。涉及到模拟滤波时,该比率会扩大到3倍以确保滤波滚降不是过于困难。不过,除了双工器,许多DPD应用仅使用非常少的滤波,以降低对群延迟的影响。另外,有非常广泛的DPD相关知识产权(IP)可供使用。许多IP可有效降低采样速率要求,常常绕过奈奎斯特要求。但是,超宽带宽的模拟信号仍然需要非常高的采样速率。

对于SFDR,反馈观测路径的典型性能必须比系统目标性能好很多。通常,转换器应当比发射机输出高出10 dB到15 dB。对于MC-GSM,性能目标通常是三阶项60 dB,五阶项70 dB。为了不使结果发生偏离,观测路径必须为这些项分别提供75 dB到85 dB的性能。虽然3G和4G平台的目标可能相对较低,但期望的性能水平仍然相似,以便确保校正稳定可靠。

在典型的DPD环路中,噪声与环路收敛性直接相关。噪底越高,环路收敛所需的时间越长。相反,噪底越低,就能越快地达到收敛。由于必须满足监管要求并使带外能量最小化,系统设计人员设计的系统必须尽可能快地响应带外信号,因此要用环路响应换取转换器分辨率。

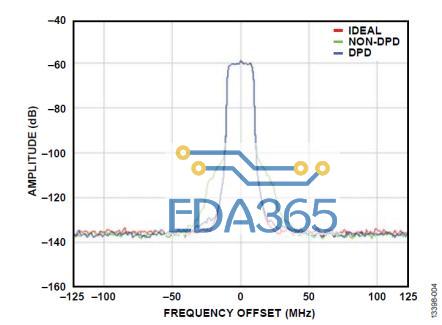

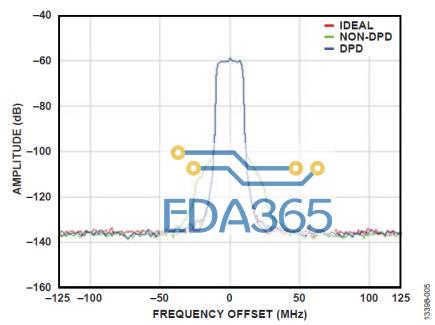

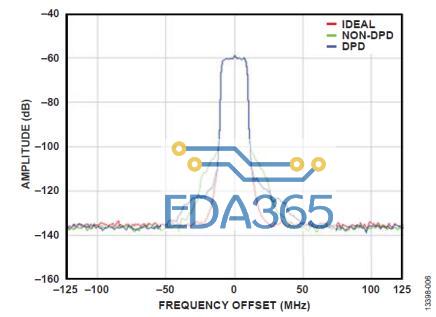

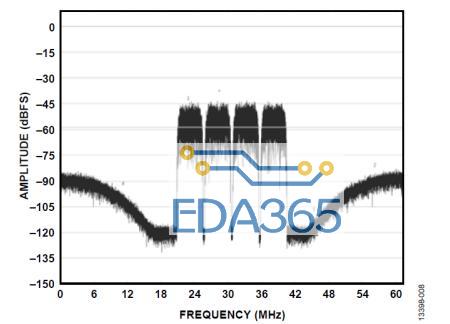

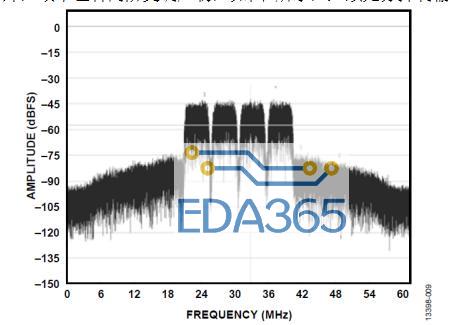

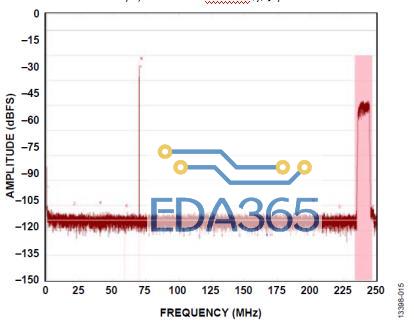

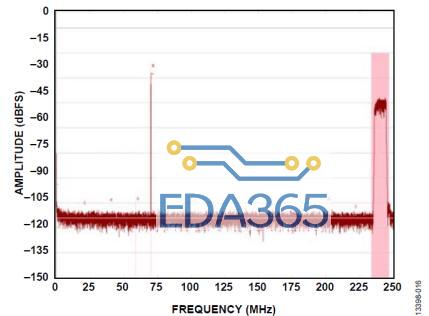

图4、图5、图6和图7展示了这一概念。图4和图5分别代表9位和14位转换器,其中环路的收敛是通过对反馈路径中的信息缓慢积分实现的。可以看出,对于慢速环路,9位和14位的收敛速率几乎无差异。

图4. 慢速环路的9位转换器

图5. 慢速环路的14位转换器

图6. 快速环路的9位转换器

图7. 快速环路的14位转换器

传统技术

由上一部分可知,采样速率、分辨率和线性度都是大多数DPD应用的重要因素。出口器件所用的许多技术都以这样或那样的方式限制了这些方面。

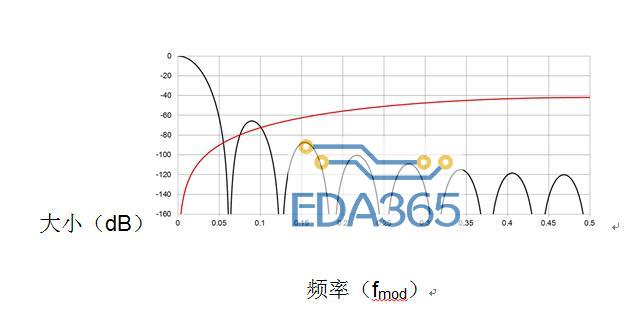

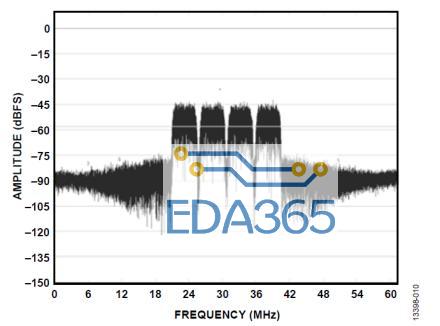

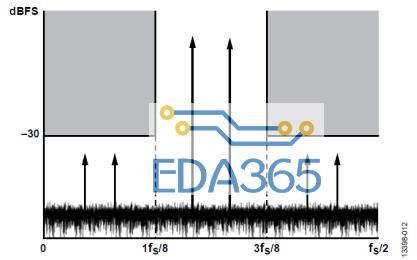

最常见的技术之一是噪声整形,即对数字数据进行噪声整形,使带内噪声移动到主要目标频段之外的区域,如图8所示。噪声整形通常是针对接收机的主要功能进行,其中主频段之外的信息主要由带外阻塞信息构成。

图8. FFT中的噪声整形

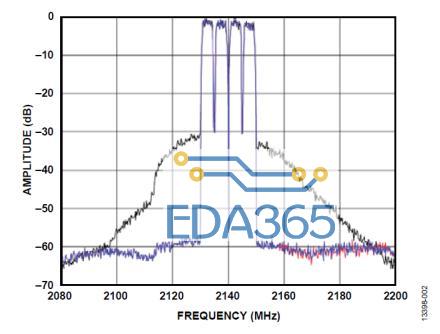

然而,对于DPD应用,该带外区域中包含高阶交调产物,如图9所示,必须充分抑制输出频谱中的这些产物。

图9. 输出频谱中的交调产物

若将噪声整形用于DPD应用,这些交调产物将变得模糊不清,难以理解。因此,噪声整形不适合DPD应用。

图10. 噪声整形使交调产物模糊不清

专用解决方案

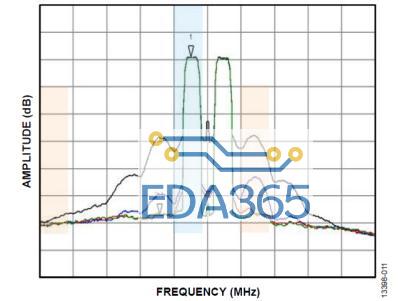

仔细研究DPD应用可发现潜在解决方案的线索。图11显示了DPD环路的典型表现。一开始,PA输出未经校正,交调产物可能相当大。当环路收敛时,交调产物逐渐减少,接近一个由初始误差和校正算法精密性决定的较低限值。典型DPD环路收敛如图11中的系列曲线所示。通过分析初始条件和收敛过程,可以找出几个关键点。

第一,总功率由多个载波分享。ACPR通常是相对于其中一个信号测量,而不是相对于总功率测量(尽管它们彼此相随)。因此,相对于满量程而言,每次载波数加倍,相对于满量程的ACPR就会降低3 dB。

第二,复合信号表现出某一峰值-均方根比值。对于原始数据,根据信号统计特性,它可以达到13 dB或更高。然而,为使功率放大器效率最高,多数系统会进行某种形式的波峰因数削减或幅度压缩,以便实现更高的均方根功率输出,同时PA不至于过度压缩。对ADC核心的动态范围要求同样得到降低。压缩后峰值与均方根之比的舍入值在6 dB左右。压缩过多对信号质量不利,可能会破坏星座并提高误差矢量幅度。

将峰值均方根比和ACPR合并,得到交调典型值为−31 dBFS。多数系统会增加一些余量和倒退,以防止削波和支持其它变化。此信息可用来构建未校正PA输出的信号模型,如图11所示。该图显示了两类区域:一类由所需信号构成,显示为突出的内部最大信号;另一类为交调产物,显示在外部区域。

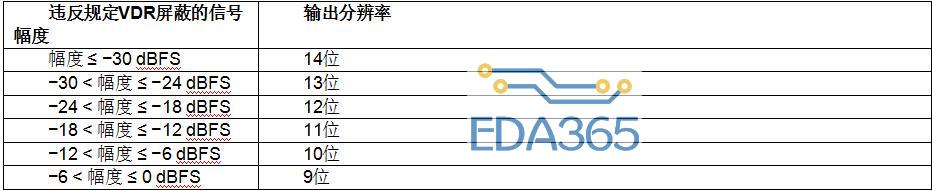

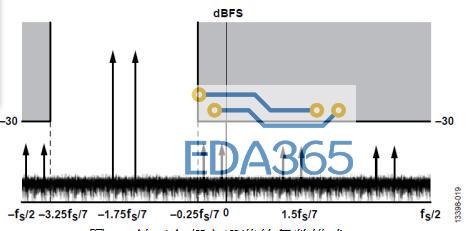

具有最大分辨率的接收机即便未经校正,也能很好地改善收敛和性能。如果交调产物延伸到图12所示典型通用DPD模型所定义的屏蔽区以上,则必须降低接收机的分辨率以便符合出口管制规定。否则,应用就能获得全部分辨率。

可变动态范围

配有可变动态范围(VDR)的接收机可为所述应用提供全部转换器分辨率、采样速率和动态范围。核心转换器性能不受任何影响,除了在与DPD应用无关的条件下可能会改变分辨率以外。核心转换器数据并不直接经过任何类型的滤波,因此对带宽、群延迟和延时无影响。原始信号完整度得以完全保留。

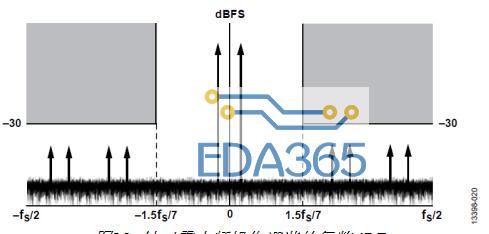

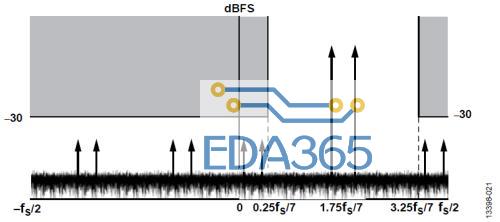

VDR对实数和复数信号链均适用。在实数接收机架构中实施时,主信号区定义为采样速率的25%。在复数接收机架构中,主信号区可定义为采样速率的25%或43%。此区仅是有效载波的区间。交调产物可落在此百分比以外,ADC性能不受影响。

图12给出了一个简化的说明。白色背景中显示的中央区域就是放置PA输出信号的地方。交调产物落在外边的区域中。只要交调产物低于红色屏蔽区,接收机便可提供全部分辨率。

图13至图18说明了DPD环路收敛时会发生什么。图13显示了交调高达6 dBFS时的噪底。图14至图18显示了环路收敛和交调产物下降时发生的事情。虽然图中的变化很细微,但噪底从开始时的−149 dBFS/Hz经过一系列步骤后降至−153 dBFS/Hz。

图13. −6 dBFS带外

图14. −12 dBFS带外

图15. −18 dBFS带外

图16. −24 dBFS带外

图17. −30 dBFS带外

图19显示VDR调谐到DC的负侧,这对在观测路径中实现复中频并产生负中频的应用是有用的。

图20. 针对零中频操作调谐的复数VDR

图20显示VDR调谐至DC,这对实现零中频观测路径的应用是有用的。

图21. 针对正频率调谐的复数模式VDR

VDR实际应用

VDR对数字预失真环路的影响很小或几乎没有。针对VDR创建的窗口与当前DPD应用重叠,这样几乎在所有条件下,包括大多数预收敛状态,都可以向处理器模块呈现全部分辨率。

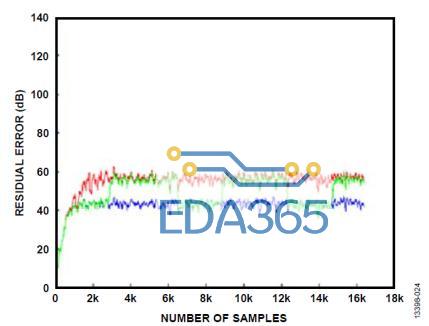

随着系统收敛,转换器的分辨率会增加。当交调产物低于−6 dBFS时,提供10位分辨率;低于−12 dBFS时,提供11位分辨率;低于−18 dBFS时,提供12位分辨率;低于−24 dBFS时,提供13位分辨率;最后,低于−30 dBFS时,提供全部分辨率。

每种情况下,交调产物与转换器噪底之间都有很大的裕量,收敛不会受到限制。图13至图18粗略显示了这些情况。

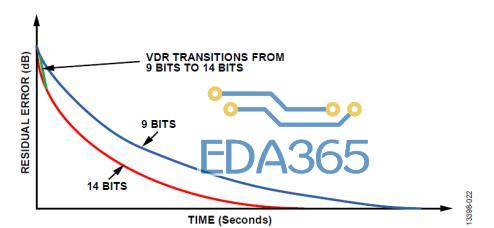

如上所述,分辨率在很大程度上决定了环路的收敛速度。对于通用算法,这种关系如图22所示。有几个关键点需要注意。第一,分辨率越低,收敛得越慢。第二,在收敛开始时,曲线斜率的差异非常小,意味着对于前几个样本,分辨率实际上无足轻重。

图22. 9位和14位分辨率的残留误差与时间的关系

在最差情况下,最初可能是遵循9位曲线。然而,其斜率相当高,在曲线的此区域几乎无区别,并且很快就会提供更高的分辨率。

对于用到每个数据样本的应用,例如OP6180,VDR在短至四个转换器样本的时间内提供全部分辨率。在提供块处理的应用中,全部分辨率出现在首次迭代之后。对于这两类应用,斜率均从9位过渡到14位,使DPD环路加速,从而改善收敛时间。在典型情况下,VDR从一开始便提供全部分辨率,因为哪怕是收敛程度最低的PA,所定义的VDR屏蔽区也允许其以全部分辨率输出。

此外,VDR支持稀疏事件。屏蔽是基于FIR滤波器,降低接收机分辨率的非频发事件会被滤波消除。因此,VDR提供几乎100%的高分辨率模式运行,改善收敛性能,如图22所示。

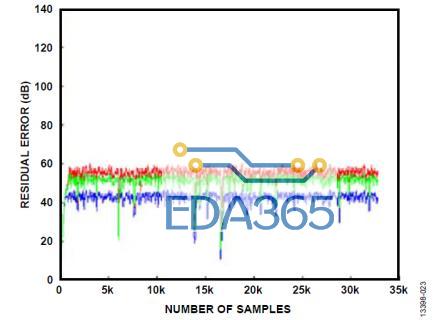

由于VDR使得高分辨率模式下的运行比例非常高,所以整体DPD性能大大高于低分辨率系统。图23显示了该性能,其反映的是残留误差。蓝线(最下方的曲线)显示9位残留误差,红线(最上方的曲线)显示14位残留误差。由于高分辨率操作的残留误差更低,因此整体收敛更佳,图6和图7清楚地显示了该差异。

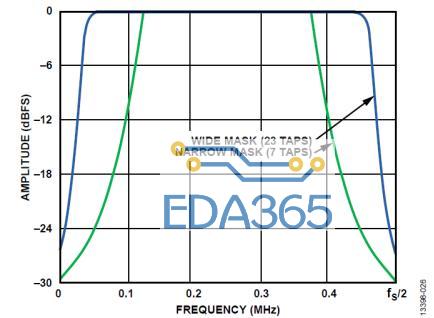

图24显示了一个VDR从高分辨率变为低分辨率的实例。这个极端例子说明了残留误差随分辨率变化的关系。需要注意的一个关键点是:当分辨率改变时,典型环路不得失稳。事实上,必须保证大多数交调事件不会破坏高分辨率性能。从屏蔽角度看,VDR有两个滤波器可供选择:一个是7抽头长,另一个是23抽头长。所需的抽头数由外部模拟滤波器阶跃响应控制。

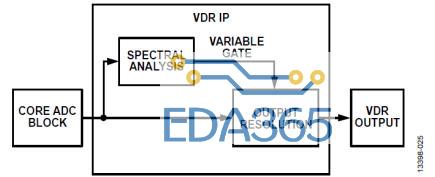

如图25所示,频谱屏蔽不在主信号路径上。上文已提到,数字滤波器并不直接影响输出数据。数字滤波器仅用于对数据执行频谱分析,然后将响应与表1所示的阈值比较,确定使用何种输出分辨率。

图25. VDR信号流程图

结果,当频谱成分落在两个已定义屏蔽区之一以内时,便会提供转换器的全部动态范围,如图26所示。图中显示,宽带屏蔽区覆盖大部分(86%)的奈奎斯特频段,并且完全可调,因为在其内部,数据是作为复数进行处理。所有信号,包括交调产物在内,只要落在此屏蔽区内,便会提供转换器的全部动态范围。如图26所示,在几乎所有情况下,转换器性能都达到最高。即使信号落在屏蔽区过渡带中的14%频谱以内,它也必须高于屏蔽区,转换器的分辨率才会降低。

图26. 宽和窄VDR屏蔽区

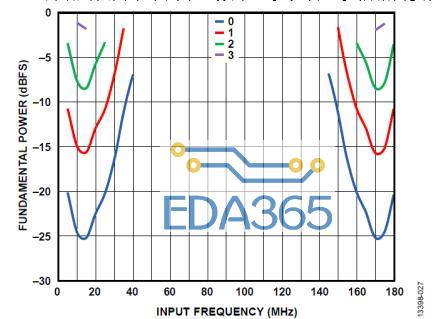

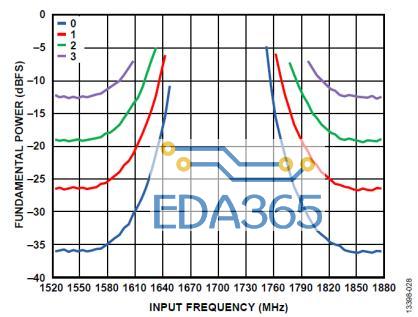

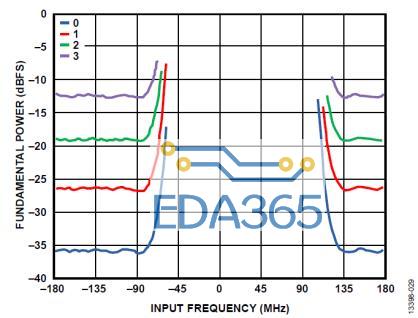

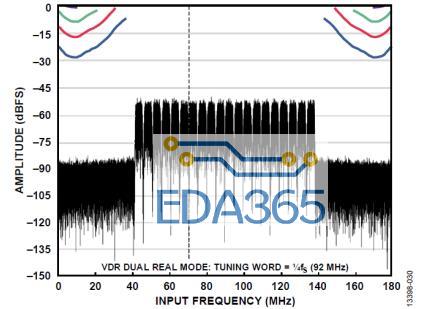

为了更直观地理解这一点,通过扫描模拟输入的频率和幅度,对器件进行了测定,如图27至图29所示。分辨率曲线代表激励信号的最终分辨率。图27所示为实数工作模式的例子,图28和图29为复数工作模式的例子。在这些示例中,采样速率设置为常用值368.64 MSPS。在图27和图28中,VDR调谐到中带。所示的第三次扫描是在复数模式下采用宽带滤波器模式。这种情况下,VDR调谐到偏离中带的中心频率,以说明可以根据需要偏移IF。

图27. VDR实数模式下的频率扫描

图28和图29是针对复数操作,采用完全相同的过程。窄带模式同样提供100 MHz的清晰频谱。在图30所示的宽带复数模式中,提供大约160 MHz的受保护频谱,这适合时分双工(TDD)应用。

图28. VDR复数模式下的频率扫描(窄带屏蔽)

图29. VDR复数模式下的频率扫描(宽带屏蔽)

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多