使用

图1. ADCLK925的均方根抖动与输入压摆率的关系

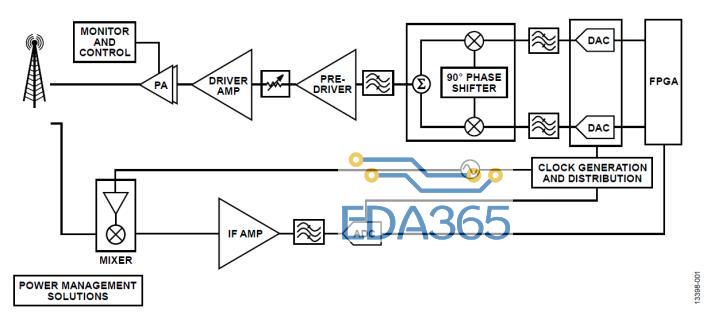

ADCLK9542时钟扇出缓冲器和ADCLK9143超快时钟缓冲器就是两款此类时钟分配器件。ADCLK954包括12个输出驱动,可以在50-Ω的负载上驱动全摆幅为800-mV 的ECL(发射极耦合逻辑)或者LVPECL(低压正ECL)信号,形成1.6 V的总差分输出摆幅,如图2所示。它可以在4.8 GHz反转率下工作。ADCLK914可以在50Ω负载上驱动1.9 V高压差分信号(HVDS),形成3.8 V的总差分输出摆幅。ADCLK914具有7.5-GHz的反转率。本文来自电子发烧友网(http://www.elecfans.com)

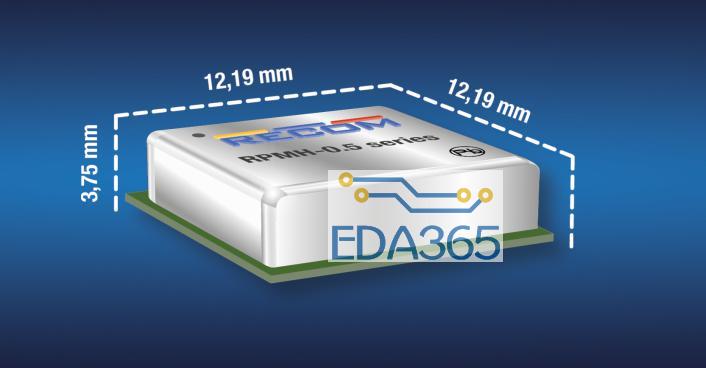

当驱动DAC时,时钟分配器件应该尽可能靠近DAC的时钟输入放置,这样,所需的高压摆率、高幅度时钟信号才不会引起布线困难、产生EMI或由电介质和其它损耗造成减弱。值得注意的是,走线的特性阻抗(Z0)会随走线尺寸(长度、宽度和深度)而变化;驱动器的输出阻抗必须与特性阻抗匹配。

图2. 采用3.3V电源供电时ADCLK954时钟缓冲器的输出波形

输出端接

时钟信号衰减会增加抖动,因此对驱动器输出的端接很重要,这可以避免信号反射,并可通过相对较大的带宽实现最大能量传输。确实,反射可以造成下冲和过冲,严重降低信号和整体时钟的性能,或者在极端情况下,可能会损坏接收器或驱动器。反射因阻抗不匹配而引起,在走线没有适当端接时发生。由于反射系数本身具有高通特性,因此这对具有快速上升和下降时间的高速信号更重要。反射脉冲与主时钟信号相叠加,削弱了时钟脉冲。如图3所示,它对上升沿和下降沿增加了不确定的延时或者抖动,从而影响时钟信号的边沿。

图3. 由端接不当引起的反射信号抖动

端接不当使回声的幅度随着时间而变化,因此∆t也会随时间变化。端接的时间常数也会影响回声脉冲的形状和宽度。基于以上原因,反射引起的附加抖动,从形状看类似增加经典抖动的高斯特性。为了避免抖动和时钟质量降低的不利影响,需要使用表1中总结的恰当信号端接方法。Z0是传输线的阻抗;ZOUT 是驱动器的输出阻抗,ZIN 是接收器的输入阻抗。仅显示CMOS和PECL/LVPECL电路。

表1. 时钟端接

方法描述优势弱点备注

串行端接CMOS

很容易计算R的值 R (Z0 – ZOUT).上升/下降时间受RC电路的影响,增加抖动。

只对低频信号有效。CMOS驱动器

不适合高频时钟CMOS drivers.信号。

适合低频时钟信号和非常短的走线。

下拉电阻CMOS

非常简单(R = Z0)高功耗不推荐

LVPECL

简单的3电阻解决方案。

就节能而言稍好一点,相对于4电阻端接来说节省一个电阻。 推荐。

端接电阻尽可能靠近PECL接收器放置。

交流端接CMOS

没有直流功耗。 为避免较高功耗,C应该很小,但也不能太小而导致吸电流

LVPECL

交流耦合允许调整偏置电压。避免电路两端之间的能量流动。交流耦合只推荐用于平衡信号(50%占空比的时钟信号)。交流耦合电容的ESR值和容值应该很低。

电阻桥CMOS

功耗实现合理的权衡取舍。单端时钟用两个器件。

LVPECL

差分输出逻辑用4个外部器件。3.3V LVPECL驱动器广泛应用端接。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多