系统级单芯片(SoC)的功能整合由IP区块转向一个个实体小芯片(Chiplet)的技术,是近来被热烈讨论的话题;而从刚落幕不久的2021年度(以虚拟形式举行)的国际固态电路会议(ISSCC)上有一整场论坛聚焦于Chiplet,更可以看出这种新设计典范受重视的程度。

在ISSCC的Chiplet论坛上总共有8场聚焦该技术的简报,其中有三场提供了市面上已有之系统成果、技术趋势的概况介绍,以及加速这种新设计方法必备的产业生态系。

AMD最新系列微处理器就是以采用Chiplet方法优化其设计,并为芯片选择最适合的技术节点而闻名。AMD资深副总裁、研究员暨产品技术架构师Sam Naffziger在ISSCC详细介绍了该公司采用Chiplet的动机(主因是晶圆工艺节点的进展速度减缓),以及将处理器功能区块分解为分别适合先进工艺节点与较成熟工艺节点的特制切片之挑战所在。

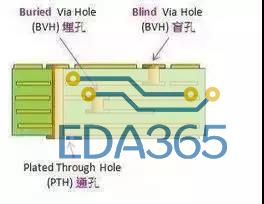

Naffziger的案例研究分享是EPYC服务器处理器的开发;他指出,以多芯片组合电路的方法不是全新的,在以往业界曾采用陶瓷基板制作多芯片模块(MCM),后来又转向采用有机基板;“摩尔定律走向终结,再加上封装技术的演进,开创了多芯片/Chiplet方法的新时代。”

对AMD来说,Chiplet最大的“卖点”在于能改善单颗良品裸晶的成本,较高良率是较小尺寸芯片的天生优势,因此AMD向晶圆代工业者采购的每一片晶圆最后会有较少的故障裸晶。大尺寸裸晶上任何一个地方出现缺陷都会是致命伤,若将之分为四颗小的,其中一颗故障还能有三颗可以出货的产品,而不是一整颗大芯片报废。

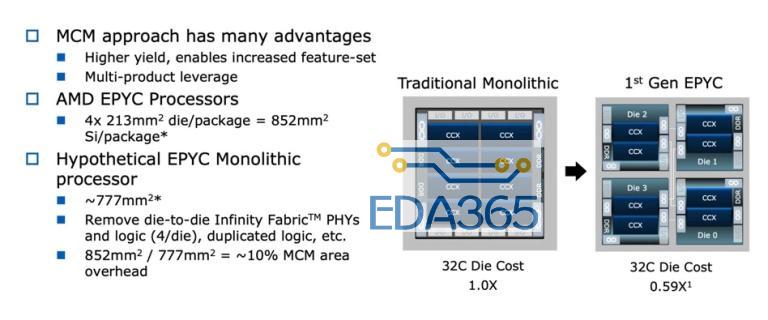

Naffziger表示,将单芯片设计改为MCM型态,一开始的自然想法可能会是在第一代设计时,得为额外硅晶圆面积付出高昂代价。其实不是这样。

AMD计算出,以Chiplet方法制作EPYC处理器时,会需要比单一芯片多出10%的硅晶圆面积做为裸晶对裸晶的通讯功能区块、冗余逻辑(redundant logic)以及其他附加功能,但最后整个Chiplet形式处理器的芯片成本,比单芯片处理器节省了41%。能节省40%硅晶圆成本似乎是很难仿效的艰难任务;那么第二代的EPYC产品又达到了甚么成就?

AMD采用Chiplet方法制作的第一代EPYC处理器,在成本上比单颗芯片更低。(图片来源:ISSCC 2021)

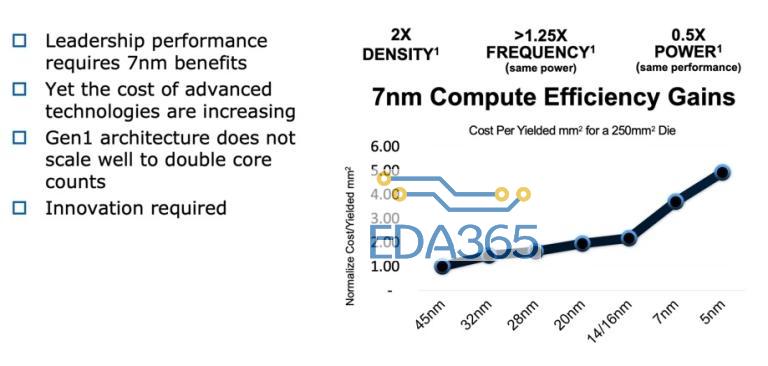

尽管摩尔定律趋缓带来了许多挑战,AMD与其他高性能运算(HPC)业者仍意识到,市场领导地位仍需要采用最尖端的工艺技术,但最新工艺节点的高昂成本是一个严重问题,在技术演进至14/16纳米以后,该趋势更是急遽升高。

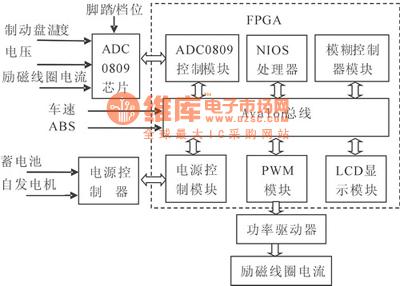

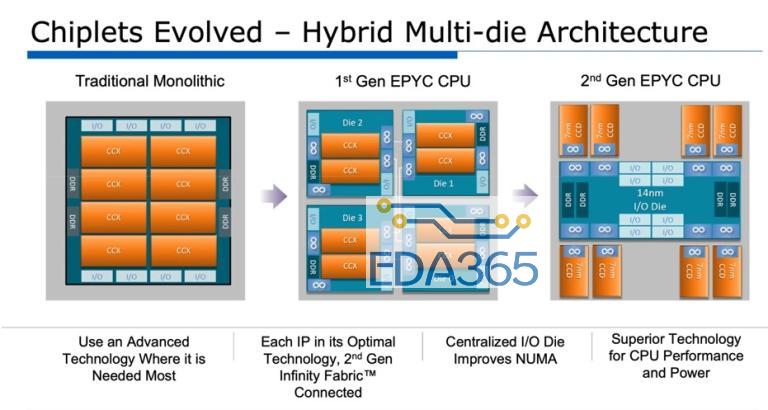

幸好Chiplet解决方案提供了在成本与性能上的优化。AMD将EPYC设计分成多个部份,让CPU功能采用最新7纳米节点,模拟与I/O功能区块则使用不那么先进的技术。这是非常合理的作法,因为模拟电路无法获益于晶体管或导线间距的微缩;更引人注意的是,与数字电路相较,传递讯号的I/O本身凸块间距微缩进展相当缓慢。

AMD计算每颗良品裸晶面积晶圆成本。(图片来源:ISSCC 2021)

第二代EPYC运算复合芯片(compute complex die,CCD)有86%面积为CPU与L3 SRAM内存,这似乎是对更昂贵之7纳米技术非常有效益的运用。模拟与I/O是高性能桌上型PC与服务器处理器设计中很重要的部份,这一点从EPYC 2产品有相当大的I/O裸晶(IOD)就明显可以看出;这类芯片可容纳大量串行数据如PCIe (在EPYC 2上有128信道)与DDR信道。

AMD在EPYC上采用的Chiplet技术演进。(图片来源:ISSCC 2021)

Chiplet解决了芯片设计上的一个问题,同时也带来新的挑战──怎么“切”芯片就是首先会遇到的难题;要在一片封装基板上链接9颗“小芯片”,是一个大工程。不过,将EPYC 2推向真正“混搭”Chiplet设计所付出的努力,是有所回报的。

AMD的设计具备采用较便宜14纳米工艺技术的IOD,支持完整产品的核心数与性能,但成本更低,以24到48核心的处理器来说,成本只有单芯片的一半。AMD指出,较大的核心产品甚至不能以单芯片形式实现;从这些结果来看,Chiplet其实是无可替代的唯一前进途径。

展望未来,Naffziger看到了一些减少连结开销的可能性,像是减少中介层(interposer)与更密集互连、直接在运算裸晶上堆栈内存,以及超越只有内存裸晶的真正3D堆栈。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多