遥测数据处理系统在航空、航天等军工试验领域有着广泛的应用。在航空飞行试验中.遥测数据处理系统为各类试飞测试数据的实时处理提供了手段和平台,是试飞员、试飞指挥员及试飞工程师协同完成新机试飞必不可少的重要设施,是确保现代飞机试飞安全、提高试飞效率、缩短试飞周期、实现综合试飞的重要手段。

遥测数据处理系统中的核心设备——遥测前端处理器,技术上经历了从分立式、智能式到嵌入式的快速发展。我国遥测前端处理器的研发经历了从引进、合作研制到完全自行研制的历程。

遥测前端处理器是一套嵌入式实时计算机系统,承担着遥测PCM数据的同步、分路、工程单位转换、数据计算、数据分配等实时处理任务。它和遥测系统管理服务器、工作站等设备通过网络联接和系统集成,组成当前流行的基于C/S结构的遥测数据处理系统。可以说,遥测前端处理器的技术水平代表了遥测数据处理系统的技术水平。

1 系统功能和主要技术指标

遥测前端处理器的功能简单地说,就是把来自遥测接收设备送来的多路串行PCM(Pulse Code Modulation)数据流进行同步、分路、合并、存储,并对转换后的并行数据进行工程单位转换、导出参数计算等实时处理,通过网络把数据传送给显示工作站。再通过遥测记录数据重放,为用户提供同实时方式一样的处理功能和更为详细的数据分析功能。

遥测前端处理器主要技术指标为:

(1)可同时完成2路PCM数据流的同步和分路,每路PCM速率不大于20Mbps。

(2)实时数据处理速率:20Mbps。

(3)数据传输:交换式以太网、网络带宽1000Mbps、广播方式和“点对点”方式。

(4)数据存储:满足在最大速率下数据存储不丢失,磁盘容量满足不小于4小时的记录时间。

(5)D/A输出:12位、16路模拟信号输出。

2 系统组成和体系结构设计

二十世纪90年代,因受当时的计算机技术限制,国内外大多数嵌入式遥测前端处理器都采用了基于VME总线的计算机平台和双总线、多CPU、百兆以太网接口的体系结构,其技术复杂、成本高、软件开发难度大、系统研制周期长。

当前计算机技术的发展,使得CPU速度和总线速率已不再是新一代嵌入式遥测前端处理器的瓶颈,基于单CPU、单总线和千兆以太网接口的体系结构成为新一代嵌入式遥测前端处理器的主流设计。板卡化后的遥测前端设备,如码同步器、分路器、时码发生器等作为计算机的一个插件板,嵌人到工业计算机系统中,其组成已简化为:19英寸计算机箱、CPU板、多功能PCM分路器板、时码板、D/A板和存储设备,其典型结构与组成见图1所示。新一代嵌入式遥测前端处理器体系结构简化,性能和可靠性提高,成本降低,研制周期缩短,更容易集成为基于C/S结构的多数据流遥测数据处理系统。

3 硬件设计

3.1 总线平台和OEM板卡的选择

计算机总线平台是嵌入式遥测前端处理器的关键,当前国外嵌入式遥测前端处理器均选用了目前流行的Compact PCI计算机总线平台。该平台吸收了PC机商用技术的最新成果,数据传输速率满足新一代嵌入式遥测前端处理器实时处理多条PCM数据流时的传输要求,环境条件、可靠性等都满足运输类飞机机载、地面活动车载等环境使用要求。

遥测前端处理器中的其他硬件,除PCM分路器板外,均选用了OEM产品。机箱选用12槽Compact PCI机箱(包括电源组件和磁盘);根据处理要求,本设计的CPU板选用了美国SBS公司的C7系列,CPU PⅢ1GHz,RAM 1GB,2个1000Mb以太网口,1个SCSI口。时码板选用了美国DATUM公司带GPS授时的BC637;D/A板选用了美国NI公司的 N16713系列,每板8通道.每通道lMSps,D/A分辨率为12位。

考虑到单片式全数字码同步器在国外已有使用,因此在多功能双PCM分路器板设计时已预留了单片码同步器的芯片位置。本设计码同步器选用外置式码同步器。

3.2 多功能双PCM分路器板的设计与实现

PCM 分路器板是嵌入式遥测前端处理器的关键插件,国外也有不少单板、单PCM分路的OEM产品。但高端产品的购置受到西方国家诸多限制,因此,选取了自行设计的技术途经,研制成功了基于Compact PCI总线的多功能双路。PCM分路器板,其技术水平达到当前国际先进水平。

3.2.1 PCM分路器板的硬件逻辑设计

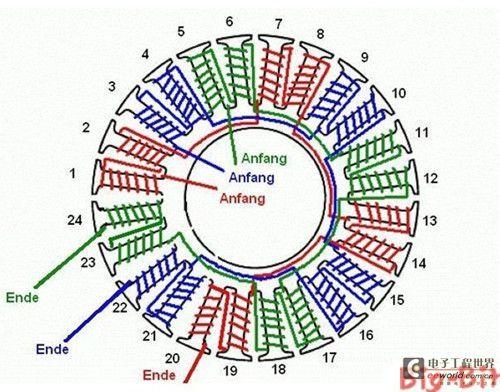

多功能双PCM分路器的原理框图如图2所示,由双PCM分路器(包括帧同步检测、帧/子帧同步策略及相应的时序控制逻辑等)、PCM模拟器、语音采集等功能模块组成。主要功能均由大规模集成电路CPLD可编程逻辑芯片实现。

CPLD选用了Latfice公司的ISP 4512V系统在线可编程器件。由于ISP便于现场更改,降低了研发成本,缩短了系统调试时间。

在众多通用的PCI接口芯片中,选用了目前业界设计选用的主流芯片:PLX公司的PLX9054。PLX9054是一种功能强、使用灵活并符合 PCIV2.2规范的32位、33MHz的。PCI总线接口控制器,它可以作为PCI总线的主控设备去控制总线,也可以作为目标设备去响应总线。 PIX9054提供了PCI总线、EWROM、IDCAL总线3个接口,作为一种“桥”芯片,在PCI总线和LOCAL总线之间有3种直接的数据传输模式。本设计选用了DMA数据传输模式。PLX9054以其强大的功能和简单的用户接口,为PCI总线接口的开发提供了一种简洁的方法,设计者只需设计本地总线接口控制电路,即可实现与PCI总线的高速数据传输。

3.2.2 帧、子帧同步及同步策略的实现

PCM 数据一个参数是以一个字或多个字的方式表达的,每个字由若干码元组成,而在一个PCM采集系统中,所有测试参数组成一个参数群,该参数群称为帧/子帧结构。怎样才能准确地区分每个字的起始位置.正确地恢复采集参数的并行数据,也就是获取帧/子帧以及表示各参数的数据字的起始时刻相一致的脉冲序列,其过程即称为帧/子帧同步。帧,子帧同步信号的作用在于在一串信号群中,给出一个起始时间标志,以便对每个参数字进行正确地分路,其特点是:它本身的信息量不大,但对传输的可靠性要求很高。帧同步检测器是PCM分路器板的关键部分,其他工作都是在帧同步检测器完成正确的检测后进行的,因此,帧同步检测器起着至关重要的作用。其框图如图3所示。

APP下载

APP下载 登录

登录

热门文章

热门文章