基于FFT算法的电力系统谐波检测装置,大多采用DSP芯片设计。DSP芯片是采用哈佛结构设计的一种CPU,运算能力很强,速度很快;但是其顺序 执行的模式限制了其进行FFT运算的速度。而现场可编程逻辑门阵列(Field Programmable Gate Array, FPGA)在近年来获得了突飞猛进的发展,目前已成为实现数字系统的主流平台之一。与DSP相比,FPGA最大的优势就是可以进行并行计算。在进行FFT 这类并行运算为主的算法时,采用FPGA的优势不言而喻。用FPGA实现FFT算法进行谐波检测成为了一大热点。

以往FPGA的设计主要依靠硬件描述语言来完成。Xilinx公司推出了专门针对实现DSP的设计软件—System Generator。在使用FPGA为原型平台运行算法时,它不仅能够对硬件的真实情况进行仿真,还能够自动生成硬件实现所需要的硬件描述语言代码。与语 言设计相比,使用System Generator有三大优势:第一,图形化操作,简单易用;第二,实现的算法能确保与仿真结果相符;第三,无需为仿真和实现建立不同的模型。因此,利用 System Generator可以大幅度减少用FPGA设计DSP的工作量,缩短开发周期。

1 基于FPGA的谐波检测模型的设计

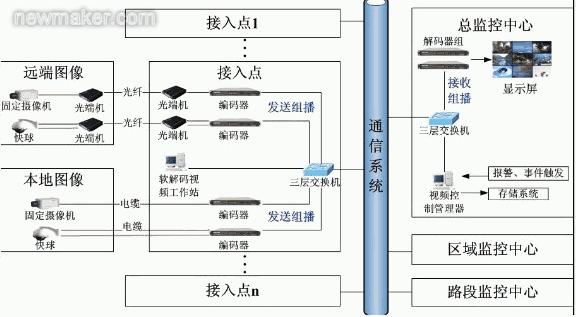

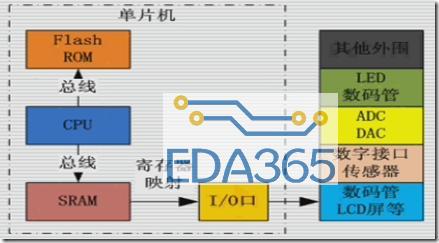

系统总体结构如图1所示。

(1)采样电路部分:包括互感器及滤波电路、锁相倍频电路和A/D转换电路。

待测电压、电流信号经互感器调理电路转化成便于采样的低压信号,经滤波器滤除检测范围外的高次谐波、高频干扰信号和噪声;然后进入A/D转换电路,电压、电流的模拟信号转换成可以用于计算的数字信号。锁相倍频电路用于跟踪待测信号的频率变化,以实现对信号的整周期采样。

(2)如图1所示,虚线框内部分由FPGA实现。最主要部分就是控制单元和FFT模块。控制单元主要由状态机的形式实现,当接收到锁相倍频电路送来 的倍频信号时,驱动A/D转换器进行采样。A/D转换器完成一次采样,先将数据送入到FIFO模块暂存,当数据达到进行FFT计算所需点数后,状态机控制 FIFO模块将数据送入FFT模块进行计算。为保证数据由A/D转换电路进入FPGA时的同步,A/D转换电路中的时钟由FPGA对开发板上的时钟分频后 提供。

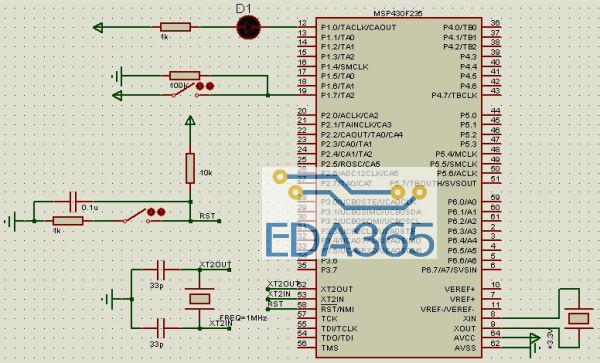

FPGA部分采用模块化的设计方法。在Simulink环境下搭建仿真模型,如图2所示。模型的核心部分是FFT计算模块(FFT v4_1),围绕它设计了数据输入子系统data_in、数据输出子系统(data_out)和控制单元模块(st_ctr)。用simulink中的信 号模块模拟出电压u(t)、电流信号i(t),考虑到后续数据输出控制的设计,预留了中断信号输入INT(signal 3),为便于仿真,其间隔时间与采样时间同步。数据输入子系统主要用于对采样数据的转换和暂存, 数据输入子系统的主要包括scale模块、convert模块和FIFO模块。数据输出子系统用于对FFT计算所得的结果进行处理,计算出电压、电流基波 及各次谐波的幅值和相位。

然后,搭建三相的电压、电流谐波检测模型(图3),其中包括了控制模块(ST_MA、da_out_ctr)和三个子系统A、B、C,每个子系统内 均有一个单相谐波检测模型。控制模块ST_MA实现对整个模型运行时序的控制以及对硬件采样电路的控制;da_out_ctr用于控制数据的输出。

APP下载

APP下载 登录

登录

热门文章

热门文章