然而今天,子系统之间带宽的迅速增长,低延时通路在子系统边界扩展的风险,以及严格的功耗和成本预算等因素导致一切变得更加复杂。在很多设计中,不可能在系统中布满CPU总线,或者外设总线。对于以芯片系统(SoC)实现的子系统,一些芯片设计人员能够通过这些子系统预先了解您的系统互联体系结构。由于低I/O电压和极短的上升时间,点对点互联遇到了很大的时序、信号完整性和电路板设计难题。

对于这一越来越复杂的情形,需要其他的解决方案。高速串行互联一直主要用于通信行业,在较长的距离上传输数据流。采用高级硅片工艺技术,在很多系统中,这些串行链路的接口变得非常小,而数据速率足够高,多千兆位串行链路替代了并行总线,甚至是异步I/O.

一个很明显的例子是PCI Express (PCIe)。最初的PCI是非常传统的并行同步总线。随着个人计算机带宽需求的增长,Intel把这一拓扑迁移到了高速串行链路的多个通路上。相似的发展也出现在大容量存储器件中,老的AT连接总线变为现在非常熟悉的串行ATA (SATA)。

而这些概念的应用已经超出了外设总线。为能够理解为什么高速串行链路可以应用于点对点连接甚至是单个电路板边界上,让我们了解一些系统划分问题。

系统划分

在理想的理论体系结构中,系统划分完全是基于数据和控制流图的系统过程。您画出图,然后,将功能模块划分到子系统中,子系统分成更大的组,这样,减小了带宽需求,增大了子系统之间链路的延时约束。然后,您可以针对这一链路的需求,以最短的合适互联,实现子系统之间的每一连接。

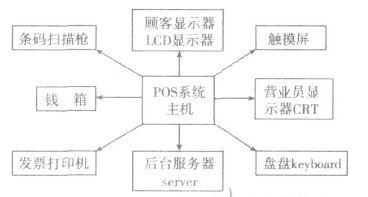

这一方法对于空白电路板非常适用。这实际上与SoC设计和FPGA使用的早期阶段非常相似。但是,当今的大部分设计都从商用芯片开始:专用标准产品(ASSP)或者微控制器单元(MCU)。这些SoC给我们提出了很多划分要求,如图1所示。我们选择的芯片决定了我们的子系统边界,以及应使用那种互联技术。如果您MCU唯一的外部互联是AMBA APB外设总线,或者DDR2存储器总线,以及一些通用I/O引脚,那么,这就是您的选择。

即使这样,划分仍然是系统设计中的一个重要步骤。而且,您必须对比SoC设计人员做出的假设和系统实际物理边界、带宽需求以及延时要求。因此,您需要识别出子系统:把需要交换大量数据的芯片放到一起,例如,SoC及其DRAM等。可以把它们之间的窄带、对延时要求不高的芯片放在不同的子系统中,例如,MCU和系统监视模数转换器(ADC)等。通过这种分组方法包括了系统中所有的功能模块后,可以转向对子系统之间的链路进行特征描述。

特征描述

在基于SoC的系统中,对子系统之间的互联进行特征描述看起来似乎没有什么意义。SoC的I/O选项很好的定义了接口。但是作为系统设计人员,您还是需要回答某些重要问题,仍然有一些可能不太明确的选项。

把问题分成带宽、延时和成本几类。带宽是这些问题的基础。如果您建议的互联方案是可行的,那么,您应该清楚的知道每一子系统的带宽需求。一般而言,这实际上是一个意义不大的问题。SoC设计人员将通路设计得很长,以保证芯片上的I/O要比预测的任务需求多得多。一般有足够的DRAM带宽来处理芯片CPU高速缓存生成的所有指令和数据流。通常有PCIe等高速总线连接至主系统或者宽带外设和加速器等。而且,还有与标准兼容的专用I/O接口。

但是,如果SoC设计人员没有预见到您所做的工作呢?有时候,基于您对系统体系结构的分析,您选择的SoC完全满足您的接口要求。在其他情况下,您可能会发现,在某些地方会遇到瓶颈,而有的情况下会遇到未使用的带宽,或者完全没有使用的接口。在所有这些情况下,您可能会重新思考这些接口的用途。或者,如果您通过在FPGA中汇集知识产权(IP)来构建SoC,那么,您能够更灵活的重新安排系统互联体系结构。特别是,您应该仔细处理系统中要求最高的数据流。将所有的东西都自动转储到一条共享总线上,即使是快速PCIe总线,也不是好方法。

APP下载

APP下载 登录

登录

热门文章

热门文章