引言

MIL-STD-1553B数据通信技术已被航空、航海乃至装甲武器系统所接纳,其技术从1553B总线通信接口的设计到构造大的通信应用系统已被众多设计师所掌握。但是由于传统的MIL-STD-1553B总线通信接口模块结构复杂,功能庞大(逻辑框图如图1所示),使得该模块的成本很高,有碍于新系统的设计、开发、仿真与研究,目前该技术的应用被局限在军工项目中。在工业控制领域,实验室装配等方面由于接口模块成本的因素,还没有很好地应用起来。为了迅速充实该领域,需要一种能满足应用、价廉的可插入通用IBM-PC或工业控制机的1553B-小型、集成、开发、仿真(以下简称1553B-SIDE)装置,用于各种类型的MIL-STD-1553B通信系统的开发与仿真。

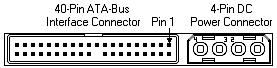

图1传统总线模块逻辑框图

美国DDC公司的IDEA(以下简称DDC-IDEA)卡是当今较为先进的MIL—STD—1553B集成、开发、仿真、模拟产品。该产品功能齐全,使用方便,但是价格很高。1553B—SIDE是依据DDC—IDEA卡的部分常用功能并结合现有的条件、市场行情为原则进行设计。其应用对象是1553B通信系统的开发与仿真,装配1553B通信实验室以及工业控制领域。

11553—SIDE逻辑结构

1553—SIDE包含硬件和软件两部分的内容,软件在下面第3节中介绍。

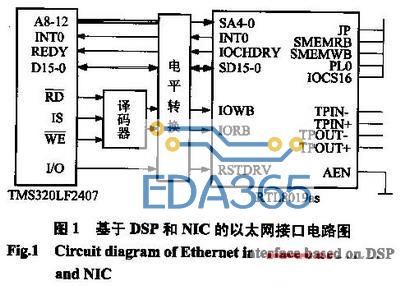

1553—SIDE由四部分组成,逻辑框图如图2。

图21553B—SIDE逻辑框图

1.11553B部分

1553B部分可完成数据串/并、并/串转换、MachesterⅡ码编译码、同步头的产生与控制、RT状态字的自动响应、地址的自动识别、各种消息格式和方式代码的总线传输、消息传输错误检测,完成电平转换功能以及直接耦合或变压器耦合选择功能。

1.2存储器部分

存储器是ISA总线主机与1553—SIDE之间交换信息的媒介,或者称为双向数据缓冲区,用于存放相关数据结构和发送接收的数据。

1.3控制器部分

控制器由可擦除的可编程逻辑门阵列EP5130芯片完成,它包括了1553—SIDE的译码逻辑、ISA总线主机与1553—SIDE访问RAM仲裁逻辑以及中断ISA总线主机的支持逻辑电路。

1.4缓冲隔离器部分

缓冲隔离器用于数据,地址的缓冲与隔离。它将ISA总线主机与1553—SIDE的内总线隔离开来,使两者能够实时地并行处理各自的数据。

21553—SIDE主要功能及技术指标

航空电子通信系统按网络层次可分为五层,1553—SIDE完成四层,即驱动层、传输层、数据链路层和物理层,其中1553—SIDE硬件完成数据链路层和物理层的功能,通信软件完成传输层和驱动层的功能,应用层由驻留在IBM—PC主机上的应用软件完成。

2.11553—SIDE主要性能

a. 1553—SIDE采用BC/RT/MT一体化设计方案,由软件选择使用;

b. 满足MIL—STD—1553B标准的各种消息传输,方式指令、状态位的技术要求;

c. 1553—SIDE与1553B总线(网缆)耦合方式为可选的变压器耦合或直接耦合,支持双余度总线结构,其电气特性满足MIL—STD—1553B标准;

d. 1553—SIDE与IBM/PC的数据交换通过32K×16位伪双口存贮器完成;

e. 1553—SIDE向ISA总线主机提供两级中断信号。

APP下载

APP下载 登录

登录

热门文章

热门文章