1 ATmega48介绍

ATmega48是基于AVR增强型RISC(精简指令集)结构的高性能、低功耗的8位CMOS微控制器。微控制器具有可控制的上电复位和可编程的掉电检测电路、经过标定的片内RC振荡器、片内外18个中断源和5种休眠模式。由于其先进的指令集以及单时钟周期指令执行时间,ATmega48的数据吞吐率高达1 MIPs/MHz,运行速度比普通的单片机高出10倍,从而可以缓解系统在功耗和处理速度之间的矛盾。

其片内集成了4 KB的系统内可编程Flash、256字节的EEPROM、512字节的SRAM。其外设具有可编程的串行USART接口、可工作于主机/从机模式的SPI串行接口;存在2个具有独立预分频器和比较器功能的8位定时/计数器和1个具有预分频器、比较功能和捕捉功能的16位定时/计数器、具有独立片内振荡器的可编程看门狗定时器等。ATmega48/88/168芯片硬件电路可以完全兼容,完全可以根据软件实际需求灵活选择AVR芯片,极大地方便系统的开发与研制。

2 CMX865简介

CMX865是CML公司新出的一款DTMF编/解码器/FSK调制解调器复合IC芯片,它采用单个高速串行总线控制,与大多数串行接口兼容。 CMX865的主要特征是:

◆供电电压2.7~5.5 V,低功耗操作模式;

◆支持V.23、Bell202 FSK 1200 bps编码/解码;

◆集成高可靠性DTMF、编码器/解码器;

◆集成振铃检测功能,支持语音探测功能。

3 硬件设计

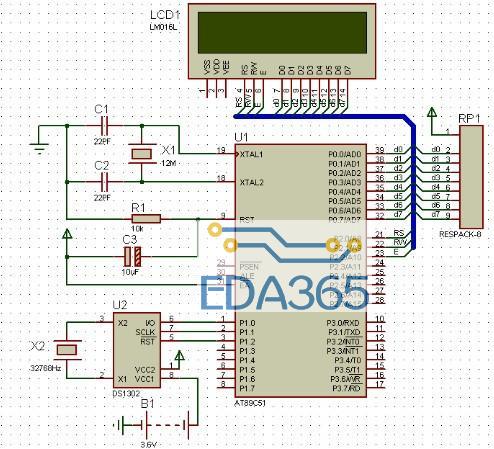

图1为串口转FSK通信模块电路。系统主要以AVR单片机ATmega48芯片和CMX865调制/解调芯片为硬件架构,ATmega48芯片利用C-BUS总线对CMX865芯片进行控制操作,实现FSK通信。CMX865芯片的IRQN终端与CPU芯片的外部中断0(INT0)相连,确保软件可以采用中断方式接收/发送FSK数据。CMX865芯片的时钟信号、片选信号、响应应答数据信号、接收控制数据信号分别与ATmega48芯片的普通I/O接口引脚相连,CPU可以通过模拟口线方式对CMX865芯片进行控制。

图1还提供了基本的FSK接收/发送数据接口电路和振铃检测电路。在FSK发送电路中,CMX865芯片TXA(15引脚)处外接电阻的目的是匹配芯片接口对线路的交流阻抗。在FSK接收电路中,CMX865芯片RXAFB(9引脚)与RXAN(10引脚)之间的电容以及隔离变压器之间电容设计的目的是滤除高频噪声;通过调节接收电路中两个电阻R1、R2的阻值即可改变接收端提供给CMX865芯片信号的幅度。在振铃检测电路中,IC1是光电耦合器,不振铃时光电三极管截止,RING为高电平;振铃时,振铃信号经过电容耦合及稳压管稳压,振铃电压使IC1内发光二极管发光,照射到光电三极管的基极上导致光电三极管导通,RING为低电平,通过ATmega48引脚检测到低电平的振铃信号。

4 软件实现

ATmega48芯片具有4 KB内部Flash和512字节的片内SRAM,软件实现需考虑资源分配问题,特别是SRAM使用情况。由于程序涉及串口通信、DTMF通信和FSK通信3种情况,理论上需要开辟6个缓冲区。如果这样,每一个缓冲区的大小显然不能确保达到实际通信数据量的需求。结合FSK通信特点,DTMF数据传输与FSK数据传输不可能同时发生,因此FSK与DTMF可共用相同缓冲区。同样串口接收与FSK发送、串口发送与FSK接收都不会同时发生,这样通信只需要开辟两个缓冲区就可以确保模块正常通信,考虑实际业务平台数据量情况,软件设计中为FSK接收开辟255字节缓冲区复用;FSK发送开辟45字节缓冲区复用。

APP下载

APP下载 登录

登录

热门文章

热门文章