摘要:异构双核SoC采用SPARC V8处理器加专用DSP的架构,根据其应用特点,设计了SPARC V8处理器与专用DSP之间互斥通讯机制。并完成了SPARC V8处理器的状态控制设计与优化、外部存储控制器的接口优化设计,以及SoC的整体功能验证。FPGA实验结果表明,异构双核SoC功能正确可靠,有效地提高了系统的效能比。

引言

从开发并行性的级别来看,指令级并行是一种普遍存在于各类程序中的细粒度并行性,随着片上集成度的不断提高,再增加动态指令窗口的体积和发射宽度将无助于高主频的实现,开发更高的ILP,以获得整体性能的提升所需的硬件设计和验证开销已很难承受。单芯片多处理器(CMP)是近年来微处理器体系结构研究的热点之一,它很好地解决了硬件设计和验证复杂度提高的问题。在一些特殊应用领域使用通用的RSIC处理器来完成,需要较高的性能才能达到其基本要求,系统的效能比很低。如果采用RSIC核加专用DSP核的异构双核结构,普通控制部分由RSIC核实现,特殊功能部分能够采用专用的DSP来实现,可有效地提高系统的效能比,可明显提升系统性能,同时有效降低整个系统的功耗。

异构双核SoC设计与实现

异构双核SoC结构

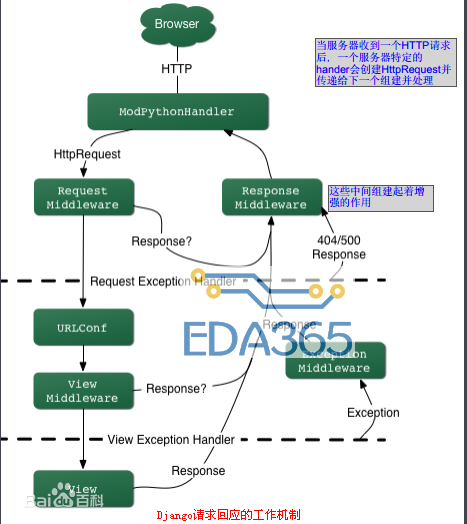

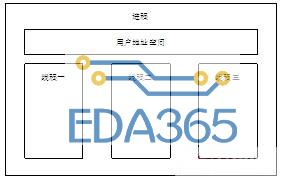

根据弹载测控系统的应用特点,采用RSIC处理器核加梯形图解算专用DSP的异构双核结构设计了SoC,如图1所示。RSIC处理器核主要完成控制功能,负责系统的启动,主程序的运行,状态的查询与传输,功能块的运算,以及中断的处理。专用DSP核主要完成梯形图的解算、IO状态表的刷新等工作。

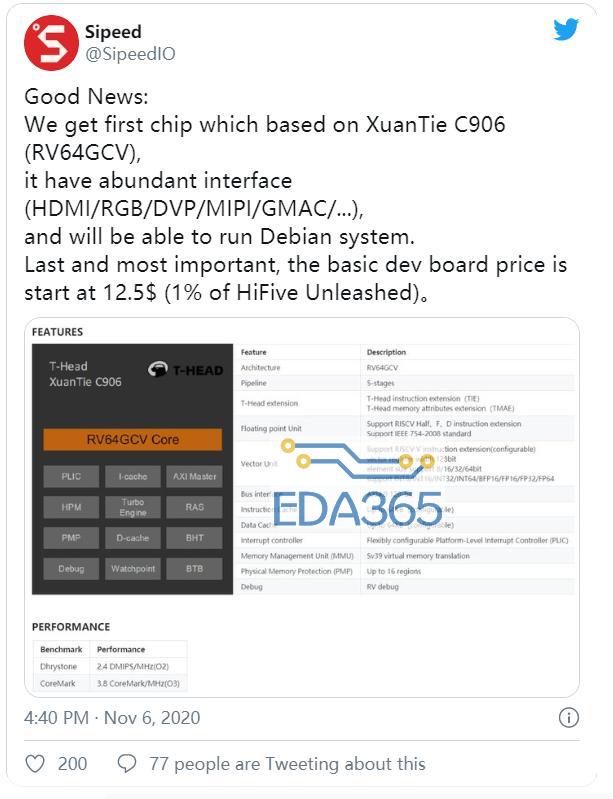

RSIC处理器核采用经过多款芯片验证的SPARC V8处理器核。处理器系统由整数处理单元、浮点处理单元、Cache子系统、中断控制器、串口、定时器、看门狗、调试支持单元DSU等组成。在32KB指令Cache、16KB数据cache的配置下,采用Dhrystone2.1得出的运算性能可以达到0.86MIPS/MHz。

DSP核采用PLC梯形图解算系统,该系统包含了HLS解算单元、定时器、串口、地址译码单元、PTO、PWM、SPI等模块构成。

SoC运行方式

异构双核SoC的主要运行方式如图2所示,主程序在SPARC V8处理器中运行,对整个系统进行初始化操作,然后进入主程序,根据启动策略配置进行相应的模块初始化,接着进入无限循环调度程序。在无限循环调度程序中,判断是否运行专用DSP;如果运行专用DSP,则暂停SPARC V8处理器的运行,将总线控制权交给专用DSP完成PLC扫描程序的运行、IO状态的刷新、特殊功能处理,专用DSP完成一次顺序扫描后将控制权交还SPARC V8处理器,SPARC V8处理器接着完成相应的通信处理,按IO映射表更新外部状态;如果不运行专用DSP,SPARC V8处理器直接执行IO映射及相应的通信处理,按IO映射表更新外部状态,然后重新判断是否运行专用DSP,进行下一次循环。

APP下载

APP下载 登录

登录

热门文章

热门文章