摘要:弹载信号处理机的DSP系统需要高速、简便的上位机接口实现大数据量的变量实时监控和在线程序加载功能。USB接口以其简单、高速与通用的优势成为优选。介绍一种基于USB接口芯片(CY7C68013A)和FPGA实现的ADSP-TS101扩展USB接口的设计方法,该方法利用DSP的Link-port接口,以DMA方式进行高速数据交换,目前该设计已成熟、可靠地应用于某弹载信号处理系统。

关键词:USB;DSP Linkport;PC机接口;高速数据交换

0 引言

ADI公司的DSP器件(ADSP-TS101)具有浮点实时处理能力强、并行性好等优点,从而广泛被弹载信号处理系统选用。其作为弹载主处理器,在导弹的系统试验中,需要利用上位机对其中的大数据量的软件变量进行实时监控和记录,这就需要一个上行传输给上位机的高速通信接口,数据上行的数据率需要大于6 MB/s。同时这个通信接口还需具有双向特性,通过数据下行可实现在线程序加载与烧写。这样的通信接口,还需具备设备连接简单、通用性强等特性,并能实现远程(大于3m)数据传输。

ADSP-TS101自身的外总线接口和链路口(Linkport接口),虽速度很快,但连接复杂,难以长线传输,并不具备上述需求特征。可以通过在DSP的Linkport总线接口上增加FPGA实现的适配电路,扩展USB 2.0接口,实现上述应用需求。下文将介绍具体的实现方案。

1 系统总体方案

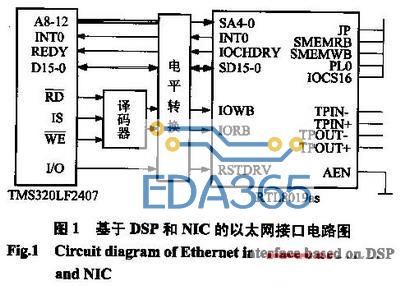

系统实现的总体方案如图1所示。

在本方案中,USB接口芯片选用Cypress公司的CY7C68013A。该芯片是Cypress公司FX2系列USB 2.0集成微控制器之一。集成了USB 2.0收发器、SIE、增强8051微控制器和GPIF,是一种优秀的高速USB外设控制器。内置的8051微控制器独立于USB数据通道,由SIE实现大部分USB 1.1和USB 2.0协议;USB FIFO和外部从FIFO映射到相同的8个512 B RAM模块,实现内部传输和外部传输的无缝连接,可以较低的代价获得较高的带宽;8.5 KB内部RAM空间,可运行较为复杂的固件,实现软件对硬件的配置。GPIF是由用户可编程有限状态机驱动的柔性8/16位并行口,可编程GPIF向量组成一个GPIF波形,匹配受控接口的时序。

ADSP-TS101作为弹载主DSP芯片,含4个链路口,每个链路口可在时钟双沿以8位进行双向数据传输,速率高达250 MB/s。通过该接口,DSP每个处理帧将预观测的变量结果以DMA的方式打包向上位机发送。

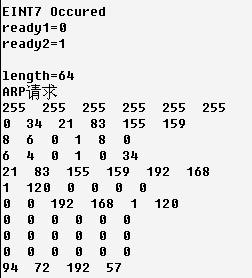

FPGA实现ADSP-TS101的Linkport接口与CY7C68013A之间的双向数据缓冲和接口协议转换。考虑到CY7C68013A中的FIFO容量较DSP的一个处理帧预发送或接收的数据量较小,故在FPGA中设置上行和下行各一个大容量FIFO,用于数据缓冲,以减少对DSP中并行流水运行的程序的打扰。这里,由于DSP链路口的瞬时数据率远高于USB芯片的传输速率(理论上限为60 MB/s),故FIFO的DSP端口的数据传输为:一个处理帧只操作一次,而USB芯片端则分成多次操作。

限于篇幅,下文将重点对传输数据率要求高、设计难度大的上行通道的设计进行详细描述。

APP下载

APP下载 登录

登录

热门文章

热门文章