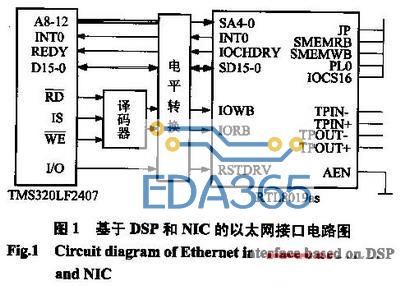

摘要:面对众多的、性能各有千秋的同类产品,如何取舍,如何在设计中选用合适的器件,往往是设计者尤其是新手们踌躇的事情。本文分析在检测设备中设计PCI总线接口卡时如何选择适合的PCI控制器总是;分别介绍几种符合PCI2.2协议的新型PCI总线桥接器:AMCC5920、CY70944PV-AC、PCI9030、PCI9054、PCI9056,同时给出其结构框图。在比较它们各自的特性后,提出自己的方案选择。 关键词:PCI总线 接口卡 AMCC5920 CY7C9449PV-AC PCI9030 PCI9054 PCI9056 引言 现要研制一台检测设备,采用工控机结构。需要设计一个将上位机与DSP、DDS等功能单元(做成扩展卡插在扩展槽中)连接起来的模块单元(即用来传输控制命令、状态和信号数据的接口部件)。在设计计算机扩展接口之前,首先考虑的是采用哪种总线形式。PCI总线是Intel公司推出的一种高性能局部总线,它的主要特点是:①具有地址数据多路复用的高性能32位或64位的同步总线。总线引脚数目和部件数量少(对于总线目标设备只有47根信号线,对于主设备最多只有49根信号线),降低了成本及布线复杂度。②PCI局部总线在33MHz总线时钟、32位数据通路时,可达到峰值132Mbit/s的带宽;在33MHz总线时钟,64位数据通路时可达到峰值264Mbit/s的带宽;在66MHz主频时,对于32位数据通路和64位数据通路带宽的峰值,可分别达到264Mbit/s或528Mbit/s的带宽;PCI总线还有线性突发传输功能,保证了满载的高速传输。③PCI总线的设计是独立于处理器的,可以方便地符合PCI规范的微机和工作站系统中进行硬件移植,目前已成为嵌入式系统的局部总线之一。④隐蔽的总线仲裁,减小了仲裁开销。⑤极小的存取延时,采用总线多主控和异步数据转移操作。⑥PCI提供的数据和地址奇偶校验功能,保证数据完整性和准确性。⑦PCI总线与CPU和时钟频率无关,它能支持多个外设,设备间通过局部总线可以完成数据快速传递,从而很好地解决数据传输的瓶颈问题。⑧对PCI扩展卡及元件,能够自动配置,实现设备的即插即用。由于使用方便、灵活、产品寿命长,目前PCI总线产品与其它的总线标准相比具有茂大优越性和更为广阔的应用前景。我们决定采用1个PCI总线的控制器来完成这个适配卡的设计。通过这一适配卡的连接,将信号、数据通过工控机内的总线插槽传到各个功能模块中。 1 芯片选择 目前,PCI总线接口电路主要有2种选择:PCI专用芯片组(又称桥接电路)或PLD。PCI总线协议较复杂,设计PCI控制接口难度较大,对于产品不大又有时限的工程项目来说,成本较大;而通用的PCI接口芯片功能全而强大(例如FIFO速度快、容量大,可支持DMA方式等),它实现PCI规范所要求的所有硬件接口信号和配置空间寄存器,能够减少开发时间和成本,并获得较好的数据传输性能。所以决定采用已有的桥接电路。PCI总线桥接器又分主控设备(master)和目标设备(target)两大类。主控设备可以控制总线驱动地址、数据和控制信号;目标设备不能启动总线操作,只能依赖于主控设备从其中读取或向其传送数据。以下针对当前的一些较新推出的产品作一些介绍和比较。 1.1 目标设备 这是一款采用SMARTarget技术的32位、33MHz的PCI目标接口芯片。是目前PLX公司推出的最高级通用PCI目标设备。它完全符合PCI2.2规范,并且是业界提供的第1个支持CompactPCI、热交换规范PICMG2.1的产品。 ②兼容性。PCI9030的引脚与9050、9052、9054、9080均不兼容,只兼容9050、9052的寄存器,并提供了某些寄存器新的位定义和若干新的寄存器定义;但与9054以及9080的寄存器不兼容。PCI9030可广泛应用于网络、通信、图像及海量存储设计中。它易于将已有的其它总线设计转换到PCI总线的设计,缩短了设计周期,且其丰富的外部接口大节省了制板空间。 (2)AMCCS5920 AMCCS5920(简称S5920)是AMCC公司新近推出的一种PCI总线目标接口芯片,从其功能来看,可被视作是S5933的子集。与后者相比,S5920减少了总线主控的功能,其它性能相仿,甚至有所增强;而价格却降低了很多,因此,在很多无需进行总线主控的场合,采用S5920完成设计能取得更高的性能价格比。其主要性能如下:符合PCI2.2标准;最高传输速率132MB/s;可编程的预取长度和等待周期;4个32位读写FIFO的直通通道;外加总线可工作于主动或被动状态;支持即插即用;支持串行NVRAM和可选的外部BIOS配置;160脚PQFP封装。 1.2 主控设备 (1)PCI9054 PCI9054是由美国PLX公司生产的先进的PCI I/O加速器,采用了先进的PLX数据流水线结构技术,是32位、33MHz的PCI总线主I/O加速器;符合PCI本地总线规范2.2版,突发传输速率达到132MB/s,本地总线支持复用/非复用的32位地址/数据;有M、C、J三种模式;针对不同的处理器及局总线特性可选,尽量减少中间逻辑;具有可选的串行E2PROM接口,本地总线时钟可和PCI时钟异步。PC9054内部有6种可编程的FIFO,以实现零等待突发传输及本地总线和PCI总线之间的异步操作;支持主模式、从模式、DMA传输方式,因其强大的功能可应用于适配卡和嵌入式系统中。PCI 9054是一种性比高的PCI桥路芯片,比PCI9080、PCI9050等性能更优越。 (2)PCI9056 具有32位、66MHz的PCI总线以及局部总线操作,是目前最先进的32位通用主控芯片;内部还是基于原有的9054技术架构。与9054相比,有以下特点:a.含有1个PCI仲裁器,支持7个外部主控设备,针对Compact PCI(含有7个插槽)的设计是足够了。B.2个独立的DMA通道:每个通道含有1个双向的深度为64长字(256字节)的FIFO。C.差分读写数据。d.用有效位旗语描述符控制动态DMA振铃管理。e.增强的M模式功能,能提供PowerQUICC超出原有16字节长度限制的突发传送。f.对于主控方式,有2个独立的读(32长字)写(64长字)FIFO;对于目标模式,也有2个响应同样深度的FIFO;并有可编程的读信号超过报告及其恢复。g.符合PICMG 2.1热交换技术规范,包括电压偏移容错、预充电功能与预置不支持响应功能,支持PCI电源管理rl.1,含有D3cold电源事件中断,符合Windows 98和Windows2000系统设计的需求,h.可应用于嵌入式主机的复位和中断引脚设置功能。i.JTAG边界扫描。j.256-FPBGA封装(17mm17mm,1.0mm),2.5V的CMOS芯核电压,对3V和5V的I/O信号电平容错。 (3)CY7C09449PV CY7C09449PV-AC是Cypress公司提供的符合PCI2.2总线规范的功能完善、价格低廉的双端口RAM接口芯片。其中一个端口是PCI接口,适合与PC机通信;另一个端本地接口,适合与各类本地CPU通信,其总线通信时钟速率可达50MHz,2个端口均可以独立读/写静态存储器SRAM。其主要特点如下:a.完全兼容PCI规范2.2版;b.128Kbit双向静态SRAM;c.可作为主/从设备进行数据的传输,支持PCI突发方式及DMA操作;d.具有I2O(智能输入/输出)功能,当I/O单元工作时包含4组32位FIFO、终端寄存器及部分SRAM用于一般存储目的;e.可作为主桥接口;f.单一3.3V电源供电,对3V、5V信号电平容错;g.可通过I2C总线对芯片进行初始化配置,并把设置参数存于非易失性NVRAM;h.由4个FIFO和1个中断寄存器构成I2O消息单元;i.可直接与多种处理器连接,减少了逻辑部件;j.局部总线时钟可达50MHz。k.160脚扁平方形塑封。仲裁加上等待的方式,允许两边CPU在指令级共享SRAM,允许两边的CPU相互通过中断交换信息,还允许通过状态信号相互同步。该芯片不含有总线仲裁功能(这一功能是标准PC及嵌入式系统所必需的),可以请示获取PCI总线控制权。 CY7C09449PV-AC可以直接与许多处理器连接,省却了粘着逻辑部件,可以采用总线。 2 选用分析 在众多通用的PCI接口芯片中,最后选用了PCI9054。原因如下:①目前AMCC公司的S5920、PLX公司的PCI9052/50等芯片已在市场上广泛应用,它们的优越性主要是实现了PCI目标设备的功能,并提供了与ISA总线信号兼容或时序相似的本地总线信号,是从ISA到PCI总线平台平滑过渡的最佳选择;但它们都不支持PCI2.2协议,无论是操作速度还是传输带宽在性能上已属落后,而且从DSP和适配卡的发展方向来说,3.3V低电压的信号环境是更主流的选择。②如果只是与局总处理器相连,采用CY7C09449PV-AC将是上佳之先;但由于本系统各功能模块作用不同,与主机交换信息的方式不同,不能同时共享CY7C09449PV-AC的右边接口,因此不选用;③信号产生模块中的DSP在需要的时候,也会发起传输,所以,决定采用主/从控制器更好些。我们所研制的这套检测设备是将根据设定的参数而产生的仿真的回波信号数据流,当每次收到启动脉冲时,将预存数据传入处理模块中,同时DSP预备产生下一次所需的回波信号,这样对数据流的速度要求就不是很高,所以选择了PCI9054。PCI9054也是目前业界设计适配器选用的主流芯片。PCI9054以其强大的功能和简单的用户接口,为PCI总线接口的开发提供了一种简洁的方法,设计者只需设计本地总线接口控制电路,即可实现与PCI总线的高速数据传输。而且由于PCI9056、PCI9656与它的兼容性较好,将来很容易将设计性能提升到64位或64MHz操作,目前已将PCI9054用于实际设计中。 图1~图5是所介绍的PCI总线接口卡的设计方案图及各个芯片的内部结构图。 每当要开始一个工程项目设计时,首先要搞清楚的是该项目所要完成的性能指标,然后再确定具体的实施方案。在成本预算允许的情况下,当然要选用当前最先进的芯片,同时也要考虑到采用这种产品的设计在未来的可扩展性、易维护性、升级成本等;另一方面也不能盲目采用所谓“高性能”产品。“高性能”产品往往集成了很多功能,而且“高性能”的体现还要整体系统性能的配套提高,或者设计指标本就不高,这样选用的“高性能”芯片只会造成资源浪费,也许随之来还有应用的复杂性。总之在考虑同类产品的选用时,要以尽量提高产品的性价比为宗旨。在这方面,PLX为了使产品开发风险降到最低并降低成本,提供了支持PCI9054的软件开发套件(SDK)和参考设计套件(RDK),这些套件可让设计者快速地将设计推向生产线。当然,产品的更新换代速度、价格、供货期等这些也都是需要考虑的方面,同时参考一些成熟的产品设计,也能提供一定的参考作用。 | |

摘要:面对众多的、性能各有千秋的同类产品,如何取舍,如何在设计中选用合适的器件,往往是设计者尤其是新手们踌躇的事情。本文分析在检测设备中设计PCI总线接口卡时如何选择适合的PCI控制器总是;分别介绍几种符合PCI2.2协议的新型PCI总线桥接器:AMCC5920、CY70944PV-AC、PCI9030、PCI9054、PCI9056,同时给出其结构框图。在比较它们各自的特性后,提出自己的方案选择。 关键词:PCI总线 接口卡 AMCC5920 CY7C9449PV-AC PCI9030 PCI9054 PCI9056 引言 现要研制一台检测设备,采用工控机结构。需要设计一个将上位机与DSP、DDS等功能单元(做成扩展卡插在扩展槽中)连接起来的模块单元(即用来传输控制命令、状态和信号数据的接口部件)。在设计计算机扩展接口之前,首先考虑的是采用哪种总线形式。PCI总线是Intel公司推出的一种高性能局部总线,它的主要特点是:①具有地址数据多路复用的高性能32位或64位的同步总线。总线引脚数目和部件数量少(对于总线目标设备只有47根信号线,对于主设备最多只有49根信号线),降低了成本及布线复杂度。②PCI局部总线在33MHz总线时钟、32位数据通路时,可达到峰值132Mbit/s的带宽;在33MHz总线时钟,64位数据通路时可达到峰值264Mbit/s的带宽;在66MHz主频时,对于32位数据通路和64位数据通路带宽的峰值,可分别达到264Mbit/s或528Mbit/s的带宽;PCI总线还有线性突发传输功能,保证了满载的高速传输。③PCI总线的设计是独立于处理器的,可以方便地符合PCI规范的微机和工作站系统中进行硬件移植,目前已成为嵌入式系统的局部总线之一。④隐蔽的总线仲裁,减小了仲裁开销。⑤极小的存取延时,采用总线多主控和异步数据转移操作。⑥PCI提供的数据和地址奇偶校验功能,保证数据完整性和准确性。⑦PCI总线与CPU和时钟频率无关,它能支持多个外设,设备间通过局部总线可以完成数据快速传递,从而很好地解决数据传输的瓶颈问题。⑧对PCI扩展卡及元件,能够自动配置,实现设备的即插即用。由于使用方便、灵活、产品寿命长,目前PCI总线产品与其它的总线标准相比具有茂大优越性和更为广阔的应用前景。我们决定采用1个PCI总线的控制器来完成这个适配卡的设计。通过这一适配卡的连接,将信号、数据通过工控机内的总线插槽传到各个功能模块中。 1 芯片选择 目前,PCI总线接口电路主要有2种选择:PCI专用芯片组(又称桥接电路)或PLD。PCI总线协议较复杂,设计PCI控制接口难度较大,对于产品不大又有时限的工程项目来说,成本较大;而通用的PCI接口芯片功能全而强大(例如FIFO速度快、容量大,可支持DMA方式等),它实现PCI规范所要求的所有硬件接口信号和配置空间寄存器,能够减少开发时间和成本,并获得较好的数据传输性能。所以决定采用已有的桥接电路。PCI总线桥接器又分主控设备(master)和目标设备(target)两大类。主控设备可以控制总线驱动地址、数据和控制信号;目标设备不能启动总线操作,只能依赖于主控设备从其中读取或向其传送数据。以下针对当前的一些较新推出的产品作一些介绍和比较。 1.1 目标设备 这是一款采用SMARTarget技术的32位、33MHz的PCI目标接口芯片。是目前PLX公司推出的最高级通用PCI目标设备。它完全符合PCI2.2规范,并且是业界提供的第1个支持CompactPCI、热交换规范PICMG2.1的产品。 ②兼容性。PCI9030的引脚与9050、9052、9054、9080均不兼容,只兼容9050、9052的寄存器,并提供了某些寄存器新的位定义和若干新的寄存器定义;但与9054以及9080的寄存器不兼容。PCI9030可广泛应用于网络、通信、图像及海量存储设计中。它易于将已有的其它总线设计转换到PCI总线的设计,缩短了设计周期,且其丰富的外部接口大节省了制板空间。 (2)AMCCS5920 AMCCS5920(简称S5920)是AMCC公司新近推出的一种PCI总线目标接口芯片,从其功能来看,可被视作是S5933的子集。与后者相比,S5920减少了总线主控的功能,其它性能相仿,甚至有所增强;而价格却降低了很多,因此,在很多无需进行总线主控的场合,采用S5920完成设计能取得更高的性能价格比。其主要性能如下:符合PCI2.2标准;最高传输速率132MB/s;可编程的预取长度和等待周期;4个32位读写FIFO的直通通道;外加总线可工作于主动或被动状态;支持即插即用;支持串行NVRAM和可选的外部BIOS配置;160脚PQFP封装。 1.2 主控设备 (1)PCI9054 PCI9054是由美国PLX公司生产的先进的PCI I/O加速器,采用了先进的PLX数据流水线结构技术,是32位、33MHz的PCI总线主I/O加速器;符合PCI本地总线规范2.2版,突发传输速率达到132MB/s,本地总线支持复用/非复用的32位地址/数据;有M、C、J三种模式;针对不同的处理器及局总线特性可选,尽量减少中间逻辑;具有可选的串行E2PROM接口,本地总线时钟可和PCI时钟异步。PC9054内部有6种可编程的FIFO,以实现零等待突发传输及本地总线和PCI总线之间的异步操作;支持主模式、从模式、DMA传输方式,因其强大的功能可应用于适配卡和嵌入式系统中。PCI 9054是一种性比高的PCI桥路芯片,比PCI9080、PCI9050等性能更优越。 (2)PCI9056 具有32位、66MHz的PCI总线以及局部总线操作,是目前最先进的32位通用主控芯片;内部还是基于原有的9054技术架构。与9054相比,有以下特点:a.含有1个PCI仲裁器,支持7个外部主控设备,针对Compact PCI(含有7个插槽)的设计是足够了。B.2个独立的DMA通道:每个通道含有1个双向的深度为64长字(256字节)的FIFO。C.差分读写数据。d.用有效位旗语描述符控制动态DMA振铃管理。e.增强的M模式功能,能提供PowerQUICC超出原有16字节长度限制的突发传送。f.对于主控方式,有2个独立的读(32长字)写(64长字)FIFO;对于目标模式,也有2个响应同样深度的FIFO;并有可编程的读信号超过报告及其恢复。g.符合PICMG 2.1热交换技术规范,包括电压偏移容错、预充电功能与预置不支持响应功能,支持PCI电源管理rl.1,含有D3cold电源事件中断,符合Windows 98和Windows2000系统设计的需求,h.可应用于嵌入式主机的复位和中断引脚设置功能。i.JTAG边界扫描。j.256-FPBGA封装(17mm17mm,1.0mm),2.5V的CMOS芯核电压,对3V和5V的I/O信号电平容错。 (3)CY7C09449PV CY7C09449PV-AC是Cypress公司提供的符合PCI2.2总线规范的功能完善、价格低廉的双端口RAM接口芯片。其中一个端口是PCI接口,适合与PC机通信;另一个端本地接口,适合与各类本地CPU通信,其总线通信时钟速率可达50MHz,2个端口均可以独立读/写静态存储器SRAM。其主要特点如下:a.完全兼容PCI规范2.2版;b.128Kbit双向静态SRAM;c.可作为主/从设备进行数据的传输,支持PCI突发方式及DMA操作;d.具有I2O(智能输入/输出)功能,当I/O单元工作时包含4组32位FIFO、终端寄存器及部分SRAM用于一般存储目的;e.可作为主桥接口;f.单一3.3V电源供电,对3V、5V信号电平容错;g.可通过I2C总线对芯片进行初始化配置,并把设置参数存于非易失性NVRAM;h.由4个FIFO和1个中断寄存器构成I2O消息单元;i.可直接与多种处理器连接,减少了逻辑部件;j.局部总线时钟可达50MHz。k.160脚扁平方形塑封。仲裁加上等待的方式,允许两边CPU在指令级共享SRAM,允许两边的CPU相互通过中断交换信息,还允许通过状态信号相互同步。该芯片不含有总线仲裁功能(这一功能是标准PC及嵌入式系统所必需的),可以请示获取PCI总线控制权。 CY7C09449PV-AC可以直接与许多处理器连接,省却了粘着逻辑部件,可以采用总线。 2 选用分析 在众多通用的PCI接口芯片中,最后选用了PCI9054。原因如下:①目前AMCC公司的S5920、PLX公司的PCI9052/50等芯片已在市场上广泛应用,它们的优越性主要是实现了PCI目标设备的功能,并提供了与ISA总线信号兼容或时序相似的本地总线信号,是从ISA到PCI总线平台平滑过渡的最佳选择;但它们都不支持PCI2.2协议,无论是操作速度还是传输带宽在性能上已属落后,而且从DSP和适配卡的发展方向来说,3.3V低电压的信号环境是更主流的选择。②如果只是与局总处理器相连,采用CY7C09449PV-AC将是上佳之先;但由于本系统各功能模块作用不同,与主机交换信息的方式不同,不能同时共享CY7C09449PV-AC的右边接口,因此不选用;③信号产生模块中的DSP在需要的时候,也会发起传输,所以,决定采用主/从控制器更好些。我们所研制的这套检测设备是将根据设定的参数而产生的仿真的回波信号数据流,当每次收到启动脉冲时,将预存数据传入处理模块中,同时DSP预备产生下一次所需的回波信号,这样对数据流的速度要求就不是很高,所以选择了PCI9054。PCI9054也是目前业界设计适配器选用的主流芯片。PCI9054以其强大的功能和简单的用户接口,为PCI总线接口的开发提供了一种简洁的方法,设计者只需设计本地总线接口控制电路,即可实现与PCI总线的高速数据传输。而且由于PCI9056、PCI9656与它的兼容性较好,将来很容易将设计性能提升到64位或64MHz操作,目前已将PCI9054用于实际设计中。 图1~图5是所介绍的PCI总线接口卡的设计方案图及各个芯片的内部结构图。 每当要开始一个工程项目设计时,首先要搞清楚的是该项目所要完成的性能指标,然后再确定具体的实施方案。在成本预算允许的情况下,当然要选用当前最先进的芯片,同时也要考虑到采用这种产品的设计在未来的可扩展性、易维护性、升级成本等;另一方面也不能盲目采用所谓“高性能”产品。“高性能”产品往往集成了很多功能,而且“高性能”的体现还要整体系统性能的配套提高,或者设计指标本就不高,这样选用的“高性能”芯片只会造成资源浪费,也许随之来还有应用的复杂性。总之在考虑同类产品的选用时,要以尽量提高产品的性价比为宗旨。在这方面,PLX为了使产品开发风险降到最低并降低成本,提供了支持PCI9054的软件开发套件(SDK)和参考设计套件(RDK),这些套件可让设计者快速地将设计推向生产线。当然,产品的更新换代速度、价格、供货期等这些也都是需要考虑的方面,同时参考一些成熟的产品设计,也能提供一定的参考作用。 | |

APP下载

APP下载 登录

登录

热门文章

热门文章