随着微电子技术的飞速发展,集成电路规模按照摩尔定律(微芯片上集成的晶体管数目每18个月翻一番)飞速提高,片上系统(SystemOnChip,简称SOC)技术成为国际超大规模集成电路的发展趋势。在SOC系统设计中,为了能够快速、稳定的形成产品,IP核积累和复用技术逐渐成为各个芯片厂商的首选。在这样的背景下,IP复用技术成为了集成电路设计的一个重要分支,很多设计厂商在购买其它公司的IP核的同时,也越来越重视本公司的IP核设计和积累。

DMA控制器是常见的总线设备之一,很多厂商都有自己的DMA控制器IP核。比如嵌入式处理器的龙头ARM公司就有自己的DMA控制器解决方案提供给客户,另外像Freescale,Fujitsu等芯片制造厂商都有自己的解决方案。本文通过介绍一种基于ARM总线之一的AHB总线的DMA控制器的IP核设计,简述了IP核设计的流程和需要重点注意的地方。

功能描述

一般而言,DMA控制器的功能与结构是由本单位特定的系统结构决定的。但是作为IP而言,DMA控制器又要有其一般性。DMA是指外部设备直接对计算机存储器进行读写操作的I/O方式。这种方式下数据的读写无需CPU执行指令,也不经过CPU内部寄存器,而是利用系统的数据总线,由外设直接对存储器写入或读出,从而达到极高的传输速率。现在DMA也可以在内存之间或是外设之间直接进行数据操作。DMA技术的重要性在于,利用它进行数据存取时不需要CPU进行干预,可提高系统执行应用程序的效率。利用DMA传送数据的另一个好处是数据直接在源地址和目的地址之间传送,不需要是中间媒介。

通用的DMA控制器应具有一下功能:

1.编程设定DMA的传输模式及其所访问内存的地址区域。

2.屏蔽或接受外设或软件的DMA请求。当有多个设备同时请求时,还要进行优先级排队,首先响应最高级的请求。

3.向CPU或总线仲裁设备提出总线请求。

4.接收总线响应信号,接管总线控制。

5.在DMA控制器的管理下实现外设和存储器、外设和外设或存储器之间的数据直接传输。

6.在传输过程中进行地址修改和传输量计数。当要求的数据传送完后,撤销总线请求,交还总线控制权。

总而言之,DMA控制器一方面可以接管总线,直接在I/O接口和存储器之间进行读写操作,即可以像CPU一样视为总线的主设备,这是DMA与其它外设最根本的区别;另一方面,作为一个I/O器件,其DMA控制功能正式通过初始化编程来设置的。当CPU对其写入或读出时,它又和其它的外设一样成为总线的从属器件。

而作为专用的DMA控制器又会有其特定的功能要求。比如对于AHB总线而言,需要支持Burst操作。另一方面,现在多数支持操作系统的嵌入式系统或计算机系统都使用虚拟内存技术。这一技术的使用使得在操作系统层面上看到内存地址与物理地址间并非一一映射,操作系统层面上连续的内存地址在真实的物理内存上并不一定连续。但是DMA控制器并不一定了解这一现象。为了解决这一问题并提高传输效率,多数在高级嵌入式系统中使用的DMA控制器支持分散/集合LLI(LogicLinkItem)技术。

设计指标本

DMA控制器的主要指标如下:

$16个DMA通道,其中6个为独立的软件通道,另10个为软硬件复用的通道。

$DMA读数据与写数据独立进行。

$各通道独立编程,独立初始化。

$支持软件复位。

$全面支持AHB总线协议。

$支持LLI技术。

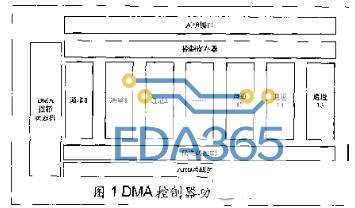

DMA控制器主要包括以下几个模块,其结构图如图1所示。

$APB接口模块:该部分主要实现APB总线读写协议,并通过ARM配置DMA控制器的寄存器。

$控制寄存器模块:该部分通过APB总线进行配置,获得DMA控制器的控制信息。该模块主要由命令控制寄存器、状态寄存器和中断寄存器组成。

$DMA控制状态机模块:本模块是DMA控制器的核心部分,负责发起和中止每一次DMA传输,同时负责每次DMA传输过程中的状态转换。

$通道模块:该模块包含了16个通道,其中10个是软、硬件复用的,另外6个是软件专用的。前者除了有常规的寄存器组外,还要负责检测硬件的DMA传输请求;而后者则没有这部分功能,但后者要支持LLI功能。常规的通道寄存器组由各个通道的源地址、目的地址、传输长度以及通道控制寄存器等组成。

$优先级控制模块:本模块有状态寄存器和请求寄存器。ARM通过编程确定各个通道的优先级顺序。当有多个DMA请求同时出现的时候,通过此模块确定哪个请求优先被响应。

$AHB总线接口模块:本模块负责实现AHB总线读写协议。

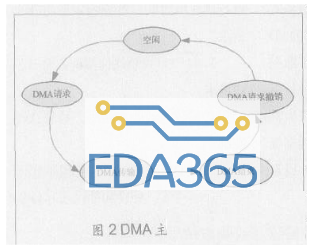

作为DMA控制器有其特殊性,主要体现在它既是总线的从设备,又是总线的主设备。因此,DMA控制器有两个主要的状态——空闲态与工作态。当DMA控制器处于空闲态时,它就相当于一个总线的从设备,受到ARM的管理与控制。ARM通过编程配置DMA控制器的寄存器。

作为嵌入式系统常用的AMBA总线结构和一般的计算机系统有一定的区别。AMBA总线控制权是由总线仲裁器给予的,DMA控制器与CPU一样,向总线仲裁器提出总线使用需求,总线仲裁器根据优先级算法决定是否给予总线使用权。而一般计算机系统默认CPU控制总线,若DMA有占用总线的需求是直接向CPU提出申请。

DMA主状态机如图2所示。当有硬件或软件提出DMA传输请求时,DMA控制器将转到工作态的第一个子状态——准备状态,DMA向总线仲裁器发出总线控制请求。若此时总线仲裁器没有更高优先级的总线需求请求,它会将总线控制权交给DMA控制器。当DMA控制器拿到总线控制权后会转到传输状态。根据选定的通道及其寄存器组的要求,进行DMA传输。在传输状态中,DMA读数据部分会率先动作,从源地址读取数据至FIFO中,当FIFO中的数据量够一次Burst操作后,写数据部分会行动,将数据从FIFO中写到目的地址所对应的模块中。若图2DMA主状态机FIFO满,则自动停止读数据,若FIFO空则自动停止写数据。当读数据部分完成了此次DMA传输要求的长度后,状态机进入下一个子状态,等待写数据部分将数据全部写完。当完成全部操作后,DMA控制器会向发起DMA传输请求的设备发出信号,告知DMA传输顺利完成,要求该设备撤销DMA传输请求,并归还总线控制权。至此DMA控制器回到空闲状态,等待下一次DMA传输请求。

一般而言,DMA控制器在总线仲裁器中是优先级最低的设备。因此,当有其它更高优先级的总线主设备要求总线资源时,DMA控制器会被剥夺总线使用的权利,此时DMA控制器将进入等待状态,直到优先级更高的总线主设备释放总线控制权后再进入传输状态。

当软件提出申请,完成内存之间的大量DMA传输时,一般会使用LLI功能。LLI功能针对的虚拟内存空间与物理内存空间映射的不一致性,为了提高传输性能而引入的一种传输机制。作为LLI传输,ARM需要编程给DMA控制器,告知LLI列表的地址,并启动DMA传输。当DMA控制器发现是LLI传输时,它会到LLI列表中读取第一次DMA传输的源地址、目的地址、传输长度以及下一个LLI列表的地址并存入寄存器。当此次DMA传输结束后,DMA控制器会自动到下一个LLI列表中读取下一次DMA传输的信息。这个链表传输过程直到LLI寄存器中的内容为“0”时中止。

根据AMBA协议,AHB总线支持字节、半字和全字操作。因此DMA控制器在这点上符合AHB协议的要求DMA控制器默认32位数据线,因此需要根据读写地址以及读数据操作类型将读入的数据放入32位的FIFO中,写出的时候再根据地址和写数据的操作类型将数据从FIFO中放到写数据总线上。如字节操作时,根据读地址从读到的一个字的数据中选取合适的字节放到FIFO中的最低字节;写的时候从FIFO最低部分取数,根据写地址将此字节放到写数据相应的部分,其余位补零。

作为ASIC而言,一般情况下,三态只用于输入输出的管脚上。即使是总线在芯片内部也是将读数据线与写数据线分开使用的。本设计秉承这一原则,将读写数据线分开。

作为DMA传输,地址的变更需要灵。有时候读写地址需要增加,有时候地址需要不变。当增加的时候,也要根据传输的类型决定地址增加1、2或4

复位是ASIC设计中最容易出问题的一环。DMA控制器主要有两种复位方式,一种是上电复位,即异步复位,另一种是软件复位,即同步复位。

异步复位通过将全部D-触发器的Reset端接到复位信号线上,无需时钟就可以实现的复位。一般情况下在上电的时候作一次。而根据功能的需要当系统出现故障,或软件需要强行中止一次DMA传输的时候,则需要软件通过配置寄存器实现复位功能。此时就需要同步复位。

由于DMA控制器工作在高速总线上,总线时钟最高可以达到200M,故在做前端设计的时候要特别注意。

以优先级判断为例。优先级判断本质就是16个数字比大小。为了使时间复杂度最小,不采取经典的“冒泡排序”,而是对半排序法。这样比较4次就可以得到需要的数据。四级MUX对于低频而言不算很困难,但是对于高频而言,为了能够满足时序要求,就需要在第二次比较之后插入一组触发器。

本文讨论了一种基于AMBA总线的DMA控制器的IP核设计,结合这个实际的设计,讨论了IP复用技术的设计方法。这个设计不依赖于具体的FPGA或ASIC型号或工艺,因此其可移植性被大大增加。另一方面本设计综合出来的DMA控制器是20K门,比起ARM公司的DMAC控制器的68K门,在面积方面也有很大的优势。

IP复用技术越来越成为嵌入式系统的发展趋势。这种设计方法顺应了超大规模集成电路的发展潮流,必将成为这一领域发展的方向。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多