1.引言

当前以硬件描述语言为工具、逻辑器件为载体的系统设计越来越广泛。在设计中,状态机是最典型、应用最广泛的电路模块,其在运行速度的高效、执行时间的确定性和高可靠性方面都显现出强大的优势。状态机及其设计技术水平决定了系统设计的优劣[1]。如何设计一个最优化的状态机是我们必须面对的问题。

本文将详细讨论状态机编写的各个步骤对优化状态机所起到的作用。

2.状态机的分类

状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作,完成特定操作的控制中心。

状态机可以分为Moore型和Mealy型两种基本类型。设计时采用哪种方式的状态机要根据设计的具体情况决定,输出只由当前状态值决定则选用Moore型,输入信号和状态值共同决定输出则选用Mealy状态机。

设计时在结构上通常遵循一下几点:

各模块只描述一个状态机;将无关逻辑减至最少;将状态寄存器从其他逻辑中分离出来[2]。

3.状态值编码方式

通常在设计状态机时,状态编码方式的选择是非常重要的,选得不好,可能会导致速度太慢或占用太多逻辑资源。实际设计中,必须考虑多方面因素选择最为合适的编码方式。

3.1 枚举类型定义状态值

设计中状态机的状态值定义为枚举类型,综合时一般转化为二进制的序列,因此与二进制编码方式本质上是相同的。

实际需要触发器的数目为实际状态的以2为底的对数。这种编码方式最为简单,综合后寄存器用量较少,剩余状态最少,其综合效率和电路速度在一定程度上将会得到提高。但在状态转换过程中,状态寄存器的高位翻转和低位翻转时间是不一致的,这样就会出现过渡状态,若状态机的状态值更多的话,产生过渡状态的概率更大。因此适合复杂度较低的设计。

3.2 格雷码表示状态值

格雷码编码,即相邻两个状态的编码只有一位不同,这使得采用格雷码表示状态值的状态机,可以较大程度上消除由传输延时引起的过渡状态。

该方式使得在相邻状态之间跳转时,只有一位变化,降低了产生过渡状态的概率,但当状态转换有多种路径时,就无法保证状态跳转时只有一位变化。所以在一定程度上, 格雷码编码是二进制的一种变形,总体思想是一致的。

3.3“ONE-HOT”状态值编码

One-hot编码方式是使用N个触发器来实现N个状态的状态机,每个状态都由一个触发器表示,在任意时刻,其中只有1位有效,该位也称为“hot”,触发器为‘1’,其余的触发器置‘0’。

这种结构的状态机其稳定性优于一般结构的状态机, 但是它占用的资源更多。其简单的编码方式简化了状态译码逻辑,提高了状态转换速度,适合于在FPGA 中应用。

3.4 剩余状态与容错技术

在状态机设计中,不可避免地会出现大量剩余状态。若不对剩余状态进行合理的处理,状态机可能进入不可预测的状态,后果是对外界出现短暂失控或者始终无法摆脱剩余状态而失去正常功能。因此,对剩余状态的处理,即容错技术的应用是必须慎重考虑的问题。但是,剩余状态的处理要不同程度地耗用逻辑资源,因此设计者在选用状态机结构、状态编码方式、容错技术及系统的工作速度与资源利用率方面需要做权衡比较,以适应自己的设计要求。

剩余状态的转移去向大致有如下几种:

a)转入空闲状态,等待下一个工作任务的到来;

b)转入指定的状态,去执行特定任务;

c)转入预定义的专门处理错误的状态,如预警状态。

对于前两种编码方式可以将多余状态做出定义,在以后的语句中加以处理。处理的方法有2种:①在语句中对每一个非法状态都做出明确的状态转换指示;②利用others语句对未提到的状态作统一处理。对于One-hot编码方式其剩余状态数将随有效状态数的增加呈指数式剧增,就不能采用上述的处理方法。鉴于One-hot编码方式的特点,任何多于1个触发器为“1”的状态均为非法状态。因此,可编写一个检错程序,判断是否在同一时刻有多个寄存器为“1”,若有,则转入相应的处理程序。

4.状态机的描述方法

VHDL对不同的状态机有不同的描述方式,描述方式不同使得综合出来的门级网表也不同,因此必须根据数字电路的特性和可综合性选择相应的状态机描述方式。

下面以实践中激光测距仪中心控制器为例,介绍不同描述方法的设计,并给出仿真图。

将整个状态机写到1个进程模块里,在该模块中既描述状态转移又描述状态的输入输出,称为一段式描述方法,即所谓的单进程状态机。其将组合逻辑和时序逻辑在一个进程中描述,该方式的唯一优点是可得到锁存后的输出信号。但在描述当前状态时需考虑下一个状态的输出,整个代码不清晰,不易于理解、维护,也不利于时序约束、功能更改、调试等,而且不能很好的表示Mealy状态机的输出,容易导致逻辑功能错误。另外,这种描述相对于另外两种描述比较冗长。因此一段式描述是应当避免的描述方式,这里也不再做进一步讨论。

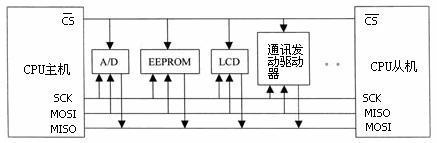

采用2个进程模块,一个模块用同步时序描述状态转移;另一个模块用组合逻辑判断状态转移条件、描述状态转移规律及逻辑输出,称为两段式描述方法,这是综合器理解最好的一种描述方式,也是要求不高的条件下最常用的一种。分析其结构概括为图1所示框图。

设计的控制器时序仿真如图2所示。

由图2可以看到direct输出信号出现毛刺,对于精密控制器来说这是不允许的。毛刺多由组合逻辑导致的,若在输出部分加入一个寄存器节拍,可消除毛刺保证输出信号的稳定性,但输出就会延迟一个周期,所以当时序允许时该方式是很好的选择。

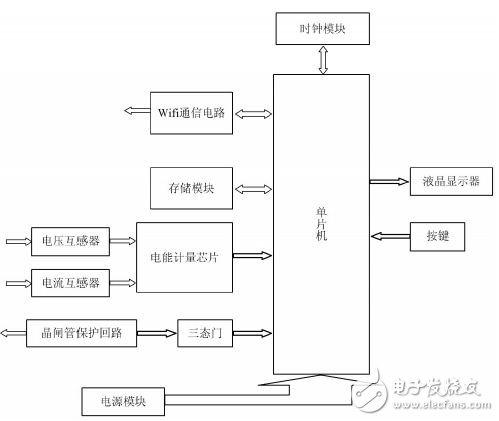

使用3个进程模块,一个模块采用同步时序描述状态转移;第二个采用组合逻辑判断状态转移条件,描述状态转移规律;第三个模块使用同步时序电路描述每个状态的输出,该写法称为三段式写法。分析其结构概括为图3所示框图。

改进后的控制器时序仿真如图4所示。

三段式与两段式描述相比,虽然代码结构复杂了一些,但是换来的优势是做到了同步寄存器输出,消除了组合逻辑输出的不稳定与毛刺的隐患,而且更利于时序路径分组,在FPGA上的综合与布局布线效果更佳。

一般而言,推荐的状态机描述方法是后两种。其原因:设计最好使用同步时序方式,以提高设计的稳定性,消除毛刺。状态机实现后,状态转移部分是同步时序电路而状态的转移条件的判断是组合逻辑。两段式描述方法虽然有很多好处,但一个明显的弱点就是其输出使用组合逻辑描述,易产生毛刺等不稳定因素,并且在逻辑器件中过多的组合逻辑会影响实现的速率,而三段式巧妙地根据下一状态的判断,用同步时序逻辑寄存状态机的输出。

5.毛刺和竞争处理

毛刺的产生,一方面由于状态机中包含有组合逻辑进程,使得输出信号在时钟的有效边沿产生毛刺;另一方面当状态信号是多位值的时候,由于传输延迟的存在,各信号线上的值发生改变的时间会有先后,使得状态迁移的时候出现临时状态。当状态机的输出信号作为其他功能模块的控制信号使用时, 将会使受控模块发生误动作, 造成系统工作混乱。因此,在这种情况下必须通过改变设计消除毛刺。

消除状态机输出信号的“ 毛刺”一般可从一下几点改进:

①在电路设计时,选用延迟时间较小的器件,且尽可能采用级数少的电路结构;或者把时钟信号引入组合进程,用时钟来同步状态迁移, 保证了输出信号没有毛刺,但这样增加了输出寄存器, 硬件开销增大, 这对于一些寄存器资源较少的目标芯片是不利的;而且还会限制系统时钟的最高工作频率; 由于时钟信号将输出加载到附加的寄存器上, 所以在输出端得到信号值的时间要比状态的变化延时一个时钟周期。

②调整状态编码, 使相邻状态间只有1位信号改变,避免毛刺的产生。

③直接把状态机的状态码作为输出信号,即采用状态码直接输出型状态机, 使状态和输出信号一致, 使得输出译码电路被优化掉了。这种方案, 占用芯片资源少, 信号与状态变化同步, 速度快, 是一种较优方案。但在设计过程中对状态编码时可能增加状态向量, 出现多余状态。虽然可用CASE语句中WHEN-OTHERS 来安排多余状态, 但有时难以有效控制多余状态, 运行时可能会出现难以预料的情况。因此它适用于状态机输出信号较少的场合。这种方式的缺点是削弱了设计的可读性和可维护性[3]。

有限状态机综合中的竞争现象是指由于敏感信号的频繁变化导致状态机在同一个节拍内多次改变状态,影响电路的正常工作。当输出信号反馈回来作为输入信号的时候,就会发生竞争。这里要指出的是在综合前模拟的时候往往不能发现描述中潜在的竞争现象,只有在综合后,竞争才会完全暴露出来。消除竞争的办法是把造成竞争的信号从敏感信号表中除去,而改成由时钟信号来触发进程,这样就使状态一个节拍只改变一次[4]。

6.状态机的优化

优化的目标主要有两个: 速度和规模,但是速度条件越苛刻, 所需规模就越大, 因此优化电路结构时, 应综合考虑各方面因素, 选择最优化方案。电路结构分为逻辑电路和时序电路。逻辑电路的优化包括布尔表达式的优化等, 时序电路包括通常的时序电路和状态机。状态机优化包括选择合适状态和编码等, 比如合理的归并以及减少状态的数量等都能大大简化电路,在编程时应尽量把可归并的逻辑放入同一结构体中, 这样可以有效优化电路结构[5]。

7.结论

有限状态机是数字系统的一个重要组成部分。本文详细讨论了状态机各部分及应注意的事项和各种不同写法的优缺点。以上只是作者在项目设计实践中学习并总结的一些经验与体会,设计时需根据实际情况做适合的选择。

参考文献

[1] 吴继华,王诚.《Verilog设计与验证》[M],北京:人民邮电出版社,2006。

[2] 王巍,高德远.有限状态机设计策略 [J].计算机工程与应用,1999,7:54-55.

[3] 鲁玲,刘大年.消除状态机毛刺策略探讨 [J] .电子技术应用,2006,9:118-119.

[4] 李春霞,顾新,王君.有限状态机的VHDL 描述及综合 [J].计算机工程与应用,2005,6:111-113.

[5] 骆珊,黄明达.VHDL 电路结构优化设计探讨 [J] .计算机应用,2001,4:14-15.

APP下载

APP下载 登录

登录

热门文章

热门文章