短波通信又称高频通信,是利用HF波段(3-30MHz)电磁波进行的无线电通信。短波通信主要靠天波传播,可经电离层一次或数次反射,最远可传至上万里,如按气候、电离层的电子密度和高度的日变化以及通信距离等因素选择合适频率,就可用较小功率进行远距离通信。短波通信设备较简单,机动性大,因此也适应于应急通信和抗灾通信。现代短波通信接收机正向着数字化、大通信带宽方向发展。文献[1-3]研究了短波通信的数字化实现方式,但其未对短波通信的大带宽应用进行探讨;文献[4-6]研究了通信信道化算法,其对一定带宽内的多信道高效算法进行了详细的讨论,并给出了具体实现的有效算法。本文将信道化算法应用于短波通信,研究采用信道化算法基于FPGA 的短波通信接收机及其具体实现方案,为未来短波通信发展的研究,进行初步的理论探索。

1 短波数字通信接收机

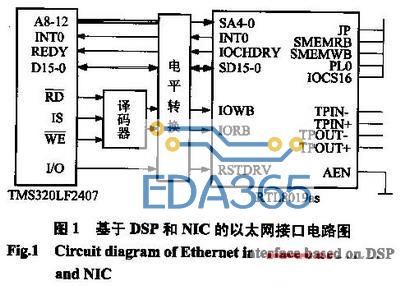

常规短波数字通信接收机由模拟前端、模数转换器(ADC)、数字下变频(DDS)以及数字信号处理(DSP)等四部分组成,其结构如图1 所示。短波数字通信接收机的模拟前端对输入的3-30MHz 模拟信号进行滤波、放大等处理,然后将处理后的回波信号利用ADC 进行采样,再将采样后得到的数字信号送入DDS 进行数字下变频,以得到可以利用DSP 进行处理的低速信号,最后将经过数字下变频的数字信号送入DSP 等数字信号处理芯片进行数字信号处理,解调出通信语音等有用信息。

图1 短波数字通信接收机结构示意图

常规短波数字通信接收机的数字信号处理部分通常由DSP芯片来实现,由于DSP的处理能力有限,因此一般需要先进行数字下变频,以降低数据率,从而满足DSP的处理能力。然而这种结构存在硬件设计复杂,且通信带宽较低等缺点。

2 基于FPGA 的短波通信接收机

2.1 短波通信接收机信道化数学模型

信道化接收是指对整个带宽信号进行信道划分,以实现对任意信道信号的接收,短波通信信道化接收机将整个3-30MHz带宽划分为N个均匀的信道,如图2所示。然后可以同时对任意一个信道中的信号进行接收,从而实现较大的通信带宽。

图2 信道分配图

由图2可知,为了可以对任意一个信道中的信号进行接收,首先需要将任意一个信道中的信号或者同时将几个信道中的信号解调到视频,因此基于图1中固定的一个DDS的硬件结构在信道化接收机中不再适用,同时解调多个信道的信号对后续的信号处理又提出了新的难题,因此急需提出一种新的短波通信接收机,以解决目前短波通信中存在的问题。

2.2 基于FPGA 的短波通信接收机

根据上节的分析,本节提出基于FPGA的信道化接收机模型,其结构如图3所示。由于FPGA具有高度的灵活性以及高速的信号处理能力,其完全可以实现多路DDS以及后续的信号处理,且可以根据实际应用需求,可以通过提高芯片的规模来实现更复杂、更大带宽的短波通信。

图3 基于FPGA 的短波通信接收机系统方案

其中FPGA实现多路DDS下变频以及后续的信号处理解调算法,利用FPGA 的灵活性和实时性实现短波通信的信道化算法,从而在理论上实现了真正的软件无线电短波通信接收机。

3 结论

短波数字通信接收机随着现代电子技术的进步而得到了极大的发展。本文提出的基于FPGA的短波通信接收机,利用信道化技术以及FPGA 的高实时性,实现了对带宽内任意信道信号的解调。本文提出的基于FPGA的短波通信接收机从结构到算法上第一次完整实现了基于软件无线电的短波通信接收机。

APP下载

APP下载 登录

登录

热门文章

热门文章