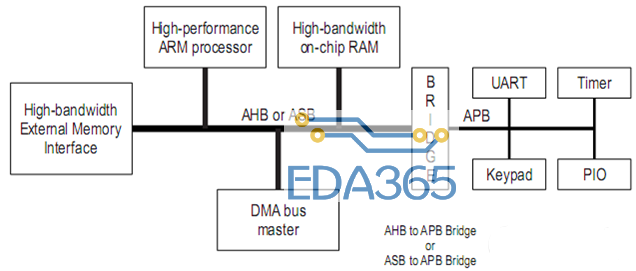

高级微控制器总线结构Advanced Microcontroller Bus Architecture(AMBA)定义了高性能嵌入式微控制器的通信标准。可以将RISC处理器集成在其他IP芯核和外设中,它是有效连接IP核的“数字胶”,并且是ARM复用策略的重要组件。它不是芯片与外设之间的接口,而是ARM内核与芯片上其他元件进行通信的接口。比如Xilinx公司的Zynq芯片,就是ARM与FPGA之间的连接通路。

AMBA3.0 协议:

1 Advanced High-performance Bus (AHB)

AHB总线用于高性能,高时钟工作频率模块。AHB在AMBA架构中为系统的高性能运行起到了基石作用。AHB为高性能处理器,片上内存,片外内存提供接口,同时桥接慢速外设。高性能,数据传输,多总线主控制器,突发连续传输,分步传输。

AHB总线协议是AMBA的新一代总线协议,支持多种高性能总线主控制器。

特性:

a 突发连续传输

b 分步传输

c 支持多个主控制器、单周期内主控制器处理

d 单时钟边沿操作

e 非三态操作

f 支持64位,128位总线

g 支持字节,半字节和字的传输。

AHB总线通过DMA和DSP,允许在总线上存在一个或多个主控制器。虽然APB总线上可以挂接慢速外设,但是也允许在AHB上挂接一些慢速外设作为从设备,不过它们通常还是挂接在APB总线上。

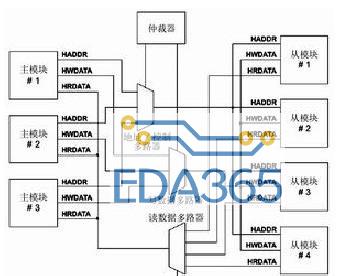

AHB总线通常设计时包含以下几个设备:

a AHB主控制器:主控制器可以通过地址和控制信息,可以进行初始化,读,写操作。在同一时间,总线上只能有一个主控制器。

b AHB从设备:从设备通常是指在其地址空间内,响应主控制器发出的读写控制操作的被动设备。通过操作的成功与否反馈给其主控制器,完成数据的传输控制。

c AHB仲裁器:仲裁器根据用户的配置,确保在总线上同一时间只有一个主控制器拥有总线控制权限。AHB总线上只能有一个仲裁器。

d AHB译码器:译码器解析在总线上传输的地址和控制信息。AHB总线上只能有一个译码器。

2 Advanced System Bus (ASB)

ASB总线主要用于高性能系统模块。ASB是可用于AHB不需要的高性能特性的芯片设计上可选的系统总线。ASB也支持高性能处理器,片上内存,片外内存提供接口和慢速外设。高性能,数据传输,多总线主控制器,突发连续传输。ASB总线是位于APB总线架构之上的用于高性能的总线协议,它有如下特点:

a 突发连续传输

b 单管道数据传输

c 多总线主控制器

3 Advanced Peripheral Bus (APB)

APB总线用于为慢速外设提供总线技术支持。

APB是一种优化的,低功耗的,精简接口总线,可以技术多种不同慢速外设。由于APB是ARM公司最早提出的总线接口,APB可以桥接ARM体系下每一种系统总线。低功耗,寻址控制,支持简单接口协议,支持多种外设。APB通过桥接高带宽、高性能总线,提供基本的微控制器二级总线,通常该总线上的外设有以下特点:支持映射寄存器接口,对带宽没有很高的要求,通过编程实现对外设进行控制。

APB总线接口协议是AMBA协议层次结构中的一部分,它是高度优化的连接低功耗外设的精简接口。

APB看起来是一个本地的二级总线接口协议,用作AHB,ASB总线协议的从设备接口。

APB桥是从控制器模块用来保证不同总线数据的有效传输和不同总线上控制信号的转发处理。

APB应该用于连接低带宽,且不需求高性能数据传输的外设。最新的APB总线协议规定了所有的信号传递都发生在时钟的上升沿。这样设计有以下优势:

a 易于实现高频率操作

b performance is independent of the mark-space ratio of the clock

c 通过单时钟操作简化静态时序

d no special considerations are required for automatic test insertion

e 许多ASIC库在上升沿寄存器有更好的选择

f 简化整合的时钟模拟器

上述的优势也说明APB总线可以更好的链接最新的AHB总线接口。

APB总线协议包含一个APB桥,它用来将AHB,ASB总线上的控制信号转化为APB从设备控制器上可用信号。APB总线上所有的外设都是从设备,这些从设备有以下特点:

a 接收有效的地址和控制访问

b 当APB上的外设处于非活动状态时,可以将这些外设处于0功耗状态

c 译码器可以通过选通信号,提供输出时序(非锁定接口)

d 访问时可执行数据写入

APB主要用于低带宽的周边外设之间的连接,例如UART、1284等,它的总线架构不像AHB支持多个主模块,在APB里面唯一的主模块就是APB 桥。其特性包括:两个时钟周期传输、无需等待周期和回应信号、控制逻辑简单,只有四个控制信号。APB上的传输可以用如图3所示的状态图来说明。

1) 系统初始化为IDLE状态,此时没有传输操作,也没有选中任何从模块。

2) 当有传输要进行时,PSELx=1,PENABLE=0,系统进入SETUP状态,并只会在SETUP 状态停留一个周期。当PCLK的下一个上升沿时到来时,系统进入ENABLE 状态。

3) 系统进入ENABLE状态时,维持之前在SETUP 状态的PADDR、PSEL、PWRITE不变,并将PENABLE置为1。传输也只会在ENABLE状态维持一个周期,在经过SETUP与ENABLE状态之后就已完成。之后如果没有传输要进行,就进入IDLE状态等待;如果有连续的传输,则进入SETUP状态。

4 基于AMBA的片上系统

大多数挂在总线上的模块(包括处理器)只是单一属性的功能模块:主模块或者从模块。主模块是向从模块发出读写操作的模块,如CPU,DSP等;从模块是接受命令并做出反应的模块,如片上的RAM,AHB/APB 桥等。另外,还有一些模块同时具有两种属性,例如直接存储器存取(DMA)在被编程时是从模块,但在系统读传输数据时必须是主模块。

如果总线上存在多个主模块,就需要仲裁器来决定如何控制各种主模块对总线的访问。虽然仲裁规范是AMBA总线规范中的一部分,但具体使用的算法由RTL设计工程师决定,其中两个最常用的算法是固定优先级算法和循环制算法。AHB总线上最多可以有16个主模块和任意多个从模块,如果主模块数目大于16,则需再加一层结构(具体参阅ARM公司推出的Multi-layer AHB规范)。

APB 桥既是APB总线上唯一的主模块,也是AHB系统总线上的从模块。其主要功能是锁存来自AHB系统总线的地址、数据和控制信号,并提供二级译码以产生APB外围设备的选择信号,从而实现AHB协议到APB协议的转换。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多