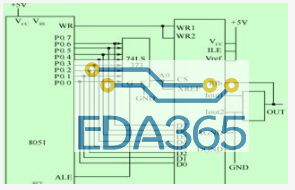

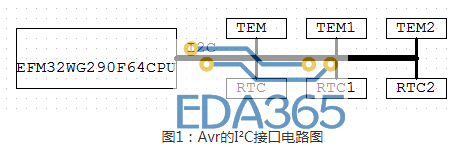

对于硬件工程师,I²C再熟悉不过了,两根线,一根数据SDA一根时钟SCL。当时在使用avr CPU设计数据采集器产品的CPU主板,外挂了Silicon lab的温湿度传感器Si7013,实时时钟,主要实现温湿度、时钟及电流电压等信号通过I²C总线到达CPU进行处理,并且由MCU EFM32WG290F64控制在液晶上和上位机界面上的CPU自带的I²C总线外挂的六个I²C从设备,如下图1所示。

最初时候,此CPU主板的I²C接口仅挂了实时时钟和温度芯片,采用CPU自带的I²C接口。在调试时,波形都比较正常,上升沿和下降沿都能符合要求,通常跑的速率为100KHz。然而后期改版,需要在I²C接口上增加四个I²C设备,线路也相应地变长,在调试的时候,就发现CPU主板上电后,I²C工作异常,偶尔会读不到任何信息。

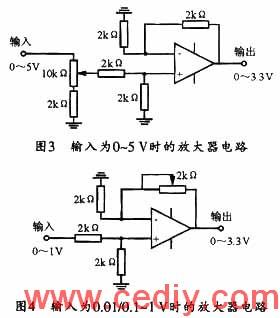

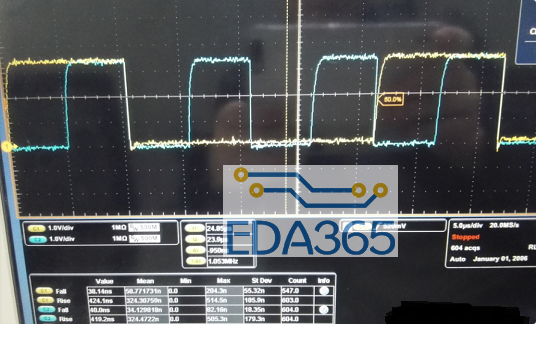

经过了长时间的查问题阶段,发现通过I²C接口的SDA和SCL上拉电阻的大小与放置位置都是有讲究的。通常I²C上拉电阻放在CPU引出的位置,若没有外挂的I²C芯片就不需要加上拉电阻,这点在我们的CPU主板是没有问题的。然后就是上拉电阻,这个通常讲的就是与速率有关,我们将上拉电阻从4.7K,2.2K,1K甚至几百欧姆都测试过,在1K和2.2K的情况下,上升沿和下降沿会比较陡一点。速率100KHZ下采用2.2K的上拉电阻测试出的I2C波形,如图2所示。

最终测出的情况,在上拉电阻为4.7K的时候,速率在100KHZ,波形是正常的;在2.2K的时候,速率在100Khz的时候,波形也是正常;在1K的时候,速率为400Khz,波形也正常;在470欧姆的时候,速率为400KHZ,波形就会畸变。我们采用的上拉2.2K,速率为100KHZ的接口,仍出现CPU板电后I²C工作异常,读不到任何异常信息。后发现是SDA被一直拉低了,SCL一直为高,I²C被死锁了。

为了解决这种问题,在网络上找到一种采用IO模拟I²C的方式,调试了一周后,发现这个问题得到了解决。将I²C接口当做普通IO来操作可能是改动最小的一种方式。其实针对这个问题,还有一些办法可以使用:

1)尽量选用带复位输人的I²C从器件。

2)将所有的从I²C设备的电源连接在一起,通过MOS管连接到主电源,而MOS管的导通关断由I²C主设备来实现。

3)在I²C从设备设计看门狗的功能。

4)在I²C总线上增加一个额外的总线恢复设备,用来监视I²C总线。当设备检测到SDA信号被拉低超过指定时间时,就在SCL总线上产生9个时钟脉冲,使I²C从设备完成读操作,从死锁状态上恢复出来。总线恢复设备需要有具有编程功能,一般可以用单片机或CPLD实现这一功能。

由于avr CPU带多个I²C从设备出现死锁的问题,虽然能够通过IO模拟解决问题,但是对于编程来说比较麻烦,IO模拟在高速上面效果并不好。后来更换了Silicon Labs的MCU,型号为EFM32WG290F64,做了一个最小系统板,外围电路不变,I²C死锁问题不再存在,有效地解决了我的I²C问题。采用EFM32WG290F64读到的I²C波形如下:

另外,设计中通过采用了多片温湿度传感器Si7013,精度也非常高,特别在高温条件下,测试的湿度准确率也非常高。其实I²C接口在我们的设计中再常见不过,但在设计中还是要特别注意以下几点,能够充分考虑以下的要点,I²C设计就可以游刃有余。

1)I²C线路的负载电容不能超过400pF;

2)需要满足上升沿和下降沿的时序关系;

3)I²C上拉电阻和速率有着密切的联系,需要选择合理;

4)如何判断死锁的情况,如上面所示,并提供了一系列的解决方案。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多