HDMI是(High Definition Multimedia Interface)的缩写,意思是高清晰度多媒体接口,是一种数字化视频/音频接口技术,适合影像传输的专用型数字化接口,可同时传送音频和影像信号,最高数据传输速度为48Gbps(2.1版),HDMI相较于VGA接口,它传输的信息量大,色彩度高,传输速度快等显著优点。

一般来说驱动HDMI有两种方法,有些开发板是用一颗专用的HDMI芯片ADV7511做HDMI的输出使用,ADV7511 是一款高速高清晰度多媒体接口(High Definition Multimedia Interface HDMI)发送器。 能够处理的数据速率高达165MHz(1080p @60H, UXGA @60Hz), 输出数据速率高达 225MHz。

Digilent官方出品的ZYBO开发板,上面一个双向的HDMI端口,直接连接在PL的引脚上,所以这次博主分享的工程是用ZYBO PL端的IO口模拟HDMI接口,首先先来讲一下HDMI的显示原理主要是TMDS

HDMI 采用和 DVI 相同癿传输原理——TMDS(Transition Minimized Differential signal),最小化传输差分信号。

TMDS 传输系统分为两个部分:发送端和接收端。 TMDS 发送端收到HDMI 接口传来的表示 RGB 信号的24 位并行数据(TMDS 对每个像素的 RGB 三原色分别按 8bit 编码,即 R信号有 8 位,G 信号有 8 位,B 信号有 8 位),然后对这些数据进行编码和并/串转换,再将表示 3 个 RGB 信号的数据分别分配到独立的传输通道发送出去。接收端接收来自发送端的串行信号,对其进行解码和串/并转换,然后发送到显示器的控制端。与此同时也接收时钟信号,以实现同步。

TMDS的原理

每一个 TMDS 链路都包括 3 个传输 RGB 信号的数据通道和 1 个传输时钟信号的通道。每一个数据通道都通过编码算法,将 8 位的视、音频数据转换成最小化传输、直流平衡的 10 位数据。这使得数据的传输和恢复更加可靠。最小化传输差分信号是通过异或及异或非等逡、逻辑算法将原始 8 位信号数据转换成 10 位,前 8 为数据由原始信号经运算后获得,第 9 位指示运算的方式,第 10 位用来对应直流平衡。

一般来说,HDMI 传输癿编码格式中要包含视频数据、控制数据和数据包(数据包中包吨音频数据和附加信息数据,例如纠错码等)。 TMDS 每个通道在传输时要包含一个 2bit 的控制数据、 8bit 的视频数据或者 4bit 的数据包即可。在 HDMI 信息传输过程中,可以分为三个阶段:视频数据传输周期、控制数据传输周期和数据岛传输周期,分别对应上述的三种数据类型。

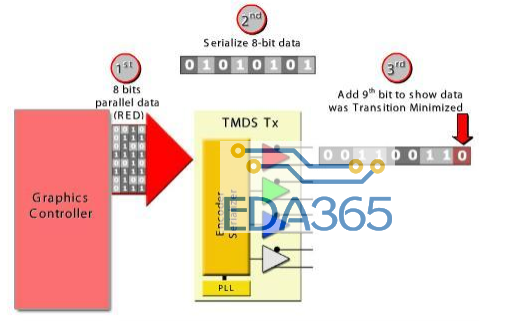

下面介绍 TMDS 中采用的技术:

传输最小化

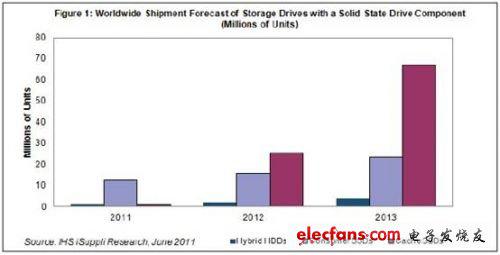

8 位数据经过编码和直流平衡得到 10 位最小化数据,这仿佛增加了冗余位,对传输链路的带宽要求更高,但事实上,通过这种算法得到的 10 位数据在更长的同轴电缆中传输的可靠性增强了。下图是一个例子,说明对一个 8 位的并行 RED 数据编码、并/串转换。

第一步:将 8 位并行 RED 数据发送到 TMDS 収送端。

第二步:并/串转换.

第三步:进行最小化传输处理,加上第 9 位,即编码过程。第 9 位数据称为编码位。

2. 直流平衡

直流平衡(DC-balanced)就是指在编码过程中保证信道中直流偏移为零。方法是在原来的 9 位数据癿后面加上第 10 位数据,返样,传输的数据趋于直流平衡,使信号对传输线的电磁干扰减少,提高信号传输的可靠性。

3. 差分信号

TMDS差分传动技术是一种利用2个引脚间电压差来传送信号的技术。传输数据的数值(“0”或者“1”)由两脚间电压正负极性和大小决定。即,采用 2 根线来传输信号,一根线上传输原来的信号,另一根线上传输与原来信号相反的信号。这样接收端就可以通过让一根线上的信号减去另一根线上的信号的方式来屏蔽电磁干扰,从而得到正确的信号。

另外,还有一个显示数据通道(DDC),是用于读取表示接收端显示器的清晰度等显示能力的扩展显示标识数据(EDID)的信号线。搭载 HDCP(High-bandwidth Digital Content Protection,高带宽数字内容保护技术)的发送、接收设备之间也利用 DDC 线进行密码键的认证。

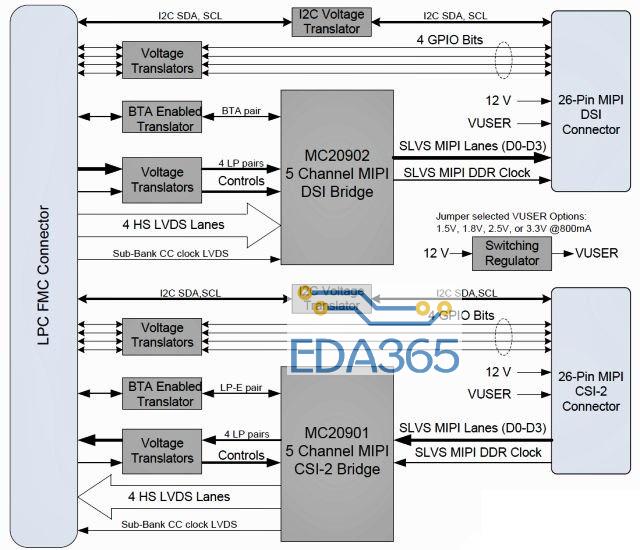

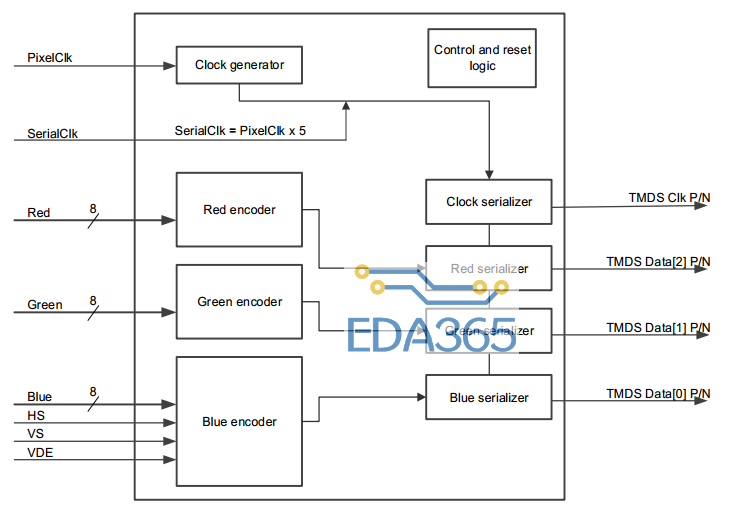

接下来是电路设计部分,HDMI驱动部分追寻原始出处应该是迪芝伦官方,该部分代码用VHDL语言描述,为了方便移植,我将该部分代码封装成自定义IP Core,由上文可知,我们需要产生RGB888三路数据,输入给该模块,然后经过解码、串/并转换,差分输出。还需要两个时钟输入,一个是当前显示分辨率的像素时钟,一个是当前显示分辨率的像素时钟的五倍。还有一个行同步信号和场同步信号,这两个信号的产生方法和VGA是一样的,简单来说就是先产生VGA的信号,行同步信号、场同步信号RGB888的数据输入给HDMI驱动模块就可以显示了,我们要修改显示的数据,还是只需要修改VGA时序即可。

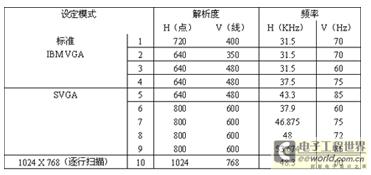

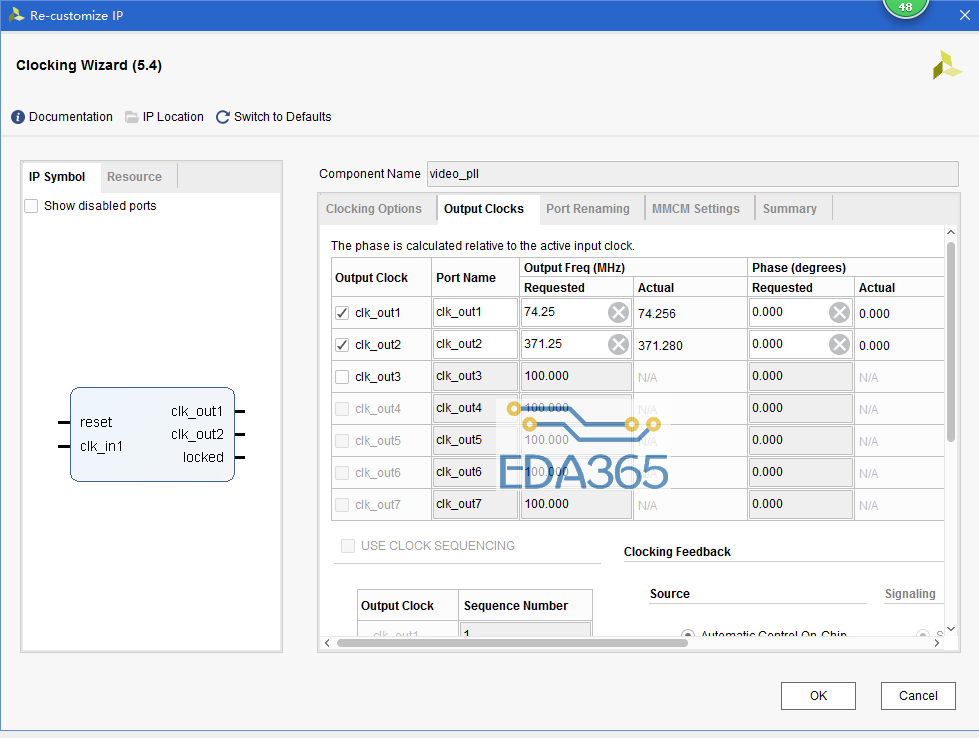

该工程经过测试,可以实现720p(1280x720)的分辨率显示,1080p(1920×1080)的分辨率没有测试出来,原因我觉得可能是官方的zybo的晶振是125Mhz的,这个时钟很尴尬,直接用Clocking wizard锁不出来HDMI所需要的精确时钟,如下图。我试过先分频出100Mhz,然后在调用一个IP Core分频和倍频,但是综合总会报错。所以直接这样进行PLL虽然有误差但是还是可以显示出720p的。

而且根据迪芝伦的官方手册上描述,有这样一段,Resolution up to 720p(1280x720) have been teste。我的英文不是很好,那既然这样说了,没准它还真达不到1080p,好吧不管了,就暂且认为它最高只能达到720p吧。逃~

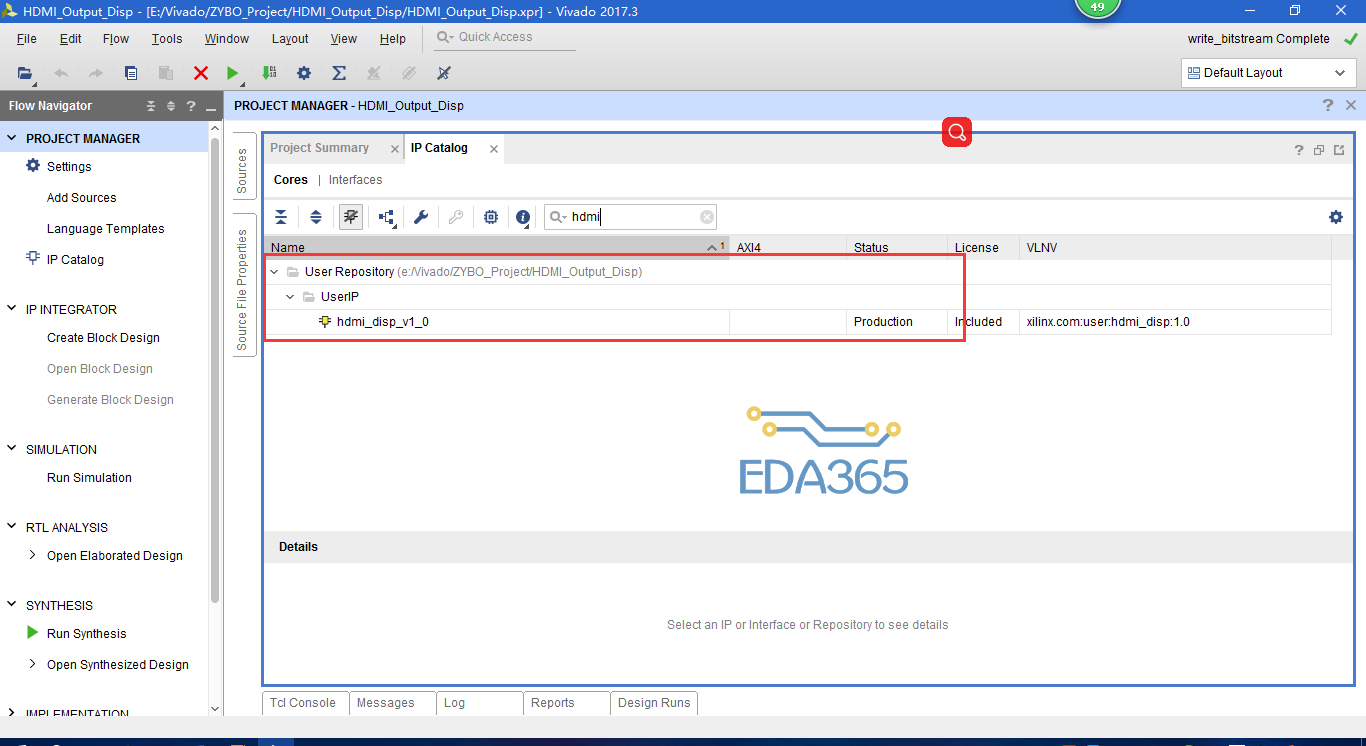

打开工程后,需要重新添加HDMI自定义IP的路径,就在工程中,rgb2dvi_v1_2文件夹中。

然后在IP Catalog中搜索hdmi_disp就可以得到对应的IP Core了。

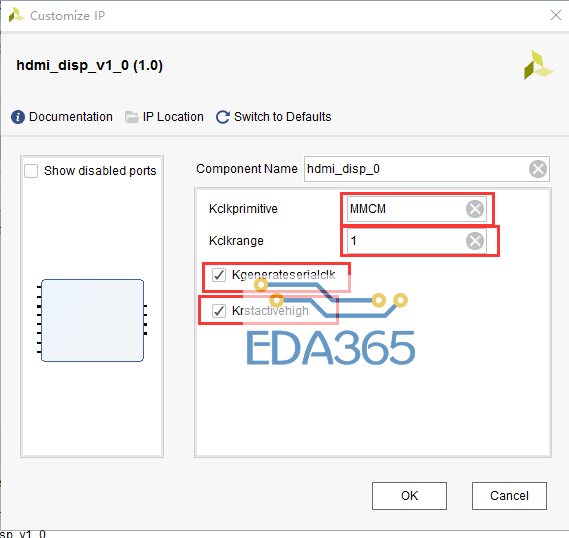

双击打开这四个需要定义的参数,已经定义好在IP中了,直接点击OK——Generate生成

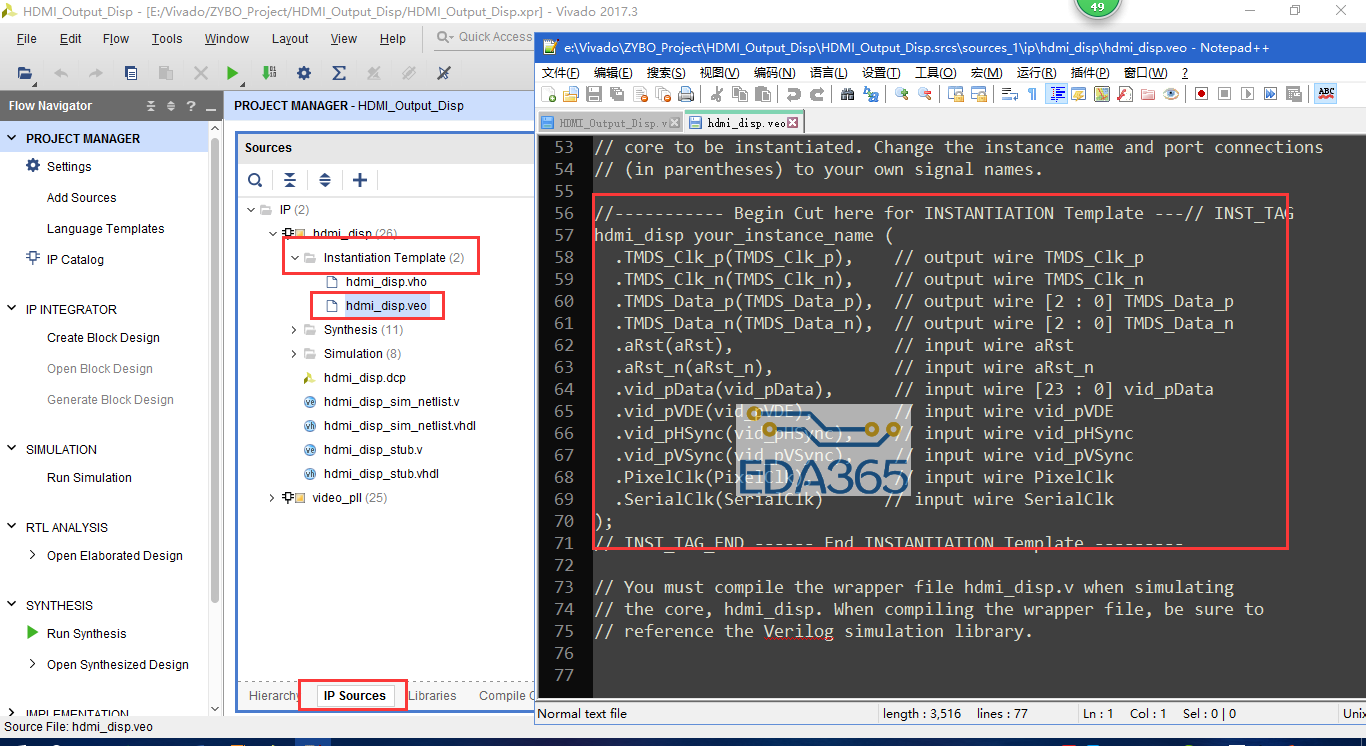

直接可以在如下图所示中找到例化文件,直接实例化即可。

关于引脚约束,需要说的是,引脚约束必须为TMDS_33电平标准

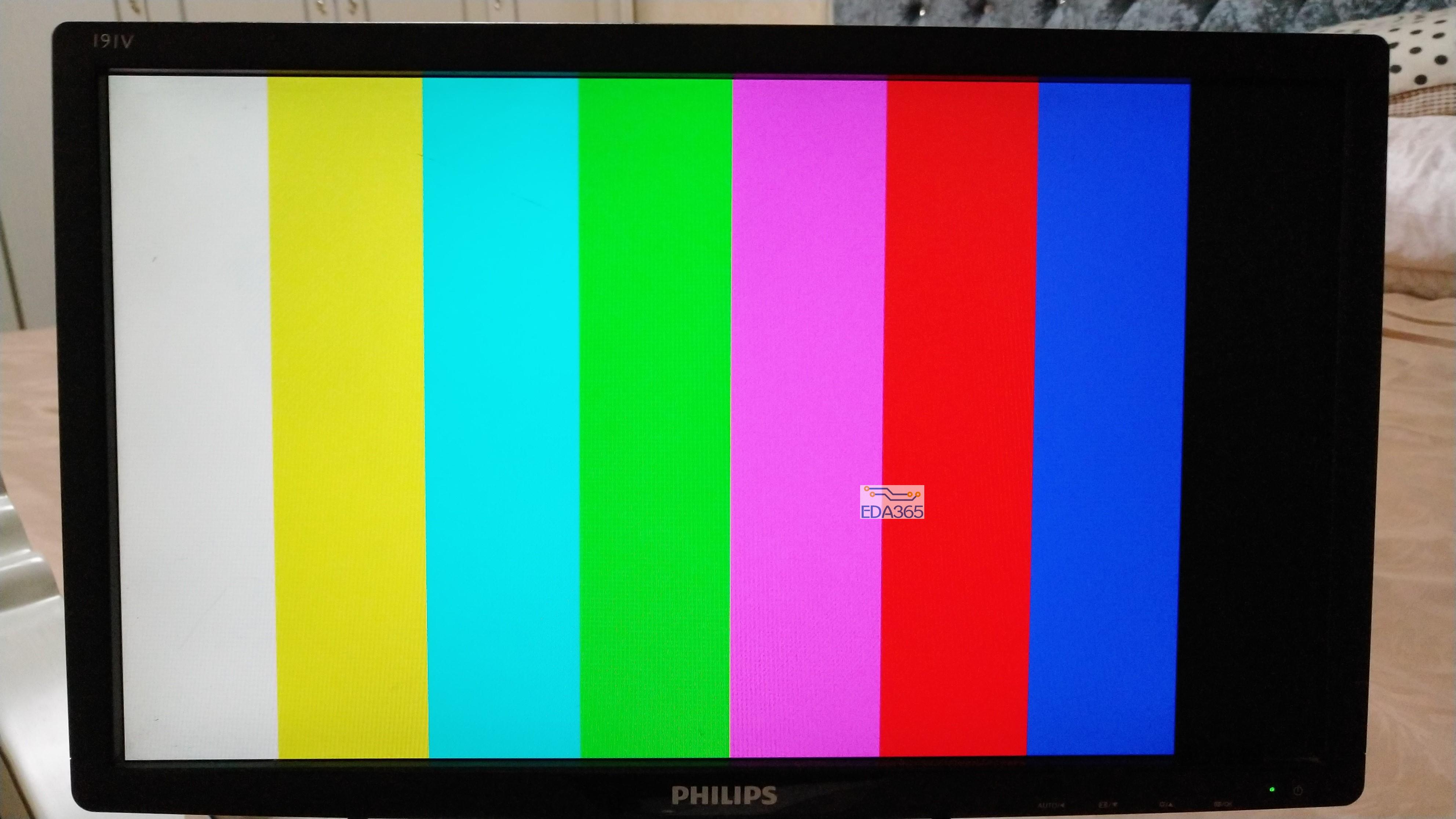

最后附上一张720p彩条测试图。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多