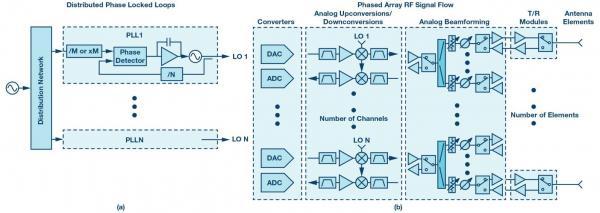

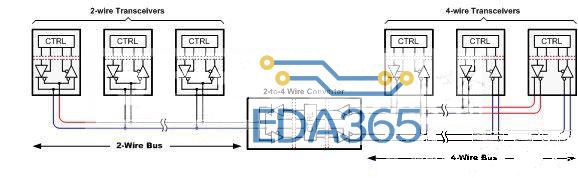

多点数据通信网络,例如:Profibus、Modbus 和 BACnet 等通常均要求具备 RS-485 双线、半双工总线系统与四线、全双工总线系统通用性。这些系统可以扩展至数百米长,并承受较大的接地电位差 (GPD)。这些电位差会超出收发器的共模电压范围,对器件造成损坏。为了消除 GPD,我们利用电隔离型收发器,将总线节点的控制电子组件隔离于连接总线的实际收发器级。图 1 显示了使用 2-4 线转换器的混合网络的结构图。

图 1 2-4 线转换器可确保半双工系统和全双工系统之间的通用性

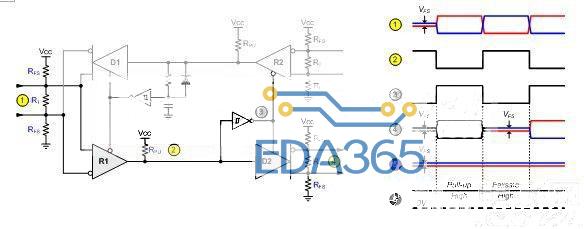

为了使转换器运行不依赖于数据速率,我们通过总线的逻辑状态来控制转换器驱动器和接收器的开启和关闭。总线驱动是以每比特间隔,从而让转换器运行独立于信号数据速率。

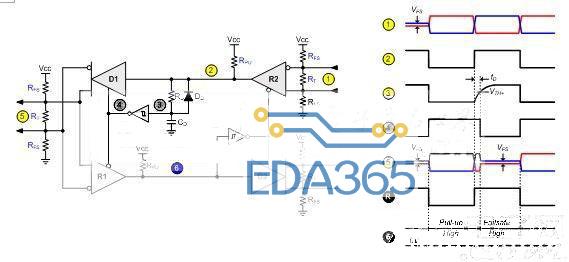

简单的控制逻辑可确保驱动器 D1 和 D2 仅由相反接收器(也即 R1 或者 R2)输出的逻辑低激活启用。因榻邮掌魇淙攵舜嬖 VFS > 200 mV 的总线故障保护电压,所以在总线闲置期间,两个接收器输出均为逻辑高。逆变器栅极将该逻辑高电平反向为低态,并在关闭驱动器的同时启用接收器。

在半到全双工方向(图 2:自左向右),R1 输入端的负总线电压激活驱动器 D2,并对驱动器输入使用低态。D2 通过以一个负输出电压驱动传输总线来做出相应的响应。当 R1 输入的总线电压变为正时,D2 立即失效。但是,它的输出却为高电平,原因是故障保护偏置电阻器 RFS 形成总线电压 VFS。

(请注意,在整个运行期间,R2 的输出始终保持高电平,确保 R1 保持有效而 D1 保持无效。)

图 2 半双工到全双工方向的转换器时序

在全到半双工方向(图 3:自右向左),R2 输入端的负总线电压激活驱动器 D1,并给驱动器输入施加低态。D1 通过以一个负输出电压驱动双线总线做出相应的响应。当 R2 输入的总线电压变为正时,D1 经一段延迟时间后失效。在该延迟时间内,D1 在出现高阻抗前使用一个负电压驱动总线,以防止 R1 输出端出现开关瞬态。

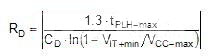

我们建议,RDCD 时间常量产生的最小延迟时间应为驱动器最大传播延迟的 1.3 倍,以补偿组件值、逆变器阈值和电源电压的容差。在给定的电容条件下,可通过方程式 1 确定要求的 RD 值:

方程式 1

其中,tPLH-max 为驱动器 D2 的最大低到高传播延迟,VIT+ min 为施密特触发逆变器的最小正输入阈值,而 VCC-max 为最大供电电压。

在 D1 失效以后,因为有故障保护偏置电阻器 RFS 形成的总线电压 VFS其输出仍为高电平。当 R2 输入端的总线电压恢复负时,由于 CD 通过放电二极管 DD 快速放电D1 立即被激活。图 3 所示时序图显示,半双工总线上一个远程接收器(此处以 R 表示),将负总线电压转换为一个低比特。一个高比特由一个低主驱动正总线电压和剩余故障保护电压 VFS 组成。

图 3 全双工到半双工方向的转换器时序

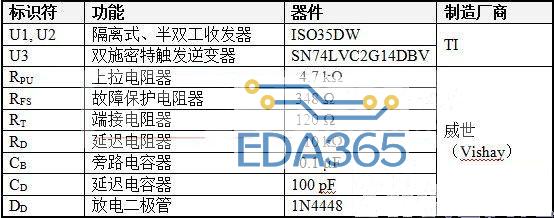

图 4 所示最后一个转换器设计使用两个全双工收发器:一个配置为半双工收发器;另一个则为全双工模式。该转换器拥有高达 200 kbps 的数据速率,并由一个单 3.3 V 电源供电。表 1 为此电路的材料清单 (BOM)。

表1、双到四线转换器 BOM

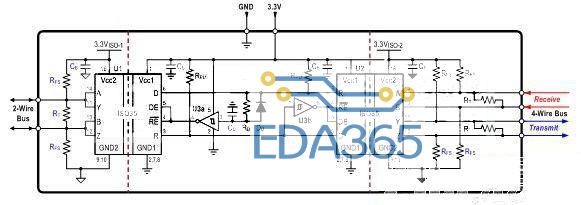

图 4 双隔离式二到四线转换器设计

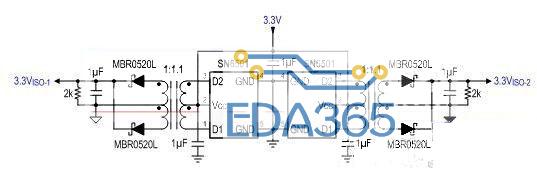

两个转换器端口的收发器级均要求所使用的隔离式电源 VISO-1 和 VISO-2须来自中央 3.3V 电源。图 5 为其原理图。为了避免无负载状态期间出现输出峰值要求,每个整流输出均包括一个大小为 2 kΩ 的最小负载电阻器。

图 5 VISO-1 和 VISO-2 的隔离式电源设计

总结

二到四线转换器可用于将一个单半双工收发器或者一条完整的半双工总线,连接至一个全双工总线。在将二到四线转换器连接至全双工总线时,必须注意的是,在与转换器节点通信时,主控节点的微控制器会改变其全双工到半双工的传输格式。

APP下载

APP下载 登录

登录

热门文章

热门文章