嵌入式无源元件技术的开发源于OEM制造商对减少元件数量、压缩电路板尺寸、增加电路板功能、降低产品总体成本的需求。在电子设备中,无源元件在元件总量中占了相当的比例,其中又以电阻和电容为主。过去,一部典型的GSM手机中含有500多个无源元件,占了电路板面积的一半,并有25%的焊点与此有关。本文描述的EP技术其着重点在于对非关键电阻、电容器和电感进行识别并尽可能多地将它们嵌入HDI-PCB中。

EP技术 开发EP技术有三个主要目的。个目的是开发一种技术,使得无线和便携式产品中现用的无源元件至少可被嵌入30~50%。Motorola研发的EP技术一开始致力于改进嵌入聚合物厚膜(PTF)电阻的方法,以及了解采用HDI电介质(PCC或光通路)以形成简单的平板电容器和2.5匝多层电感的限制条件。其后,他们又致力于开发用于嵌入大数值分立电容器的新型高介电常数材料。

第二个目的是使该技术与传统的HDI-PCB制造工艺和设备相兼容

,以限度地减少投资并加速供应基地的形成。PTF电阻、HDI介电平板电容器和电感的生产均依赖于大多数HDI-PCB制造厂的现有设备。填充了高介电常数陶瓷的光致介电(CFP)"夹层(mezzanine)"电容器要求采用幕涂(curtain coating)或垂直辊涂(vertical roller coating)及溶剂显影(solvent developing)工艺。

第三个目的是使新型的EP技术比现有的其他选择方案更便宜。采用薄金属膜来制造嵌入式电阻已变得较为普遍,但这些材料制成的薄膜电阻范围有限,且货源和制造基地稀缺。同样,现有的电容技术其适用性有限,不允许采用分立电容器,且不易加工。

EP技术与任何的1-X-1或2-X-2 HDI加高工艺(build-up)相兼容。PTF电阻的丝网印刷技术在业界的应用已有几十年的历史,可为大多数PCB制造厂所采用,而且在材料和加工方面都显示出低成本的特点。HDI介电嵌入电容器和电感的适用性受到限制,但它们是HDI加高工艺所固有的,且嵌入时无需额外成本。

下面简述每个可嵌入元件的可靠性和性能。

PTF电阻 商品化的PTF印剂(inks)的改进加上内部开发的工艺改良措施实现了适用范围广、可靠性高的PTF嵌入式电阻技术的推广应用。ASAGU TU-00-8碳酚醛树脂印剂用于制造嵌入式PTF电阻。这种印剂的薄膜电阻率可在每方35 M 之间,并可通过混合以获得位于其间的任何数值。PTF电阻技术允许在同一层上印刷多种印剂,由此获得小至18 、大至10M 的电阻。

传统的做法是把嵌入式电阻直接印刷在蚀刻铜条或丝网银条上。两种电阻生产工艺均不能满足业界对高可靠性和不断增长的空间节约方面的要求。

Motorola公司的EP技术在铜条和丝网印刷PTF电阻之间插入了一种专有材料。采用一种直接沉积在铜条上的界面稳定性助触媒来替代传统的银膏,能够显著地减轻环境应力条件下的电阻漂移,同时保留了光刻制模铜版的边缘轮廓和密度上的优势。

当采用稳定性助触媒时,暴露于85%RH/85℃条件下500小时之后的电阻的总体变化不超过初始值的 10%。而且当置于烘烤条件(125℃,3小时)下时,这一阻值的增加是完全可逆的。因此,不能表示实际工作条件下的器件性能。在单独的测试中,光对电阻进行5X-高温回流焊(峰值温度220℃),随后施以500次的液体-液体热冲击,电阻的变化在 4%以内。

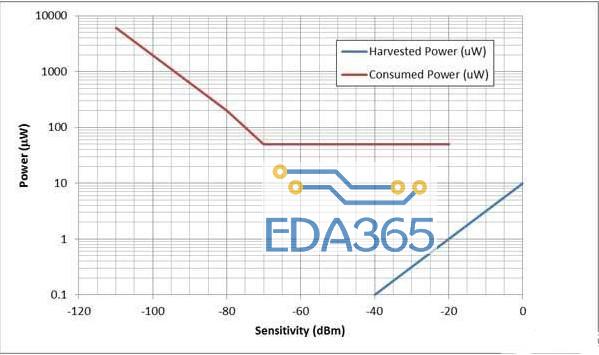

电容器 电容器技术的开发分两个阶段。在技术应用的阶段,HDI电介质被用来做成平板电容器。当电介质厚度为50微米时,典型HDI电介质的电容密度为0.8pF/mm2。这就把合理的可嵌入式电容器的范围限制在12 pF以下。

在该技术应用的第二阶段,通过与Vantico AG公司的合作,共同开发出了一种高介电常数的CFP材料,使得可把分立电容器嵌入在层与外HDI层之间("夹层"电容器由此得名)。

电感

电感技术专注于制作可嵌入范围高达22nH的2匝和2.5匝的多层螺旋电感。开发工作致力于建立用于预测各种RF条件下嵌入式电感特性的数学模型,并确定变化的主要原因。嵌入式螺旋电感的容限在15%~20%之间,且受记录、印刷-蚀刻以及各PCB制造厂对HDI电介质厚度控制能力的影响。

设计根据 用于在任何给定的设计中选出可嵌入的无源元件的方法。选择过程总是始于对材料清单和电原理图的分析。作为确定可嵌入无源元件的初步筛选,首先应分析每个元件的数值和容限,随后对那些在嵌入时对电路功能至关重要的元件进行评估。重要的元件可能是指要求高Q值、高功耗或对噪声敏感的无源元件,以及那些用于对电路功能进行微调的元件。

此外,电气工程师必须决定如何对EP元件进行布局,以使各功能不至相互干扰并由此降低整个电路的功能(交互/寄生电容或电感)。必须进行计算以确定在各个层上是否有足够的空间来嵌入全部被选择的元件。可把EP电路元件相互组合起来,同时把EP元件与SMT元件组合起来,以形成一个总体面积更小、功能相当的模块。

选择完成后,必须比较EP组装模块和等效的SMT模

块的成本。早期的许多EP模块设计采用的是直接替换现有SMT陶瓷RF模块的方法。

新的EP设计不适用于这种简单的比较,因为很多时候非EP替代方案并不存在。尽管如此,对于大多数RF及其他模块应用而言,EP技术已证明是一种降低成本的行之有效的方法。

RF模块的研究 作为降低成本的措施之一,设计了一个EP-RF模块来替代GSM电话中现有的共烧陶瓷模块。该设计采用了PTF电阻、HDI电容器和电感。

EP模块是一个7 9mm元件,其设计采用了与现行陶瓷元件相同的引出线和面积,意在便于将其以表面安装的形式"插入"母板衬底上。模块一半以上的无源元件被嵌入四层HDI/FR4加高结构中。采用两种不同的印剂来嵌入8个电阻。电容器以平板构造嵌入(采用50 m HDI环氧树脂作为电容器电介质)。电感作为单层或双层铜线(copper traces)嵌入。在进行此项设计时(1999年),CFP电容器尚未进入大批量生产阶段,故未能被采用。将EP模块与共烧陶瓷方案(以及替代的SMT方案)相比较,发现EP-HDI模块的电气性能(包括相位噪声)与之相当或更好。

用于说明电路板构造的截面图。一个HDI层被涂敷于20mil的高Tg FR4磁心的两侧。模块的底部主要是接地平面和引出脚底座;电路的大部分位于层和第二层。第二层上的PTF埋入式电阻经由微通路(microvias)与层相连,实现了高效的电路板设计,且有可能引入寄生或干扰的轨迹非常少。细微的线和间隔为4mil。微通路和底座分别为5和10mil。

嵌入式电阻 在大多数设计里,通常首先检查嵌入电阻的可能性,因为电阻是数量多的无源元件,且在解放电路板面积资源方面潜力。空出来的表面积则可以用来嵌入那些原本无法装进的较大电容器或电感,或者用于压缩模块的占用面积。

分析RF模块电原理图可得出一个结论:全部8个电阻可允许20%的波动,所以应被嵌入。模块中第二层上的PTF电阻的布局。采用每方50 印剂来印刷22 ,51 和220 电阻。采用每方1000 印剂印刷1.5 K 、1.8 K 和2.2K 电阻。这些电阻宽400~750 m,长280~850 m。采用两种不同的印剂可把设计压缩到希望的面积内。另外,电阻直接与HD平板电容器的底部电极(第二层)相连,这样限度地减少了电损耗和占用空间。

根据经验,只要每印刷的底板电阻密度超过8K~10K,因采用两种或更多印剂印刷而增加的费用便不成为问题。影响基底成本的因素有许多种,但重要的一个因素是底板的利用率。每个底板上的电阻密度越大,基底的成本越低,模块的成本也越低。

在这个RF模块例子中,必须采用两种印剂来嵌入所有的电阻以实现希望的占用面积,消除了对昂贵的双封装晶体管或0201元件的需求,并且节省空间以嵌入昂贵的电感。

电容器 在可能嵌入的11个电容器中只嵌入了3个。有5个电容器的数值不在采用HDI电介质制造的范围之内。剩下的6个低值电容器(<12pF=中,其中3个要么对电路功能影响极大,要么是电路微调所必需的,因而不能被嵌入。剩下3个电容器象平板电容器一样被嵌入,电极位于层和第二层。如何选择用于嵌入的非关键电容器是通过一个实验来确认的。在实验中,嵌入电容器的尺寸(以及数值)变化范围为 24%,对组装模块的产量无影响。

电容器的尺寸得根据0.8pF/mm2(50 m电介质厚度)的电容密度来计算。超过1pF的电容器所占面积比0402表面安装电容器通常需要的要大。在多层HDI结构和采用CFP的结构中,可把电容器埋入,这样就不会与SMT元件争抢上面的面积资源。在单层HDI结构中,顶部电极位于外层。尽管如此,本设计中还是采用了为2.2 pF的嵌入式电容器,这是因为:1=它们基本上是"无成本"的,节约了被替换的等效SMT元件的元件和组装成本;2=若非如此,EP模块占用面积必须与现有LTC模块相匹配的要求将产生未用空间;3=因把顶端电极加倍作为一个或多个SMT元件的焊接区,增大了嵌入式电容器的空间利用系数。

电感 将小于4nH的嵌入式电感设计为单层铜线(传输线),宽度通常为6~8mil。较大数值的电感(为10n

H)被设计为两层线圈式(螺旋状)。电感的几何形状是模型化的,并被输入Mentor Graphic元件库以为目前和今后的设计所用。即使是低值螺旋电感占用的面积也比大多数0402元件大。但是,我们仍建议嵌入尽可能多的电感,因为这样做也无需额外的成本,并且不占用上方的表面积。

成本 本例研究中的EP-RF模块所用的元件比采用等效共烧陶瓷元件时少13个。这使得元件成本节约了10%以上。用HDI-EP代替共烧陶瓷元件节约了30%的基底成本。组装成本的节约更为显著,超过了40%。这主要是因为组装过程中处理陶瓷基底非常困难。HDI-EP元件在标准尺寸的PCB底板上生产并被大批量排列整齐地发运,从而便于高效快速地进行组装。

结论 本文描述的EP技术使得大量的无源元件能够容易而可靠地嵌入有机HDI基底中。它与所有HDI加高工艺兼容,并可以从三家性的PCB供应商处购置。该说明了HDI-EP模块是该技术的一个极好的应用,并可实现成本的显著节约。

:

热门文章

更多

热门文章

更多