存储器芯片是在特定条件下用来存储数字信息的芯片。存储的信息可以是操作代码,数据文件或者是二者的结合等。根据特性的不同,存储器可以分为以下几类,如表1所示:

存储器术语的定义

在讨论存储器芯片测试之前,有必要先定义一些相关的术语。

写入恢复时间(Write Recovery Time):一个存储单元在写入操作之后和正确读取之前中间必须等待的时间。

保持时间(Hold Time):输入数据电平在锁存时钟之后必须保持的时间间隔。

Pause Test:存储器内容保持时间的测试。

刷新时间(Refresh Time):存储器刷新的最大时间间隔。

建立时间(Setup Time):输入数据电平在锁存时钟之前必须稳定保持的时间间隔。

上升和下降时间(Rise and Fall Times):功能速度测试是通过重复地进行功能测试,同时改变芯片测试的周期或频率来完成的。测试的周期通常使用二进制搜索的办法来进行改变。这些测试能够测出芯片的最快运行速度。

写入恢复(Write Recovery):一个存储单元在写入操作之后和下一个存储单元能正确读取之前中间必须等待的时间。

读取时间(Access time):通常是指在读使能,片选信号或地址改变到输出端输出新数据的所需的最小时间。读取时间取决于存储器读取时的流程。

存储器芯片测试中的功能测试

存储器芯片必须经过许多必要的测试以保证其功能正确。这些测试主要用来确保芯片不包含一下类型的错误:

存储单元短路:存储单元与电源或者地段路

存储单元开路:存储单元在写入时状态不能改变相邻单元短路:根据不同的短路状态,相邻的单元会被写入相同或相反的数据地址

开路或短路:这种错误引起一个存储单元对应多个地址或者多个地址对应一个存储单元。这种错误不容易被检测,因为我们一次只能检查输入地址所对应的输出响应,很难确定是哪一个物理地址被真正读取。

存储单元干扰:它是指在写入或者读取一个存储单元的时候可能会引起它周围或者相邻的存储单元状态的改变,也就是状态被干扰了。

存储器芯片测试时用于错误检测的测试向量

测试向量是施加给存储器芯片的一系列的功能,即不同的读和写等的功能组合。它主要用于测试芯片的功能错误。常用的存储器测试向量如下所示,分别介绍一下他们的执行方式以及测试目的.

全”0”和全”1”向量: 4n行向量执行方式:对所有单元写”1”再读取验证所有单元。对所有单元写”0”再读取验证所有单元。

目的:检查存储单元短路或者开路错误。也能检查相邻单元短路的问题。

棋盘格(Checkerboard)向量:4n行向量

执行方式:先运行0-1棋盘格向量,也就是第一个单元写1,第二个单元写0,第三个单元再写1,依此类推,直到最后一个单元,接下来再读取并验证所有单元。再运行一个1-0棋盘格向量,就是对所有单元写入跟0-1棋盘格完全相反的数据,再读取并验证所有单元。

目的:这是功能测试,地址解码和单元干扰的一个最基本最简单的测试向量。它还能检查连续地址错误或者干扰错误,也通常用它作为时间测量时的向量。

Patterns Marching向量:5n行向量

执行方式:先对所有单元写0.读取第一个单元,再对第一个单元写1。再读取第二个单元,再对第二个单元写1,依此类推,直到最后一个单元。最后再重复上述操作,只是写入数据相反。

目的:这是功能测试,地址解码和单元干扰的一个最基本最简单的测试向量。它还能检查连续地址错误或者干扰错误,也通常用它作为时间测量时的向量。

Walking向量:2n^2 行向量

执行方式:先对所有单元写0,再读取所有单元。接下来对第一个单元写1,读取所有单元,读完之后把第一个单元写回0。再对第二个单元写1,读取所有单元,读完之后把第二个单元写回0。依次类推,重复到最后一个单元。等上述操作完成之后,再重复上述操作,只不过写入的数据相反。

目的:检查所有的地址解码错误。它的缺点是它的运行时间太长。假设读写周期为500ns,对一个4K的RAM进行wakling向量测试就需要16秒的测试时间。如果知道存储器的结构,我们可以只进行行或者列的walking以减少测试时间。

Galloping写入恢复向量:12^2n行向量

执行方式:对所有单元写0。再对第一个单元写1(基本单元),读取第二个单元, 然后返回来读取第一个单元。再对第二个单元写0,读第二个单元。接下来再在其它所有单元和基本单元之间重复这个操作。等第一个单元作为基本单元的操作完成之后,再把第二个单元作为基本单元,再作同样的操作。依此类推,直到所有单元都被当过基本单元。最后,再重复上述过程,但写入数据相反。

目的:这是功能测试,地址解码测试和干扰测试一个极好的向量。如果选择适当的时序,它还可以很好地用于写入恢复测试。同时它也能很好地用于读取时间测试。

其他的测试向量都类似于以上这些向量,都基于相同的核心理念。

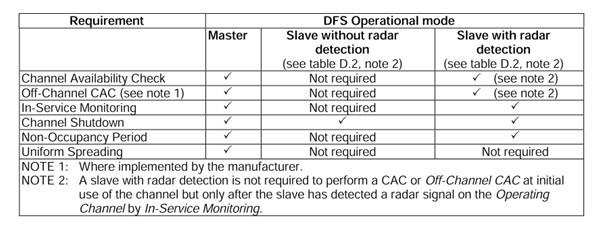

动态随机读取存储器(DRAM)

动态随机读取存储器( DRAM)的测试有以下的一些特殊要求:

1.行地址和列地址在相同的地址线上输入(行列地址复用)。他们分别通过RAS和CAS信号来锁存。

2.需要在固定的时间间隔内对芯片进行刷新。

3.DRAM能够进行页操作。因此需要保持行地址不变而改变列地址(或者相反)。

逻辑测试介绍

逻辑芯片功能测试用于保证被测器件能够正确完成其预期的功能。为了达到这个目的,必须先创建测试向量或者真值表,才能进检测代测器件的错误。一个真值表检测错误的能力有一个统一的标准,被称作故障覆盖率。测试向量与测试时序结合在一起组成了逻辑功能测试的核心。

APP下载

APP下载 登录

登录

热门文章

热门文章