高速或GSPS ADC(每秒千兆采样ADC)相对稀疏出现的转换错误不仅造成其难以检测,而且还使测量过程非常耗时。该持续时间通常超出毫秒范围,达到几小时、几天、几周甚至是几个月。为了帮助消减这一耗时测试负担,可以在一定“置信度”的确定性情况下估算误差率,而仍然保持结果的质量。

误码率(BER)与转换误差率

与串行或并行数字数据传输中BER的数字等效值类似,CER是转换错误数与样本总数之比。但是,BER和CER之间有一些截然不同之处。数字数据流中的BER测试采用长伪随机序列,该序列可于发送器中在传输两端使用常用种子值来启动。接收器预期将收到理想的传输。通过观察接收数据与理想数据的差异,便可精确计算出BER。两端之间伪随机序列数据中的失配(基于种子值)即视为误码。

与CER不同,误差测定不像纯数字比较那么简单。由于ADC转换过程中始终具有小的非线性,另外还存在系统噪声和抖动,因此并非总是能确定预期数据和实际数据之间的确切差异。相反,需要建立误差阈值,用于确定转换错误和具有容许预期噪声的样本之间的界限。这与数字BER不同,并不会对发送和接收的预期数据进行确切比较。相反,首先必须量化样本的误差幅度,然后再确定是转换错误,还是在转换器和系统的预期非线性范围内。ADC后端数字接口的误码率必须低于转换器的内核CER,因此无法忽视。如果并非如此,那么数据输出传输误差将覆盖CER并成为主要误差来源。

亚稳态

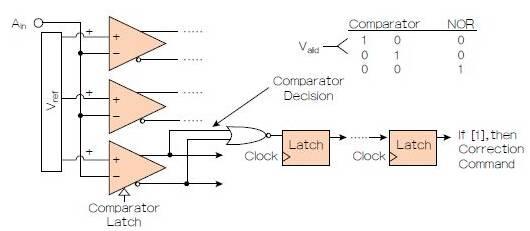

高速ADC中造成转换错误的一个常见原因是一种称为亚稳态的现象。高速ADC在将模拟信号转换为数字值的转换过程中,往往会在不同阶段使用多个梯级比较器。如果比较器无法确定模拟输入是高于还是低于其参考点时,就会产生可能导致出现错误代码的亚稳态结果。当两个比较器的输入之差幅度非常小或为零时,就可能发生这种情况,此时无法进行正确比较。由于此错误值会沿着流水线传播,因此ADC可能产生重大的转换错误。

当差分模拟输入为相对较大的正值或负值时,比较器可以快速计算出差值并给出明确决定。当差分值很小或为零时,比较器做出决定所需的持续时间会长很多。如果在此决定点之前比较器输出锁存,则将产生亚稳态结果。

有些设计方案可以减轻这个问题。首先,将比较器的不确定范围设计的非常小,迫使比较器在可能的最大模拟输入条件范围内做出准确决定。但是,这可能造成电路功率和设计尺寸增加。

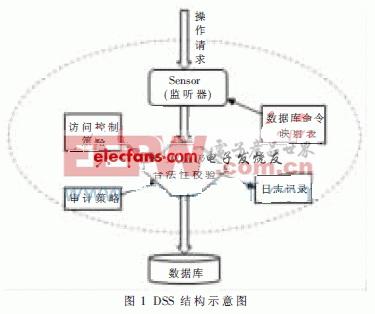

第二种方法是尽量延迟比较器采样时间,给模拟输入最长的时间建立至已知的比较器输出值。但这种方法存在多个限制,因为延迟最长也只能持续到当前采样时间结束,而后比较器必须继续处理下一次采样。第三种方法是采用智能错误检测和校正算法,该算法会对比较器在高速ADC转换过程后续阶段中引入的不确定性进行数字补偿。当比较器未能在最大允许时间内做出决定时,逻辑可检测到该缺失。然后,此信息可被附加到相关样本上,以便未来进行内部调整。识别出此警报时,可使用后处理步骤在样本从转换器输出前纠正该错误。这可以从图1中的AD9625看出,它是ADI公司的一款12位、2.5GSPS ADC。

图1:可在AD9625的模数转换过程内识别比较器的不确定性。在后续步骤中执行校正命令以校正样本,然后再从转换器输出。

置信度

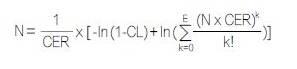

CER置信度(CL)是指在不精确到特定故障率的情况下对未来错误的外推预期。这可减少针对给定CER获取的样本总数,但代价是不能保证100%的确定性。从数学角度来说,要达到绝对100%的确定性,需要取得无限持续时间内的样本。因此,根据行业经验,95%的置信度已经相当接近已知值,并且实现了不确定性和测量时间之间的平衡。如果将测试重复一百次,则有95次可以准确识别误码率。有时工程师会误认为一旦在测试期间检测到误差,该过程就会结束并找到最终的CER。这既不准确也不完整。无论过程中是否有误差,转换误差率及相关的置信度都可以测试。但是,如果在给定置信度下检测到误差,则与没有错误时的样本数相比,必须增加测量的样本数量。

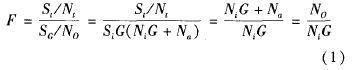

以上公式给出了置信度、误码率和样本数之间的自然对数数学关系表达式。式中:N为测量的样本数;CER为转换误码率;CL为置信度;E为检测到的错误数。

未检测到误差时,公式有所简化,右边的项等于零,结果仅取决于左边的项。当CL为95%且未检测到误差时,所需的样本数仅约为预期CER的倒数乘以3。测量到100%置信度,即对于任何CER值都有CL=1.0,从数学角度上需要获取-ln(0)无穷大的无限样本数(N)。误差阈值

高速ADC中的转换误差幅度很关键,有些误差比其他误差更重要。例如,一个或两个最低有效位(LSB)误差可能在系统的预期噪底之内,甚至可能不会影响瞬时性能。但是,最高有效位(MSB)误差,乃至满量程误差可能造成系统故障事件。因此,CER测试需要具有一种机制或阈值来确定转换中误差的严重程度。

转换的误差阈值应该包括ADC的已知线性不足,以及时钟抖动和其他超出转换器功能的系统噪声。对于任何给定样本,这些通常会累加为14位ADC的4或5个最低有效位(LSB)或16~32个代码。根据ADC分辨率、系统性能和应用的误码率要求,该值的大小可能略有不同。使用此误差带与理想值进行比较后,超出此限值的样本将被视为转换错误。在传统视频ADC中,此错误被称为“闪码”,因为它会在视频屏幕上产生亮白色像素闪烁。可接受的转换器误码率很大程度上取决于信号处理系统和系统误差容差要求。

历史上测量的GSPS ADC转换误差率一般不会低于1e-14。1e-15的误差率意味着转换器在1e15个样本范围内不应出现转换错误。虽然这些数字看起来很大,但凭借当今先进转换器技术的高采样速率,对于CER测试仍然可以实现。但是,对于具有8ns采样速率的125MSPS转换器,1e15次采样将占用800,000s(1e15*8ns),也即9.24天。要在这些误码率中实现95%的CL,则需要分别将这些采样持续时间的均乘以2.996。

CER测试

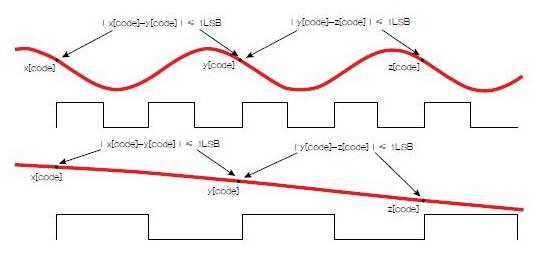

图2给出了如何测试内部A D C 内核的CER。在或接近ADC最大编码速率下采样时,可使用频率相对较慢的正弦波作为模拟输入。应对模拟输入信号进行规划,以便在忽视系统噪声的情况下,两个相邻样本之间的预期绝对差不大于1LSB代码。理想情况下,模拟输入信号比满量程稍大,以便运用ADC的所有代码。应计算模拟输入和编码采样速率,以便建立较长的一致性周期,而ADC不在同一代码级别进行一致采样。

图2:CER测试的两种采样情形。顶部的情形是以比Fs/2稍快的速率对模拟信号进行采样,其中仅每隔一个样本比较一次。理想情况下,两个连续样本的不同之处不超过一个LSB代码。下面的情形是对相对较慢的模拟输入进行过采样,以便两个相邻样本的不同之处也不超过一个LSB代码。

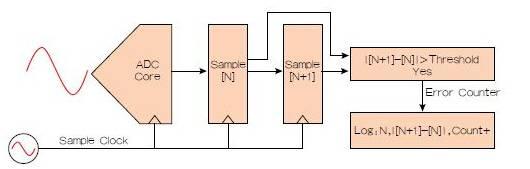

图3:CER测试比较两个连续ADC样本和预定误差阈值。计数器记录错误发生次数、幅值和采样位置标识符。

系统使用一个计数器来跟踪两个相邻样本之间的幅度差值超过阈值限值的情况,并将这种情况计数为转换错误。该计数器必须保留整个测试过程中错误的累加总数。为了保证系统按预期工作,还应记录误差幅度与理想情况之间的关系。测试需要的时间将基于采样速率、所需的测试CER和所需的置信度(图3)。

小结

典型转换器架构可实现一些系统可接受的测量转换误码率,新的设计和错误检测算法正推动限值实现更佳的性能。ADI的12位2.5GSPS ADC AD9625分级比较型流水线内核使用专有技术检测流水线处理前期的ADC转换错误,然后处理和纠正后期的错误。这在12位GSPS ADC上实现了优于1e-15、置信度为95%的行业一流测量CER。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多