摘要

本文首先主要介绍了TI 的新一代时钟产品LMK0480X 的holdover 功能和指标,以及在新一代的无线C-RAN 网络中的应用。通过对LMK0480X holdover 的指标分析,证明LMK04808 完全满足通信网络的时钟倒换的需求。

1、Holdover 功能的引入

在目前的通信系统当中,无论是有线还是无线,都是一个时钟同步系统。参考时钟从宿源端通过网络传递给系统中的各个设备;为了提高系统中各个设备的稳定性,同时为了提高系统中设备对于不同应用的灵活性,一般都有超过一路的参考时钟输入到设备中。当设备中的时钟单元在这些输入的参考时钟中切换时,要使时钟单元的输出要保持性能和时钟的稳定性,这就要求时钟电路具备holdover 功能,支持参考时钟hitless 切换。

以往的模拟时钟电路中所谓的holdover 功能,只是当发生时钟切换时,鉴相器的电荷泵被强制输出到VCC/2;但某些情况下,时钟锁定时的电荷泵电压和VCC/2 差别比较大,这样在时钟切换的过程中,输出时钟的跳变可能会超出系统所能允许的范围,造成系统的时序紊乱。

在TI 最新的时钟去抖芯片LMK048XX 系列中,增加了电荷泵电压跟踪电路;这个电路实时采样电荷本电压并且保存更新到芯片的集成DAC 上;当芯片在输入时钟切换的过程中,电荷泵电压输出切换到DAC 的输出上,这样在参考时钟切换前后,压控电压变化非常微小,保证了系统时钟的稳定性。

LMK0480XX 系列时钟器件的Holdover 功能是真正的hitless switch,下面的章节将详细介绍holdover 的整个过程及相关的指标。

2、LMK0480x 系列产品holdover 功能介绍

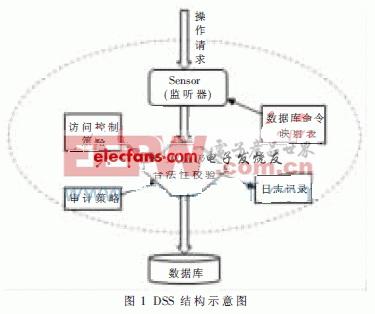

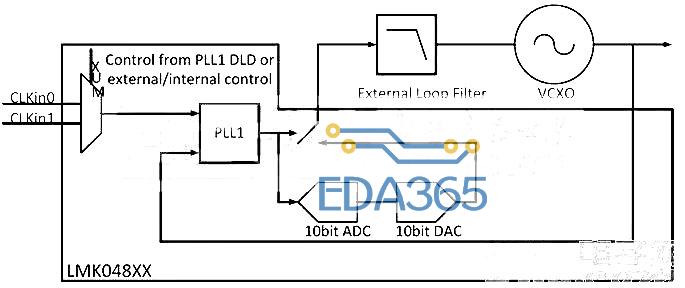

LMK048xx 系列是TI 推出的新一代时钟去抖芯片,采用了两级锁相环级联的架构。第一级锁相环,利用窄带环路滤波器和外部VCXO,主要完成对输入参考时钟去抖;第二级环路滤波器主要利用高性能的内部锁相环生成系统需要的各种时钟。上文提到的Holdover 功能是第一级锁相环具备的功能。

xa0

Figure 1 LMK0480X holdover 架构

xa0

上图是LMK048XX holdover 的功能框图。其中,CLKin0 和CLKin1 分别是来自网络的两个参考时钟,选择一路作为时钟芯片以及系统的主时钟。当网络设备发生主从倒换或者业务切换时,时钟芯片的参考时钟也随之切换。触发参考时钟切换的条件可以为a. PLL1 的DLD 状态,b.外部管脚的硬件控制,c. 内部寄存器控制。下面的讨论我们假定切换是以PLL1 的DLD 状态触发的。

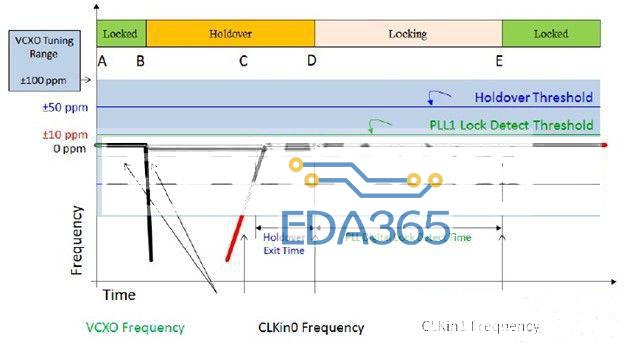

当LMK048XX holdover 功能使能时,一个完整的参考切换过程如下图所示,主要分为如下几个步骤:

xa0

Figure 2 LMK0480X holdover 流程

xa0

Step1: PLL1 正常锁定在CLKin0, PLL1 DLD 为高;LMK048XX 集成的counter ADC 跟踪VCXO 的压控电压并更新集成的counter DAC, 更新的速率为PDF/DAC_CLK_DIV,每个更新周期内上升或下降一个LSB。

Step2:当CLKin0 由于某些原因丢失或出现比较大的频率误差时,PLL1 的鉴相误差超过锁定窗口(PLL1_WND_SIZE),DLD 为低;DLD 为低时,ADC 停止跟踪压控电压及更新DAC,DAC 的输出保持在最后锁定时的压控电压;DLD 拉低同时触发LMK048XX 进入holdover 状态,内部开关切换VCXO 的压控电压到DAC 输出。

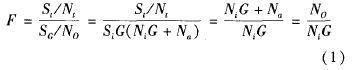

在这个过程中,由于ADC/DAC 的DNL 误差(+/-2LSB),导致输出频率与锁定频率之间产生了频率误差,可以根据以下公式得到频率误差或频率准确度:

Equation 1

一般情况下,holdover 的频率误差可以控制在0.5ppm。进入holdover 功能以后,VCXO 的频率稳定度主要取决于VCXO 以及LMK048XX 自身的温度特性。

Step3: 当芯片检测到CLKin1 的有效参考输入后,LMK048XX 不会立即退出holdover;VCXO 的输出首先会与CLKin1 的参考输入进行鉴相,只有连续HOLDOVER_DLD_CNT 个鉴相周期频率误差小于PLL1_WND_SIZE,LMK0480XX 将会退出holdover。按照最差情况下,如果要满足退出条件,CLKin1 和VCO 的频率误差应该满足:

Equation 2

退出holdover 所用的时间与CLKin1 和VCXO 的初始相位有关,考虑最差的情况,退出holdover 所用的时间为:

Equation 3

Step 4: 当LMK048XX 退出holdover 以后,VCXO 的Vtune 电压切回到PLL1 charge pump 输出,同时CLKin1 和VCXO 开始锁相。由于在退出holdover 的过程中,VCXO 和CLKin1 的相位已经相当接近(PLL1_WND_SIZE),所以在重新锁定的过程中,VCXO 和CLKin1 的相位误差迅速减小,满足小于PLL1_WND_SIZE。一般情况下,这个时间不会大于20ms。

在LMK048XX 中,为了使芯片稳定锁定,VCXO 和CLKin1 的误差必须连续PLL1_DLD_CNT 个鉴相周期小于PLL1_WND_SIZE,DLD 才会置高上报芯片重新锁定。重新锁定的时间:

Equation 4

Step 5:当芯片再次锁定,DLD 重新置高,触发集成的ADC 重新跟踪VCXO 的压控电压,并开始更新DAC 输出。

由于DAC 是coutner 型DAC,更新的速率为每个工作周期增加或降低一个1LSB。当考虑最差情况下,DAC 更新到VCC/2 的时间为:

Equation 5

LMK048XX 要求PFD/DAC_CLK_DIV 100KHz,以保证DAC 的更新速度。

至此,LMK048XX 已经完成了输入参考时钟的整个平滑切换,进入了重新锁定的状态。

3、Holdover 功能的参数设置

3.1 Holdover 功能的配置

使用holdover 功能,必须首先Holdover_Mode = Enable;在绝大多数的应用场景,内部的DAC 输出需要跟踪 VCXO Vtune 电压,所以EN_Track = 1; 并且跟踪电路的正常工作需要在PLL1 锁定之前设置EN_Track =1;否则,当PLL1 锁定之后,设置EN_Track=1 并不能使DAC 输出跟踪Vtune 电压。

APP下载

APP下载 登录

登录

热门文章

热门文章