在系统设备不断向小型化、集成化、网络化发展的今天,嵌入式开发成为新技术发展的最前沿,改变着系统的整体结构。FPGA由于其自身特点,成为嵌入式开发的最佳平台。Altera公司结合其最新一代高端器件推出了全新的嵌入式开发系统,能够实现软核niosII 32位处理器为核心的嵌入式开发系统。

在CvcloneII中,A1tera集成了完整的千兆以太网硬核,硬核包括MAC模块以及可选择的物理层PCS模块和PMA模块,其中MAC模块支持l0/100/1000 Mb/s。Altera的SOPCBuilder工具提供快速搭建SOPC系统的能力,这种架构可以包含一个或多个CPU,提供存储器接口,外围设备和系统互连逻辑的复杂系统。

2 千兆以太网技术简介

以太网技术是当今应用广泛的网络技术,千兆以太网技术继承了以往以太网技术的许多优点,同时又具有诸多新特性,例如传输介质包括光纤和铜缆,使用8B/10B的编解码方案,采用载波扩展和分组突发技术等。正是因为具有良好的继承性和许多优秀的新特性,千兆以太网已经成为目前局域网的主流解决方案。

千兆以太网利用原以太网标准所规定的全部技术规范,其中包括CSMA/CD协议、以太网帧、全双工、流量控制以及IEEE 802.3标准中所定义的管理对象。千兆以太网的关键技术是千兆以太网的MAC层和以太网接口的实现。随着多媒体应用的普及,干兆以太网必然得到广泛应用。

3 Altera的千兆以太网解决方案

3.1 IP核的支持

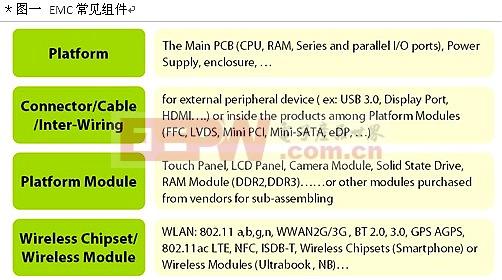

Altera提供了可参数化的千兆以太网megacore解决方案。该方案可在Altera的Arria GX,CycloneII,CycloneIII系列FPGA上工作,可配置使其包含MAC,PCS,PMA模块中的一种或多种,配置选择及相应的接口标准。

千兆以太网IP核的功能描述如下:

(1)支持IEEE 802.3标准。

(2)10/100/1 000 Mb,s以太网媒体访问控制支持半双工和全双工工作模式。

(3)多通道MAC,支持最多24端口。

(4)以太网物理层编码子层1000BASE一X/SGMII标准的自协商。

(5)接口使用方便。

对于千兆以太网控制器的实现,采用表第l行的配置。吉比特级以太网媒体控制器核(GEMAC)是针对1 Gb/s以太网媒体访问控制器功能的可参数化的megacore解决方案。

3.2 基于FPGA的千兆以太网MAC控制器实现方案

3.2.1 整体设计方案

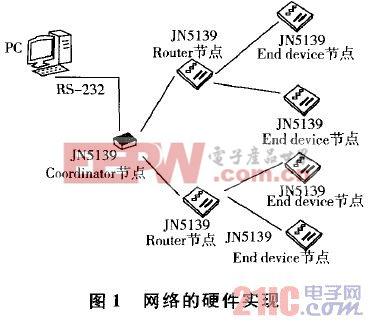

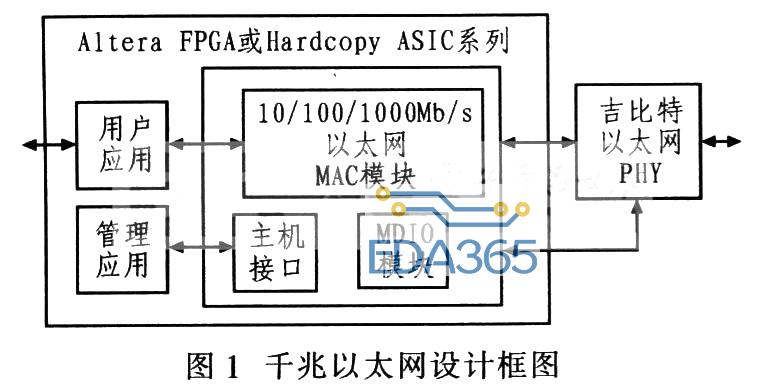

以太网控制器的FPGA设计工作包括以太网MAC子层的FPGA设计,MAC子层与上层协议的接口设计以及MAC与物理层(PHY)的GMII接口设计。该以太网控制器的总体结构设计框图如图1所示,整个系统分为MAC模块,主机接口模块和管理数据输入输出模块。其中,MAC模块主要执行在全双工模式下的流量控制,MAC帧实现发送和接收功能,其主要操作有MAC帧的封装与解包以及错误检测,直接提供了到外部物理层器件的并行数据接口,物理层处理直接利用商用千兆PHY器件,主要开发集中在MAC控制器的研究。

管理数据输入输出模块提供了标准的IEEE802.3介质独立接口,可用于连接以太网的链路层和物理层。主机接口则提供以太网控制器与上层协议(如TCP/IP协议)之间的接口,用于数据的发送、接收以及对控制器内各种寄存器的设置。

APP下载

APP下载 登录

登录

热门文章

热门文章