随着模数转换器(ADC)的设计与架构继续采用尺寸更小的过程节点,一种新的千兆赫ADC产品应运而生。能以千兆赫速率或更高速率进行直接RF采样且不产生交织伪像的ADC为通信系统、仪器仪表和雷达应用的直接RF数字化带来了全新的系统解决方案。

最先进的宽带ADC技术可以实现直接RF采样。就在不久前,唯一可运行在GSPS (Gsample/s)下的单芯片ADC架构是分辨率为6位或8位的Flash转换器。这些器件能耗极高,且通常无法提供超过7位的有效位数(ENOB),这是由于Flash架构的几何尺寸与功耗限制需要取舍。

因此,对超过1 GHz的较高动态范围模拟输入信号进行采样的唯一方法,就是利用一个采样时钟来交错连接多个高速ADC内核,此采样时钟针对每个内核都有精确的交错相(或占空比)。模拟输入需分割并多路复用至每一个ADC,这便为新信号噪声进入信号链及降低输入功率创造了机会。虽然此方法能为某些应用提供充分结果,但设计较复杂,并且在需要数字滤波的输出频域内会产生糟糕的干扰交错伪像。

1 快速还是半速?

在快速傅里叶变换(FFT)的频率响应中看到交错“杂散”,其中每个内部交错式ADC内核的输入失调、增益、带宽和样本时序并非严格匹配。这便为系统设计人员增添了规划复杂性,使其难以预先确定频率内的交错伪像,进而在数字后处理中避免或移除。

由于每一个ADC内核都是分立的,因此在量产系统的寿命期间,这些性能参数极有可能产生较大的制造失配差异。这些失配会造成输入信号的周期性不平衡,并且交错式ADC的输出端会出现杂散频率。

现在,专有ADC技术可通过先进架构与算法防止双通道和四通道交错式ADC内出现上述问题。使用两个半速交错式ADC会增加伪像,现在采用单个全速ADC可在无交错杂散的条件下实现同样的性能。工厂调整算法和片内校准可确保每一个ADC工作在预期的高性能标准下,避免受多个分立交错式内核的失配差异影响。

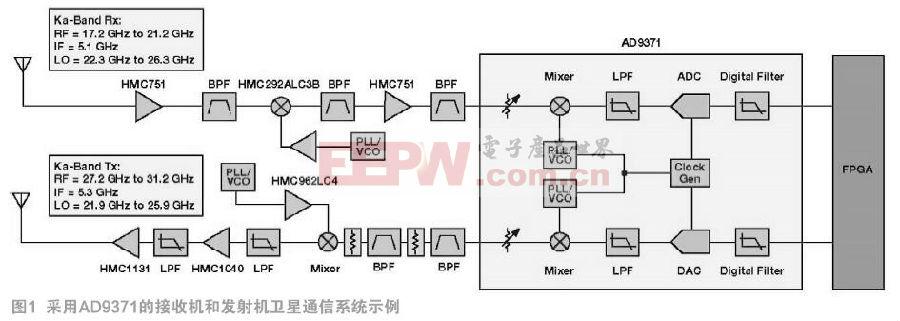

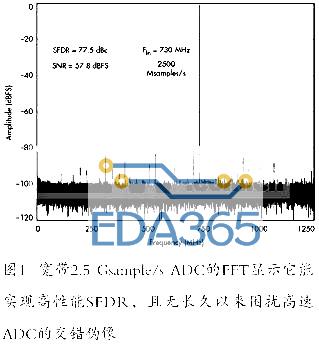

在通常频谱纯净的FFT中观察到杂散频率时,会减小其他噪声相关的载波信号的可用无杂散动态范围(SFDR)。为了改善GSPS ADC的SFDR,除了使用交织式内核,现在又发展出新架构和算法。这样,系统设计人员不必再使用专用ADC后处理例程来鉴别并移除干扰交错杂散(图1)。

2 简化路由

10/12/14位分辨率的多个千兆采样转换器可在短时间内产生大量输出数据。使用低压差分摆幅(LVDS)数据可能需要2.5 Gsample/s、12位ADC的30条1 Gbps并行通道。就系统布局来说,针对每个ADC处理30个差分LVDS对可能会对路由和保持匹配长度提出挑战。使用JESD204B,则仅采用6条或8条差分通道即可发送同等数据。

APP下载

APP下载 登录

登录

热门文章

热门文章