摘要:针对RS-485总线多个节点之间无法自由通信的问题,介绍一种多主机通信方法,以探讨总线接口电路和组网方式,并通过设计通信协议和规划通信过程,完成相关程序设计。此方法在某装备模拟项目中得到应用,取得了预期的效果。

引言

RS-485接口以其结构简单、通信速率高、传输距离远、成本低廉等优点在现场总线中得到广泛应用。传统的RS-485总线要求在同一时刻只能有一个节点进行数据发送,为此多采用一主多从方式或分时复用方式。一主多从方式,即网络中有一个主节点和若干个从节点,由主节点轮询各个从节点以实现数据通信。分时复用方式,即总线控制权分时交由各个节点使用,各节点按照预先分配的时间段发起通信。遇到节点主动发送实时要求高,节点数目不确定,且各个节点通信负荷不均衡等通信系统时,上述两种通信模式的总线利用率和实时性都相对较低。在模拟器材通信中,经常会遇到各节点不定期、多批次主动发起通信的情况,在应用RS-485网络时显得较为不便。为此,需要研究一种基于RS-485总线的多主机通信方法,并在模拟训练中得到应用,以取得良好效果。

1 接口电路

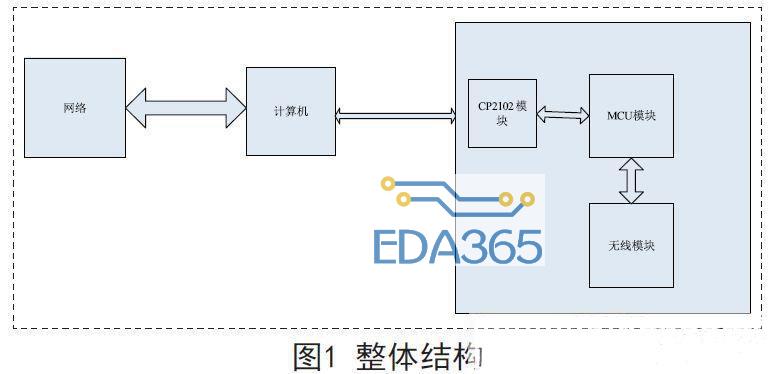

RS-485 接口电路的主要功能是将来自微控制器(MCU)的发送信号TX通过“发送器”转换成通讯网络中的差分信号,将通讯网络中的差分信号通过“接收器”转换成MCU接收的RX信号。任一时刻,RS-485收发器只能够工作在“接收”或“发送”两种模式之一,因此,必须为RS-485 接口电路增加一个收/发逻辑控制电路。另外,RS-485接口电路的附加保护措施也是必须考虑的环节。

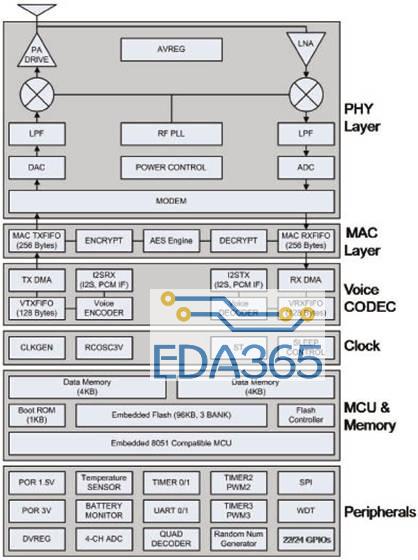

如图1所示为我们设计的RS-485总线接口电路,核心芯片为SP3485,该芯片为+3.3V低功耗半双工收发器,满足RS-485和RS-422串行协议的要求,数据传输速率可高达10Mbps(带负载),与Sipex的SP481、SP483和SP485的管脚互相兼容,同时兼容工业标准规范。SP3485发送器的输出是差分输出,空载时输出电压的大小为0V~+3.3V,即使在差分输出连接了54Ω负载的条件下,发送器仍可保证输出电压大于1.5V。发送器输出最大250mA ISC的限制使SP3485可以承受-7.0V~+12.0V共模范围内的任何短路情况,保护IC不受损坏。SP3485接收器的输入是差分输入,输入灵敏度可低至±200mV。接收器的输入电阻通常为15kΩ(最小为12kΩ)。-7V~+12V的宽共模电压范围允许系统之间存在大的零电位偏差。SP3485接收器还具有故障自动保护(fail-safe)特性,可在输入悬空时使输出保持在高电平状态。

控制该电路工作的MCU采用STM32F103VET6,该芯片为100引脚LQFP封装,采用Cortex-M3内核,处理速度可达72MHz,具有64K RAM和512K Flash,支持CAN、I2C、 SPI、USART、USB等接口。其串行口通过RXD(即485_RX引脚)连接SP3485芯片的RO引脚,通过TXD(即485_TX引脚)连接芯片的DI 引脚。MCU输出的485_DIR信号控制芯片的发送器/接收器使能,亦即控制通信方向。当485_DIR信号为“1”时,发送器工作,接收器失效,此时MCU可向RS-485 总线发送数据;485_DIR信号为“0”时,发送器失效,接收器工作,此时MCU可以接收来自RS-485 总线的数据。

为保证电路工作稳定可靠,电路中B引脚连接上拉电阻R2,A引脚连接下拉电阻R3,这样在上电或不传输数据时能保证RS485总线处于确定状态,为总线提供网络失效保护,以提高RS-485节点与网络的可靠性。

电阻R5为备用设计,如果将SP3485 连接至80C51或STM32F103VET6等MCU芯片的UART串口,则SP3485芯片的RO引脚不需要上拉(R5为0Ω);否则,需考虑将R5更换为约10K 的上拉电阻。

考虑到485总线在组网时,位于网络两端的节点需要增加120Ω终端电阻,我们在485_B和485_A之间放置了终端电阻R4,为便于使用者灵活调整节点在网络中的位置,我们还为终端电阻设计了选择跳线JP1。

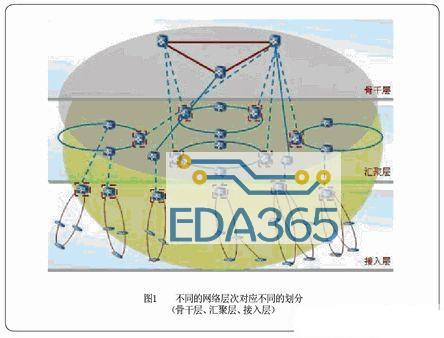

2 组网方式

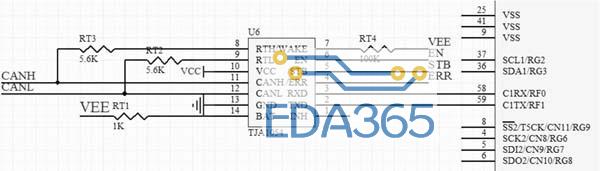

RS-485总线组网方式如图2所示,所有RS-485节点全部挂在一对RS-485总线上。注意RS-485总线不能够开叉、但是可以转弯。RS-485网络采用直线拓朴结构,需要安装2个终端匹配电阻。终端匹配电阻安装在RS-485 传输网络的两个端点,并联连接在A-B 引脚之间,其阻值要求等于传输电缆的特性阻抗(一般取值为120Ω)。终端匹配电阻主要作用是使总线的阻抗连续,以减少信号的反射,从而提高信号的传输质量。在矩距离(300 米以下)、低波特率(19200bps)数据传输时可不需终端匹配电阻。

3 多主机通信协议

稳定可靠的通信不仅依赖硬件环境,对通信协议也有很高的要求。为了解决RS-485总线多主机通信的问题,需要对RS-485通信协议进行研究。

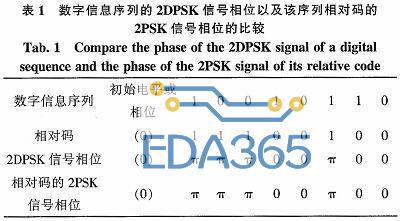

3.1 帧结构

![]()

设定起始符为字符’$’。考虑到便于报文接收,起始符应与设备地址不同。目的节点、源节点均为网内设备节点地址,取值为1~32。帧长度是从起始符到结束符的字符长度,取值为7~255。结束符为字符’@’。

帧校验(FCS)通常可采用奇偶校验、和校验、CRC校验等方法,前两者处理相对简单,节省运算时间,但存在漏检的可能,后者处理相对复杂,需要一定的运算时间,但可靠性优于前面两种方法。在具体应用时,可根据需要自行选择。本文帧校验方法为从目的地址开始,到数据的最后一个字节为止,各字节依次异或,最后得到的数值即为帧校验值,如果接收方发现校验错误则应要求发送方重发。

值得注意的是,对于起始符、结束符与数据帧内容重叠时的处理,采用数据字节前插入0xFF的办法加以识别。例如,要发送的数据为0X24,与结束符重叠,则在报文中应写为0xFF 0x24。

3.2 通信过程

3.2.1 发送方工作流程

RS-485总线采用半双工工作方式,全网在同一时刻只能有一个设备在发送报文(扮演主机),此时其它设备处在接收状态(扮演从机)。基于对可靠性的考虑,采取如图3所示通信流程。

具体解释如下:F_BUSY为总线忙标志,取值为“1”时表示“总线忙”,N为发送报文后对方无应答时报文的重传次数,M为接收到的报文出现FCS错误时的重传次数。当系统初始化时,每个节点的F_BUSY均为0,即总线空闲, N、M均为0。

发送方的工作流程如下:

总线的申请和释放均由通信的发起方完成。

步骤一:申请总线。发送报文前先进行“忙”检测,当F_BUSY为“0”时发送“申请总线”报文,通知全网节点即将占用总线,并开启计时器,无关节点收到该报文后将F_BUSY置为1,并禁止本地发送报文,目的节点收到后发送“确认可用”报文。当F_BUSY为“1”或计时已到却未收到“确认可用”报文,则随机延时后重新申请总线。

步骤二:发送报文。

步骤三:等待应答。发送报文后,启动计时器,等待对方的接收应答,如在规定时间内未收到对方应答,则进行报文重传,并将重传次数N加1。如果重传已达三次,则认为网络断开,释放总线,结束通信。

步骤四:出错重传。如果对方应答帧内容为“FCS错误”报文,则进行报文重传,并把M加1。如果重传已达三次,则认为网络不稳定,释放总线,结束通信。

步骤五:释放总线。报文发送流程结束后,该节点发出“释放总线”报文,各节点将F_BUSY置为0,总线恢复空闲状态。

发送方的处理中,在申请总线阶段没有考虑消息碰撞问题,这主要是基于网络节点数量有限,碰撞几率较低的考虑。为增强报文的可靠性,须进行帧校验处理。在等待应答阶段,采取ARQ技术,对出错报文进行请求重传。为避免程序陷入死循环,针对对方无应答或报文帧校验错误的情况采用了有限次重传的机制。

APP下载

APP下载 登录

登录

热门文章

热门文章