引言

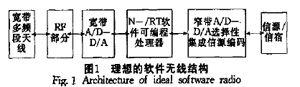

软件无线电 技术的宗旨是构造一个具有开放性、标准化、模块化的通用硬件平台,将无线通信的各种功能,如工作频段、调制解调类型、数据格式、加密抗干扰模式、通信协议等用软件来完成,并使宽带A/D和D/A转换器尽可能靠近天线。理想的软件无线电

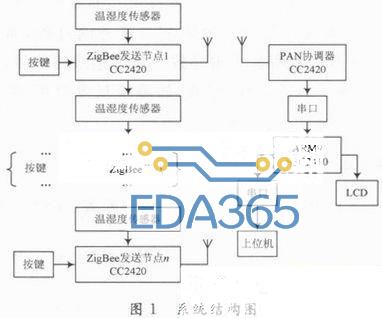

技术的宗旨是构造一个具有开放性、标准化、模块化的通用硬件平台,将无线通信的各种功能,如工作频段、调制解调类型、数据格式、加密抗干扰模式、通信协议等用软件来完成,并使宽带A/D和D/A转换器尽可能靠近天线。理想的软件无线电 结构如图1所示。其中,N-/RT为准时和实时;信源 /信宿包括窄带业务与未来的宽带业务。

结构如图1所示。其中,N-/RT为准时和实时;信源 /信宿包括窄带业务与未来的宽带业务。

xa0

传统的短波电台由于频率资源拥挤,时变电离层信道严重的频率选择性衰落以及多径时延、各种大气噪声以及人为无线电 噪声的影响,只适合于传输模拟话音以及低速率数据。随着现代无线通信理论与软硬件技术的发展以及对电离层信道特性的深入探索,短波电台出现了以下几方面的变化:①采用跳频技术来提高抗干扰能力;②采用自适应通信技术来提高建链能力;③数据通信(包括图文数据及声码话数据等)成为重要的业务方式;④采用数字加密方式等。

噪声的影响,只适合于传输模拟话音以及低速率数据。随着现代无线通信理论与软硬件技术的发展以及对电离层信道特性的深入探索,短波电台出现了以下几方面的变化:①采用跳频技术来提高抗干扰能力;②采用自适应通信技术来提高建链能力;③数据通信(包括图文数据及声码话数据等)成为重要的业务方式;④采用数字加密方式等。

理论上就目前ADC的速度而言能够满足对短波波段信号进行低通采样,但直接在射频端进行A/D转换存在以下问题。①严重影响接收机的选择性和灵敏度,一般射频频段内会存在若干强窄带干扰,为防止超载并降低ADC的量化噪声,ADC必须具有大动态范围,而当信号很弱接近噪声基底时,ADC的无寄生动态范围SFDR指标决定了接收机总的SNR,ADC的实现难度很大;②短波波段带宽较宽,ADC前的宽带抗混叠滤波器与宽带放大器目前性能还不够理想;③ 数字信号处理器对射频段窄带信号进行信道分离解调难度很大;④ADC采样孔径抖动引起的信噪比恶化相对严重。因此,目前对传统短波电台的数字化改造大都保留了电台的射频以及模拟混频环节,而在频率较低并且固定的二中频处进行。

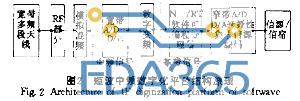

本文中我们设计的短波中频数字化平台是在二中频500kHz处进行数字化,从而省去传统电台的边带滤波等一系列模拟解调环节,构筑一个统一的硬件平台实现单边带、调幅、等幅报音等的软件调制解调,并在此基础上加载跳频、自适应、并行及串行Modem 数传等调制解调模块。短波中频数字化平台结构原理如图2所示。其中,N-RT为准实时和实时;信源/信宿包括窄带业务与未来的宽带业务。

1数字变频技术

xa0

从图2可以看出,从中频采样信号到基带信号是通过数字变频来完成的,数字变频技术是软件无线电 的核心技术之一,涉及到多抽样率数字信号处理 (MRDSP:multiratedigitalsignalprocessing)技术,后者是自20世纪70年代开始发展起来的数字信号处理领域的一门重要技术。数字变频器主要由数字混频器、数控振荡器和低通滤波器3部分组成。数字变频采用正交混频,而且需要对信号进行重采样抽取或者内插滤波(此处的抽取滤波包括2步操作,首先是抗混叠低通滤波,然后是样点的抽取;内插滤波则先是样点的内插,然后是抑制镜频的低通滤波)。因为中频接收信号经过正交混频以后已变为基带信号,此时信号只在中频采样频带(二分之一中频采样率)内占很小一部分,经低通抽取滤波后可以在保持信号不受影响的情况下降低数据速率(降为基带采样率),有助于减轻后端数字信号处理压力;对于发送通道在正交混频之前必须先进行内插滤波以提高信号的数据率,使之至少达到奈奎斯特采样定理要求的两倍信号最高频率,否则会产生严重的混叠。

的核心技术之一,涉及到多抽样率数字信号处理 (MRDSP:multiratedigitalsignalprocessing)技术,后者是自20世纪70年代开始发展起来的数字信号处理领域的一门重要技术。数字变频器主要由数字混频器、数控振荡器和低通滤波器3部分组成。数字变频采用正交混频,而且需要对信号进行重采样抽取或者内插滤波(此处的抽取滤波包括2步操作,首先是抗混叠低通滤波,然后是样点的抽取;内插滤波则先是样点的内插,然后是抑制镜频的低通滤波)。因为中频接收信号经过正交混频以后已变为基带信号,此时信号只在中频采样频带(二分之一中频采样率)内占很小一部分,经低通抽取滤波后可以在保持信号不受影响的情况下降低数据速率(降为基带采样率),有助于减轻后端数字信号处理压力;对于发送通道在正交混频之前必须先进行内插滤波以提高信号的数据率,使之至少达到奈奎斯特采样定理要求的两倍信号最高频率,否则会产生严重的混叠。

在模拟变频中,混频器的非线性和模拟本振的频率稳定度,边带、相位噪声、温度漂移、转换速率等都是人们最关心和难以彻底解决的问题,这些问题在数字变频中是不存在的,频率步进、频率间隔等也具有理想的性能。和模拟变频器相比,数字变频还具有以下优点:①载频与数字滤波器系数具有可编程性;②数字混频不存在非线性失真,因而互调小;③数字滤波频响特性好;④系统造价低等。

目前市场上有大量专为数字变频而设计的专用可编程数字信号处理器,如Intersil公司的 HSP50214/215,HSP50415,Graychip公司的GC1012,GC4014以及AD公司的AD9856,AD6620/22/24 等,这些芯片指令集较为简单,速度也较快,并且处理效率更高。本文中我们设计的中频数字化平台即采用了两块专用的数字变频芯片:HSP50415和 AD6620。

HSP50415是Intersil公司单路数字上变频芯片,该芯片具有很强的调制能力,内部主要由内插滤波器、复调制器、定时和载波数控振荡器、双12位150M采样率D/A转换器四部分组成。采样率转换包括3级内插滤波器,内插范围4~128K;支持正交AM及PM调制;提供脉冲成形滤波以及星座图映射等;该芯片最大输出采样率100MSPS,最大输入速率25MSPS,前端具有256级深度的FIFO;32位可编程数控振荡器提供最大 50MHz载波和0.023Hz频率精度。

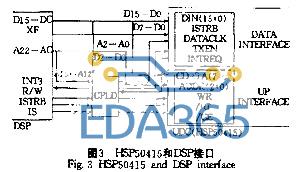

该芯片内部共有16个控制寄存器和4个触发选通寄存器,还有多个可配置RAM块,有2个外部接口,uP NT ER FA CE用于芯片配置以及初始化,DATAINTERFACE用于I,Q正交数据输入。图3给出了一种该芯片和TM S320C54x的参考接口电路。芯片配置时,由于内部控制寄存器大都是32位字长,而uP接口只有8位宽,每个控制字需要连续加载4次才能完成,在此期间,片选线和读写线都必须保持有效状态。数据输入时,根据驱动时钟DATACL K的产生不同,有同步和异步两种方式,前者直接把HSP50415的2×SYMCLK(2倍输入码元时钟)接到DATACL K作为数据输入驱动时钟,此时码元输入输出严格同步,H SP 50415前端的F IFO不起作用,DSP通过控制输入使能TXEN来进行总线隔离;后者DATACL K由DSP通过地址译码产生,当DSP不向H SP50415发送数据时DATACLK为高电平,总线被隔离,DSP可根据FIFO的中断状态来确定是否发送数据,本系统中采用基于中断的异步方式。

xa0

HSP50415的初始化主要包括设定载波频率、输入码元速率、FIFO中断类型、整形滤波器系数、信道增益、工作模式以及输出模式等。其中控制载波频率和输入码元速率的寄存器值是根据下两式计算的,Fsout是输出采样率,等于HSP50415的主时钟,carrierFrequency是载波频率,sym bolRate是码元速率,也是输入采样率。

carrierNCOStep=(carrierFrequency/Fsout)×2^32

symbolNCOStep=(symbolRate/Fsout)×2^32

HSP50415中需要重点设计的是3级内插滤波器,其设计结果直接影响到数字信道性能。第1级滤波器为可编程FIR整形滤波器,主要完成首级内插滤波以及信号整形,该滤波器可以设计成脉冲成形滤波器;第2级滤波器为一系数固定的19阶半带滤波器,提供2倍内插,半带滤波器的特殊结构可以在同样的抽头数下比FIR滤波器减少一半的运算量;第3级滤波器为内插滤波器,其冲激响应类似于级联的积分梳状滤波器,能够提供2~8192倍的内插,而且能够实现分数倍内插,该滤波器配置是芯片自动完成的。

AD6620是AD公司单路数字下变频芯片,该芯片最高输入速率67MSPS;32位复数NCO提供0.02Hz的频率精度和相位与幅度抖动修正;采样率转换包括3级抽取滤波器,分别为2级级联的CIC2滤波器、5级级联的CIC5滤波器以及系数可编程FIR滤波器RCF;数据可以选择16位并口输出或者标准同步串口输出,两个独立的控制和配置端口,可以动态配置AD6620。

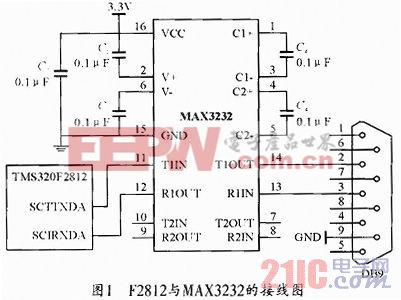

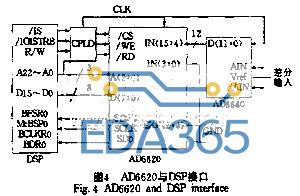

AD6620内部有14个控制寄存器、一个RCF系数RAM块和一个RCF数据RAM块。一般采用uP端口(接DSP外部数据线)进行芯片配置,而用串口输出下变频后的数据,因此接口逻辑相对比较简单。图4给出了一种AD6620与TMS320C54x的参考接口方案。其中AD6620串口输出采用了主机模式,即由AD6620提供串口时钟和帧同步,DSP通过串口中断接收数据。

xa0

本平台中,AD6620前端采用AD6640进行中频采样,该芯片为12位65M采样率高性能A/D转换器,广泛应用于中频宽带高速采样领域,结合过采样技术能够进一步提高采样精度。AD6620和AD6640采用相同的主时钟,这样能在二者之间达到最大的数据吞吐率。

理论分析如何配置3级抽取滤波器的抽取率才能获得最佳信道特性及最小运算量是比较困难的,在级联数与总的抽取率一定的情况下的抽取率分配方案是有限的,因此可通过计算机辅助设计穷举搜索符合要求的各级抽取率,并用Parks-McClellan标准算法来设计最后一级可编程FIR滤波器,该滤波器主要用于末级抽取和信号整形,对信道性能影响很大。另外,AD6620数据文档上还提供了根据抗混叠指标,通过简单的计算公式及查表来快速确定CIC2和 CIC5抽取率的方法。

2短波电台中频数字化平台实现

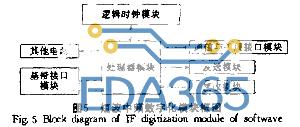

基于上述的专用数字上下变频芯片以及通用数字信号处理器,我们构建了短波中频数字化平台,配合前端的射频模块,该平台还能够用于其他频段(比如超短波)的中频数字化,具有较强的通用性及可扩展性。图5为该平台的硬件模块框图。其中,处理器模块完成信号的基带调制解调;逻辑时钟模块提供系统中的地址译码及控制信号和各种时钟信号;发送模块完成信号的上变频及中频数模转换;接收模块完成中频采样及信号的下变频;基带接口模块完成语音信号的模数、数模转换;通信与扩展接口模块提供数字业务接口及通信功能。此外,还包括AGC电路、电源及看门狗电路等。

xa0

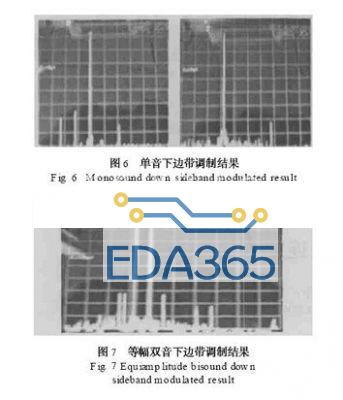

对该平台进行单边带调制性能测试(主要有边带抑制、载波抑制、带外衰减、互调失真等指标),采用高效的复数滤波法进行数字单边带调制[5]。在基带分别加入1kHz,1.7kHz单音和1kHz+1.7kHz等幅双音信号,在500kHz中频处用频谱分析仪观察上边带调制结果如图6和图7所示(横轴中心频率为500kHz,每格1kHz,纵轴每格-10dB)。

xa0

其中,由于HSP50415内部集成的D/A转换器其SFDR指标>50dB,实际测得的三阶互调指标约55dB,在D/A转换器线性指标范围内。如果要求进一步提高互调指标,可以选用双音SFDR指标更高的专用D/A转换器。

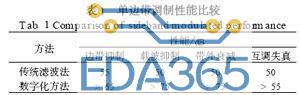

表1给出了该数字化中频与采用晶体滤波器的模拟中频的单边带调制性能比较,可以看出各项指标都有一定提高,并且易于实现。

xa0

该中频数字化平台达到了预定的设计目标,整个平台功耗小于1.5W,主载波调制方式有USB,LSB,AM三种方式,支持等幅报音通信方式,音频响应范围300~3000Hz,并且可编程,中频采样时输入信号可低至毫伏级,可有效降低前端射频模块增益,从而降低模拟前端的非线性影响。在该平台上加载跳频通信,自适应通信以及并行或者串行Modem等业务软件模块,有助于提高电台的保密抗干扰以及数据传输性能。

3结束语

在介绍软件无线电 基本理论以及在短波电台中频数字化应用的基础上,我们结合两款典型芯片对软件无线电中核心的数字变频技术进行了比较详细的讨论,并给出一种短波电台中频数字化平台设计方案,最后采用短波单边带调制对该平台进行了测试,测试结果验证了平台的可实现性。

基本理论以及在短波电台中频数字化应用的基础上,我们结合两款典型芯片对软件无线电中核心的数字变频技术进行了比较详细的讨论,并给出一种短波电台中频数字化平台设计方案,最后采用短波单边带调制对该平台进行了测试,测试结果验证了平台的可实现性。

目前,国内多个科研机构正在开展第三代短波数字化抗干扰自动控制通信电台的研制,该电台基于MIL-STD-188-141B,MIL-STD- 188-110以及GJB2076-94,GJB2077-94标准,融合了高速串行分组数传以及第三代自动链路建立等功能,代表了未来短波通信的发展方向。

APP下载

APP下载 登录

登录

热门文章

热门文章