闩锁效应 (Latch Up) 是在器件的电源引脚和地之间产生低阻抗路径的条件。这种情况将由触发事件(电流注入或过电压)引起,但一旦触发,即使触发条件不再存在,低阻抗路径仍然存在。这种低阻抗路径可能会由于过大的电流水平而导致系统紊流或灾难性损坏。在设计电路应用时,需要确保应用于器件的电压和电流水平符合额定值要求。

在电路设计时, 可以考虑以下建议来防止闩锁问题。

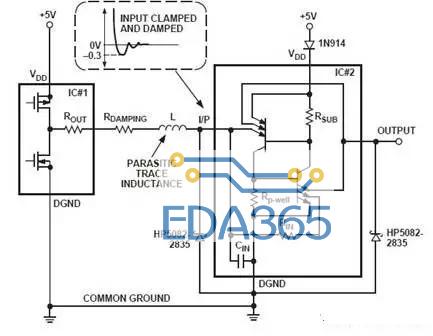

1. 如果由于上电排序而发生闩锁,可以利用二极管与VDD串联。

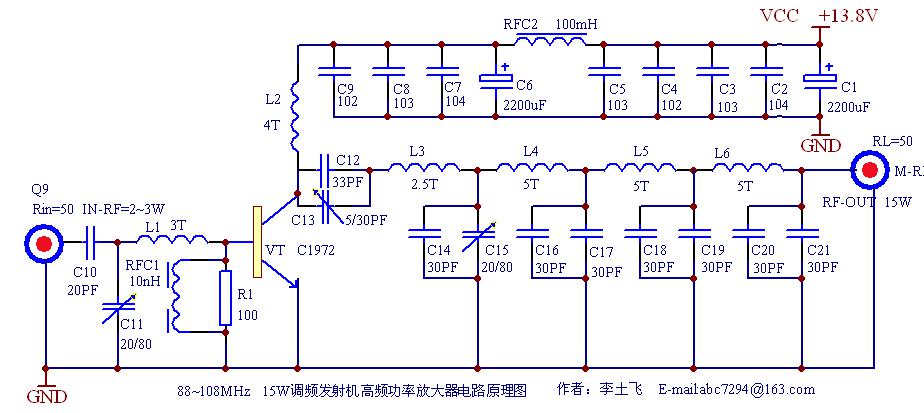

如果任何时候器件的数字输入或输出都超过VDD,可以在VDD串联二极管(如下图使用1N914)来阻止SCR触发和随后的闩锁产生。这是因为二极管能够防止寄生横向PNP晶体管的基极电流从VDD引脚流出,从而防止SCR触发。

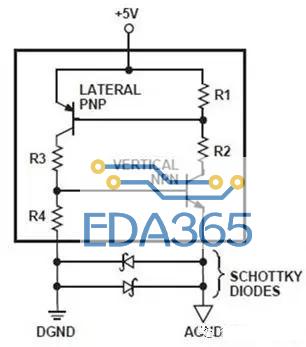

2 将肖特基二极管添加到DGND(数字地)可防止电压不足

如果器件的数字输入和输出随时低于DGND,那么从这些输入或输出连接到DGND的肖特基二极管将有效地将负偏移钳位在-0.3V至-0.4V之间。 这可以防止寄生NPN晶体管的发射极与基极结导通,并且还可以防止SCR触发。

3在DGND和AGND (模拟地) 之间连接肖特基二极管

如果DGND电位偶尔会超过AGND 0.3V或更多,则可以在器件两个引脚之间a放置肖特基二极管来阻止相关寄生NPN晶体管的导通。 这提供了额外的防止闩锁的保护。 此外,前面提到的反向并联连接的额外二极管可以在另一个方向上将DGND限制到AGND,这样就大大减少了数字噪声被注入器件的可能性。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多