VHDL是随着可编辑逻辑器件(PLD)的发展而发展起来的一种硬件描述语言。它是1980年美国国防部VHSIC(超高速集成电路)计划的一部分,并于1986年和1987年分别成为美国国防部和IEEE的工业标准。

作为一种硬件设计时采用的标准语言,VHDL具有极强的描述能力,能支持系统行为级、寄存器传输级和门级三个不同层次的设计,这样设计师将在TOP-DOWN设计的全过程中均可方便地使用同一种语言。而且,VHDL设计是一种“概念驱动式”的高层设计技术,设计人员毋需通过门级原理图描述电路,而是针对目标进行功能描述,由于摆脱了电路细节的束缚,设计人员可以专心于设计方案和构思上,因此设计工作省时省力,加快了设计周期,并且工艺转换变得轻松。VHDL设计技术对可编程专用集成电路(ASIC)的发展起着极为重要的作用。

自从微软提出“维纳斯”计划后,机顶盒便成为信息产业追逐的主要目标,也是信息家电中的主流产品。各国都在加紧对机顶盒的开发,我国也提出了相应的“女娲”计划,全国许多科研单位与生产厂家都在进行这方面的研究。由于我国有线电视资源丰富,市场前景很大,因而对有线电视机顶盒的研究也就格外引人注目。然而,由于我国还未完全开展数字电视业务,因而在机顶盒的调试过程中,要找到合适的信号源是很不容易的,不得不采用通过计算机输出标准视频码流的方式来实现。可大多数计算机EISA总线并行输出的数据速率都难以满足实际工作的需要。虽然EISA总线可以输出16位并行数据,但这对于只能处理8位并行数据的器件来说,仍需要一个转换过程。本文介绍了一种数据格式转换的设计方案。该方案采用VHDL对一块CPLD芯片进行编程,使其实现从16位并行数据到8位并行数据的转换,并将EISA口的数据输出速率提高一倍,达到信源要求。

1 VHDL的特点

VHDL是一种面向设计的、多层次、多领域且得一致认同的、标准的硬件描述语言。它主要有如下特点:

●能形式化地抽象表示电路的结构和行为,降低了硬件电路设计的难度。

●采用自上到下(Top-Down)的设计方法,支持逻辑设计中层次与领域的描述;它支持三个层次的描述:行为描述、RTL方式描述、门级描述(逻辑综合)。

●可进行系统的早期仿真以保证设计的正确性。

●主要设计文件是VHDL语言编写的源程序,便于文档管理。

●硬件描述与实现工艺无关。

由于VHDL语言已作为一种IEEE的工业标准,因而其语言标准、规范、语法比较严格,易于共享和复用。而且,VHDL设计技术齐全、方法灵活、支持广泛。目前大多数EDA工具几乎在不同程度上都支持VHDL语言。

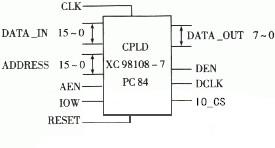

2 CPLD外部引脚说明

该方案中所用的芯片是Xilinx公司的CPLD 9500系列芯片,其类型为XC95108-7 PC84.这种芯片共有84个外部引脚,其中5个引脚接地,6个引脚接电源,4个引脚用于JTAG,剩下的引脚为I/O引脚。根据EISA总线的信号特征和信源的要求,该芯片所使用的外部引脚为如图1所示。

图1 CPLD芯片结构引脚简图

中输入信号:

DATA_IN 15~0 输入的数据信号

ADDRESS 15~0 输入的地址信号

RESET 复位信号

AEN 地址允许信号

CLK 输入时钟信号

IOW I/O写信号

输出信号:

IO_CS 16位I/O片选信号

DATA_OUT 7~0 输出的数据信号

DEN 输出数据使能信号

DCLK 输出数据时钟信号

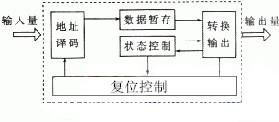

3 系统整体设计

系统启动后,主机向I/O口发出地址信号。AEN为低电平时,系统进行地址译码。译码成功后,产生一使能信号ENABLE打开数据暂存单元。数据到来后,数据暂存单元将总线上的16位并行数据锁存在暂存器中,同时产生一允许信号PERMIT,允许进行数据格式转换。接下来系统根据当前所处的状态进行选择输出,完成格式的转换,并产生相应的输出数据使能信号DEN和输出数据时钟信号DCLK.整个过程结束后,将各信号复位,开始新的转换周期。因此,整个系统应包括五个逻辑部分:地址译码、数据暂存、状态控制、复位控制、转换输出。

3.1 系统的整体框图

系统的整体框图如图2所示。

图2 系统结构框图

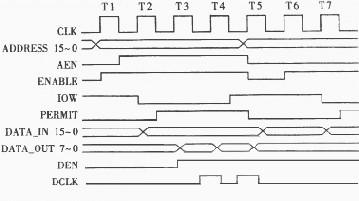

3.2 系统的工作时序

转换过程的时序如图3所示。

图3 系统功能时序图

4 VHDL语言描述

4.1 各单元模块的描述

地址译码单元

计算机与I/O设备间的正确通信是通过对I/O空间的寻址操作来完成的。每个I/O端口都分配了一个地址。在该方案中,将端口的地址设定为0280H,采用完全译码的方式。同时为了避免DMA操作控制总线,设计时让aen亦参与译码,并由时钟信号进行触发控制。译码成功后,产生一使能信号enable(高电平有效),同时将io_cs信号拉低。

数据暂存单元

enable信号无效时,数据暂存单元为高阻状态。该信号和写信号iow(低电平有效)都变为有效后,在接下来的一个时钟的下降沿(确保采样时数据有效),将总线上的数据读入数据暂存单元,并产生一允许信号permit,允许系统进行格式转换。

状态控制单元

这是系统的控制部分。系统状态的控制是由系统的控制信号simbol、sign在时钟信号的驱动下实现的。系统每完成8位数据的输出,在同一时钟的下降沿,状态发生改变,产生另外一控制信号varb(低电平有效)。复位后,系统又回到初始状态。状态变化过程如下:

转换输出单元

转换输出单元是系统的,它包括三个部分:数据格式的转换、数据使能信号DEN的输出、数据时钟信号DCLK的输出。数据的转换输出是由系统当前所处的状态决定的。permit信号有效后,在时钟的上升沿,转换输出单元检测系统状态:状态为first时,输出高8位;状态为second时,输出低8位;状态为third时,系统复位,从而完成转换,开始下一转换周期。在转换过程中,系统同时完成对信号simbol、sign(低电平有效)的控制。

输出数据使能信号DEN是根据MPEG-2标准码流格式产生的,用于数据信号的同步。在MPEG-2标准中,码流是以包的形式传送的。每一个数据包都有一个统一的包标识符PID,它的十六进制形式为47H.从包中的个字节(47H)开始,DEN变为有效(高电平),并保持到第188字节。在接下来的16个字节时间里,DEN保持低电平。

输出数据时钟信号DCLK用作解复用单元的采样时钟,它是由控制信号sign、permit以及系统当前所处的状态控制产生的。为了保证采样时数据保持有效,DCLK的输出比相应的输出数据要延迟半个机器周期。

复位控制单元

转换结束后,需要对系统复位,保证下一转换的顺利进行。复位信号的产生取决于三个控制量:系统当前状态为third、控制信号varb为低电平、控制信号simbol为高电平。复位后,输出端为高阻状态,其他信号均为无效值。系统回到初始状态。

4.2 系统的门级描述

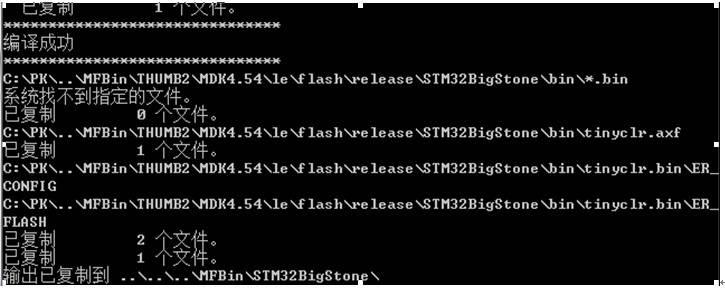

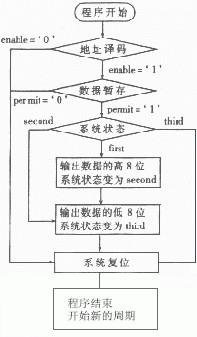

整个系统的VHDL描述流程如图4所示。

图4 系统的VHDL程序流程图

总之,机顶盒信源发生方案是机顶盒调试过程中的一个重要课题。本文提出的解决方案具有简单、实用、易实现的特点,经实践证明是可行的。同时在硬件实现时采用了VHDL的设计方法,也给整个方案提供了很大的灵活性。如果采用传统的方法来实现该方案,则首先要选择通用的逻辑器件,然后进行电路设计,完成各独立功能模块,再将各功能模块连接起来,完成整个电路的硬件设计,才能进行仿真和调试,直至整个系统的完成。这样一个过程往往需要比较长的时间,而且费时费力,特别是对一项大的工程。而采用VHDL这类高层设计技术,设计人员只需专心于设计方案和构思上,描述、编译成功后,经过系统综合,便可直接进行软件仿真和调试。整个系统的完成周期大大缩短,而且VHDL与工艺无关,它不限定模拟工具和设计方法,从而给设计师一个自由选择的余地。

随着电子工艺的日趋提高与完善,ISP(系统内可编程)功能为 PLD提供了更高的灵活性,使PLD能够向高密度、大规模的方向发展以满足复杂系统的要求,从而使可编程ASIC的设计逐步向高层设计转移。作为一种重要的高层设计技术,VHDL亦成为当代电子设计师们设计数字硬件时必须掌握的一种方法。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多