PLL1700是一款价廉、多时钟产生器锁相环(PLL)。它可从27MHz基准输入频率产生4个系统时钟。它通过不用外部元件使用户既能降低成本又节省空间,并可实现高性能无线电数/模变换器和模/数变换器所需的特低抖动性能。PLL 1700对于MPEG-2应用来讲是理想的器件。

MPEG-2(Moving Pictures Experts Group)系统需要几个时钟来控制环绕声AC-3译码器、数字信号处理器和数/模变换器。它接受27MHz MPEG-2视频时钟来实现音频/视频同步器并且为系统的其余部分提供所有的音频时钟。它所你生的4个音频系统时钟是:SCK01为33.8688MHz(固定),SCKO2为256fs,SCK03为384fs,SCK04为768fs(其中fs是取样频率,fs值为32kHz、44.1kHz、48kHz、88.2kHz、96kHz)。

表1 可选择的功能

| 功能 | 硬件模式(MODE=H) | 软件模式(MODE=L) |

| 取样频率选择 (32kHz,44.1kHz,48kHz) |

是 | 是 |

| 取样率选择(标准/倍频) | 是 | 是 |

| 每个时钟使能/断开 | 不是 | 是 |

表2

| FSI(引脚20) | FSO(引脚19) | 取样频率 |

| L | L | 48kHz |

| L | H | 44.1kHz |

| H | L | 32kHz |

| H | H | 备用 |

表3

| SRO(引脚1) | 取样率选择 |

| L | 标准 |

| H | 倍频 |

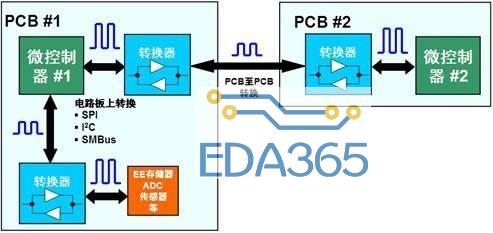

图1示出PLL 1700典型的连接电路,其功能由软件或硬件功能确定。当MODE(引脚2)为低态时用3线接口ML(引脚1)、MC(引脚20)、MD(引脚19)实现软件模式(串行模式)控制。当MODE为高态时用SRO)引脚1)、RSI(引脚20)、FSO(引脚19)进行硬件模式(并行模式)控制。可选择的功能示于表1。

表4 寄存器位图

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0 | 1 | 1 | 1 | 0 | 0 | CE6 | CE5 | CE4 | CE3 | CE2 | CE1 | SR1 | SR | FS1 | FS0 |

| 寄存器 | 位名称 | 说明 | |||||||||||||

| 模式 | CE6 | MCKO输出使能/禁止 | |||||||||||||

| CE5 | MCKO输出使能/禁止 | ||||||||||||||

| CE4 | SCK04输出使能/禁止 | ||||||||||||||

| CE3 | SCK03输出使能/禁止 | ||||||||||||||

| CE2 | SCK02输出使能/禁止 | ||||||||||||||

| CE1 | SCK01输出使能/禁止 | ||||||||||||||

| SR[1:0] | 取样率选择 | ||||||||||||||

| FS[1:0] | 取样频率选择 | ||||||||||||||

在硬件模式中用FS1和FS0选择取样频率(见表2);用SRO选择取样率(见表3)。其中标准取样频率指32kHz、44.1kHz、48kHz,倍频指64kHz、88.2kHz、96kHz。

表5 取样频率选择

| FS1 | FS0 | 取样频率 |

| 0 | 0 | 48kHz |

| 0 | 1 | 44.1kHz |

| 1 | 0 | 32kHz |

| 1 | 1 | 备用 |

软件模式用ML、MC、MD串行控制信号控制其功能。通过其内部16位程序寄存器控制其功能,此寄存器用MD输入。表4列出模式寄存器位图。软件模式中取样频率。取样速率的选择和时钟输出控制见表5、6、7。

表6 取样率选择

| SR1 | SR0 | 取样率 |

| 0 | 0 | 标准 |

| 0 | 1 | 倍频 |

| 1 | 0 | 备用 |

| 1 | 1 | 备用 |

PLL1700的典型应用是基于MPEG-2的系统,如DVD播放机、多媒体PC的DVD附加板、数字HDTV系统和机顶盒。典型应用示于图2。

表7 时钟输出控制

| CE1-CE6 | 时钟输出控制 |

| 0 | 时钟输出禁止 |

| 1 | 时钟输出使用 |

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多