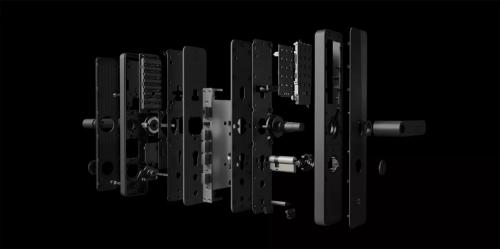

图1 系统硬件结构

2.1.1数字信号处理芯片

为满足语音信号处理的实时性要求,语音信号采集与处理系统应具有高速数据处理能力。本系统采用TMS320VC5416芯片作为信号处理芯片。

2.1.2音频CODEC模块

本系统的CODEC模块以TLV320AIC23芯片为核心。

2.1.3电源模块

VC5416属于低功耗定点芯片,采用双电源供电。电源由内核电源(CVdd)和I/O电源(DVdd)两部分构成,其中内核电源为1.8V,I/O电源为3.3V。内核电源采用1.8V供电可以降低功耗;I/O电源采用3.3V供电使得芯片可以直接与外部低压器件接口,而不需要额外的电平转换电路。本系统采用TI公司的TPS73HD318(简称HD318)作为电源输入芯片,HD318提供的两路输出电压一路为1.8V、一路为3.3V。另外该芯片提供的宽度为200ms的低电平复位脉冲还可以用来作为VC5416的上电复位信号。AIC23芯片具有单电源(5V电源)和双电源(3V数字电源+5V模拟电源)两种供电模式,本系统选择双电源供电模式,这样AIC23和VC5416之间就可以直接联接而不需要其它电平转换芯片。

2.1.4 JTAG仿真接口

系统由硬件仿真器XDS510/PP通过JTAG仿真接口和计算机相连,用户可以通过此接口向VC5416芯片加载程序并观察芯片内部存储器的数据,完成系统仿真及程序调试的任务。如果系统需要以脱机方式工作,可以用JTAG仿真接口将用户程序烧录到Flash Rom中,再通过设置启动方式引脚确定系统从片外ROM启动。

2.2硬件接口设计

VC5416有3个McBSP,可以方便地利用其中2个McBSP完成对AIC23的控制和通信,其中VC5416的McBSP0与AIC23的数据口相连,McBSP1与AIC23的控制口相连。

AIC23芯片是一个可编程芯片,内部有11个16位寄存器,控制接口具有SPI和I2C工作方式,这两种工作方式由MODE引脚来选择,即:MODE=0为I2C模式;MODE=1为SPI模式。 [page]

AIC23与VC5416的接口电路见图2。

图2 AIC23与VC5416的接口电路

VC5416的2个多通道缓冲串口McBSP分别配置为I2C模式和SPI模式。McBSP0作为数据的发送和接收端口;McBSP1对CODEC写控制字,作为控制端口;AIC23作为从设备,因此设置为Slave模式,而VC5416则设置为Master模式,Codec采样率设置为8kHz。

2.3 BOOTLOADER设计

VC5416片内ROM中有固化的自加载程序(BOOTLOADER),但它对被加载程序的大小有限制。在使用8bit Flash的情况下,只能加载小于16KWord的内容。而三个速率的SELP算法程序区和数据区的总数据量远远超过16KWord,显然只使用片内的BOOTLOADER是不能满足需要的。所以必须自己写加载程序。首先由VC5416片内的BOOTLOADER把自己写的加载程序加载到片内RAM,然后执行这段加载程序,加载其它部分。这里需要解决的一个主要问题就是Flash数据和片内地址空间的映射关系。由于SELP算法的程序数据总量很大,所以必须用到片内扩展的程序区,也就是说MP/MC标志位需要设为0。从此时的Memory Map中可以看出,VC5416可以访问的每块连续片外地址空间只有32K,所以Flash数据只能按照每页32K的方式分页映射到片内地址空间。使用FPGA可以很方便地控制哪页Flash数据映射到片内中,这部分的原理框图如图3所示。

图3 BOOTLOADER原理

3接口软件设计

本系统的软件采用C语言和汇编语言混合编写。由于是利用VC5416的McBSP口来控制AIC23芯片,且2个McBSP口设置成不同的工作方式,所以必须把McBSP初始化为符合AIC23芯片的控制命令时序和要求的工作模式。由于篇幅本文只列出对VC5416及AIC23芯片初始化设置时的部分代码。

3.1 TMS320VC5416初始化

SWWSR=0x7fff;/程序、数据、I/O空间

SWCR=0x0001;/等待周期为7×2=14

BSCR=0x8006;/按32KW分区,HD[7:0],D[15:0]Hold

CLKMD=PLL_DIV_INIT;

Waitloop(0x0400);

CLKMD=PLL_LOCK_INIT_X(5);

Waitloop(0x0400);

PMST=0x0168;/中断向量表定位在0X100,MP/MC=1

OVLY=1,DROM=1;

3.2 TLV320AIC23初始化

为使AIC23正常工作并产生预期的音频效果,必须对其相应的寄存器进行配置。首先对VC5416的I2C模块初始化,将AIC23总线上的地址写入从机地址寄存器ICSAR;再把相应的AIC23内部映射寄存器的地址和待写数据合并为16bit控制字,逐次写入ICDXR,并通过I2C总线发送给AIC23,即可完成对AIC23的初始化配置。

AIC23初始化的部分源代码:

Unsigned int codec_buf[9]={OX1e00,OXOc00,OxO81a,OxOaO4,OxOe01,0x1020,0x1021,0x0117,OxO5f9};

Port_sub_address=(unsigned int*)MCBSP_SPSA_ADDR(1);

Port_sub_index_reg=(unsigned int*)MCBSP_SPAD_ADDR(1);

*Port_sub_address=MCBSP_SPCR2_SUBADDR;

For(i=O;i<9;i++){

While(!(*Port_sub_index_reg&(MASK_BIT(XRDY))));

Set_codec_cs_low();

MCBSP1_DXR1=codec_buf[i];

While(!(*Port_sub_index_reg&(MASK_BIT(XRDY))));

Set_codec_cs_high();}

4结束语

本文的创新点是根据TI公司的DSP芯片TMS320VC5416和语音CODEC芯片TLV320AIC23的特性,设计并实现了一个语音采集处理系统。该系统具有很强的处理能力和灵活的外围接扣电路。实践证明它能够满足实时信号处理的要求,可以作为一种语音信号处理算法研究和实时实现的通用平台。

参考文献:

[1]张雄伟,曹铁勇.DSP芯片的原理与开发应用(第二版)[M].北京:电子工业出版社,2OO0

[2]任丽香,马淑芬,李方慧.TMS220600系列DSP的原理与应用[M].北京:电子工业出版社,2OOO

[3]戴明祯,周建江.TMS320VC54x DSP结构、原理及应用[M].北京:北京航空航天大学出版社,2001

[4]TMS320VC5416 Bootloader.SPRA602C.Texas Instrument, February 2001

[5]TMS320VC5416 Fixed-Point Digital Signal Processor Data Manual.TI Corporation,2003

[6]Stereo Audio CODEC,8kHz-96kHz,with Integrated Head Phone Amplifier TLV320AIC23.TI Corporation,2001

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多