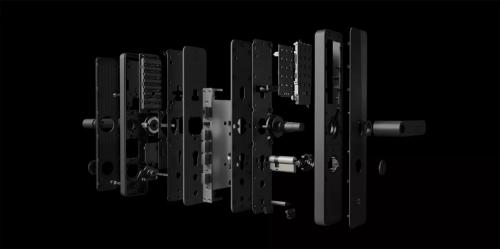

现在大多数的CPLD(复杂可编程逻辑器件)都采用可减少功耗的工作模式,但当系统未使用时,应完全切断电源以保存电池能量,从而实现很多设计者的终极节能目标。图1描述了如何在一片CPLD 上增加几只分立元件,实现一个节省电池能量的系统断电电路。在本例中,使用的CPLD是Altera EPM570-T100。使用一只外接P沟道MOSFET Q1和一只国际整流器公司 的IRLML6302(或等效器件),构成IC1 CPLD的一个电源控制开关。CPLD和开关矩阵控制着MOSFET的栅极,当用户按下一个开关时,在Q1上施加开关的偏压。CPLD内带一个嵌入的计时器,用于监控开关和系统的工作。当系统处在一个特定的不工作周期内时,计时器会去掉 MOSFET 的栅极驱动,使CPLD以及连接到MOSFET上的其它元器件断电。

Q1的源极连接到电池的正极,其漏极连接到IC1的VCC(INT)、VCC(IO1)和VCC(IO2)电源脚和其它需要断电控制的元件。当电源断开时,一只1kΩ的上拉电阻R3将Q1的栅源电压保持在0V,维持其关断状态。当切断IC1电源时,它通过CPLD的断电管脚建立一个对地的泄漏路径。EPM570T100带有热插保护,可将任何用户可接触器件的I/O脚限流在 300mA 以下。因此,即使在最差情况下,R3上产生的I/O脚电压也不会达到FET的0.7V最小栅极阈值导通电压。

按下任何开关都会通过开关的触点以及相应的二极管建立一个电流路径,因此在R3上产生约2.3V的栅源偏压,这个电压足以在约100ms时间内使Q1导通,并为IC1供电。当激活机械开关时,它们的最小导通时间至少为3ms,而一个典型的操作员的按/放时间至少要30ms。由于人的响应时间相对较慢,在操作者松开开关以前,CPLD可以完成导通、复位内部电路,并将使Q1导通的断电管脚维持在逻辑零状态。

除了用户设定的应用逻辑以外(图中未画),CPLD的电源控制逻辑增加了一对标准参数的库宏电路,它由Altera的Quartus II开发工具生成。内部的4.4MHz±25%振荡器Altufm_osc驱动一个模块化44 million LPM(库参数化模块)计数器。CPLD应用逻辑产生的逻辑低电平信号或关闭任何开关时都会使计数器复位。当复位计数器时,它的执行信号变低,驱动外接的断电管脚。当去掉复位时,反相的执行信号会重新开始 LPM 计数器的运行。

如果所有开关均为开,应用逻辑为不工作状态,则计数器在约10秒内计数到4400万,然后内部执行信号变高电平,关断计数器,并保持执行信号为高电平。接下来,断电管脚向VCC爬升,当断电管脚电压达到2.3V时关断Q1。关断CPLD的电源会使断电管脚进入三态(或不连接)模式,而R3使Q1保持关断。

用户可以使用符合JTAG标准的命令,用一根下载电缆连接到一个厂家定义的10脚插头上,对EPM570-T100进行配置。该过程需要在配置前、中、后按一个外接的开关,以保证CPLD能在配置过程中获得电源。可以通过改变计数器的模块,将不工作时间设置为任何需要的值。虽然电源、地和JTAG信号都使用专用的器件管脚,但也可以将任何通用CPLD I/O脚设定为开关输入和断电输出。

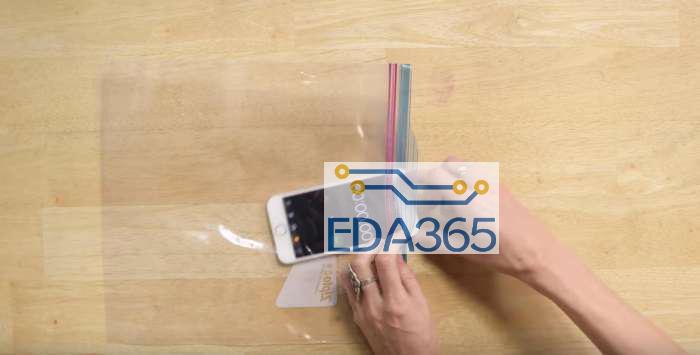

如果你的应用需要一个按键开关矩阵,则可以用n个二极管搭成一个nxm开关,进行有效的上电检测(图2)。在本例中,一排排开关通过二极管D1~D4连接到MOSFET的栅极。电阻R8~R11为每行开关提供一个对地通路,并只在开关闭合时承载电流,使行输入为低电平,同时保证只消耗最小的电源电流。

当用户按压任一开关时,Q1的栅极为低电平,CPLD接通。在用户释放开关以前,一个快速的CPLD上电例程,扫描开关阵列的各行和各排,以确定用户按下的是哪个开关。并且重置信号复位LPM计数器的不工作定时器。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多