摘 要:本文提出了一种基于FPGA的宽带中频数字接收机的实现方法。

引言

在现代通信系统中,人们提出了各种各样的全数字调制解调方案,全数字接收机的研究则是其中的关键,其中正交解调技术由于可以实现信号相位和幅度信息的提取,因而越来越受到广泛的应用。

与其它几种解调方式相比QPSK调制方式抗噪声性能好,功率频谱段占用少,数据传输率高,是一种较好的调制方式。对于宽带、高载频的QPSK调制信号,如果用信号最高频率两倍以上的时钟采样,现有的器件根本无法满足要求,所以必须采用欠采样技术,降低系统对ADC器件和信号处理器件的性能要求。

现在大规模集成电路设计已经发展到在一片芯片上集成一个复杂系统的规模,所以单模块、单芯片的接收机不仅是可实现的,而且是一种必然趋势。用软件实现接收机解调功能并利用高速FPGA芯片,可以把整个接收机解调部分用单芯片实现;通过修改软件,可以改变接收机的功能,而且由于在软件、硬件上都是一个模块,可以方便的进行功能扩展以及与其它系统连接,这也符合软件无线电的思想。基于以上原因,在此提出一种单芯片FPGA实现的宽带中频数字接收机系统。

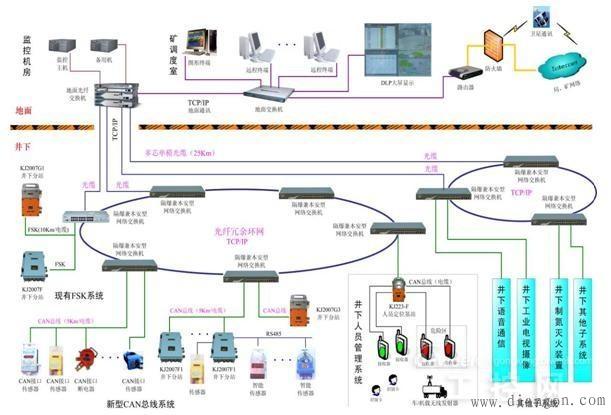

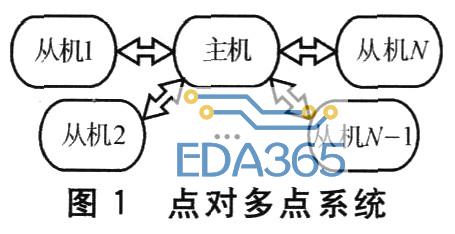

图1 中频数字接收机

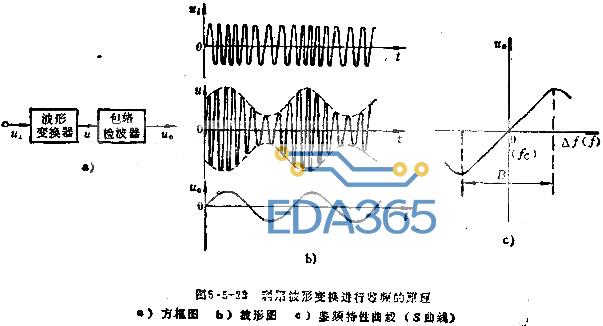

图2 NCO结构图

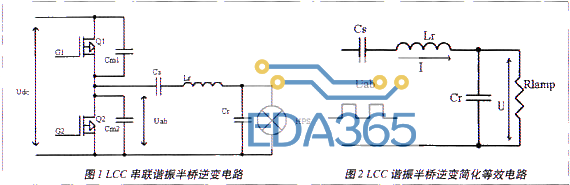

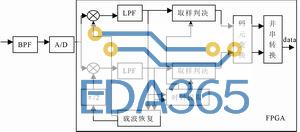

图3 解调器软件实现

系统结构

该接收机实现对载波频率70MHz、数据率9.856Mbps、最大载波频偏±80kHz的QPSK调制信号解调。接收的调制信号经过AGC和带通滤波器,通过高速ADC中频采样,数字信号送FPGA实现解调功能(见图1)。

由于接收信号是高载频、带通信号,所以必须采用欠采样技术。对于本系统,信号载频70MHz、带宽约10MHz,则

fh=n·B+k·B

其中B是带宽,这里取10MHz,n=7,k=0.5根据采样定理,采样最低频率为:

fs=2B(1+k/n)

大约等于21.4MHz。采样频率的选择要考虑两个因素:一是要满足带通信号的抽样定理,抽样后频谱不能发生混叠;二是采样后的数据率要满足后级处理的要求。对于本系统采样频率选40MHz,采样后信号频谱会镜像到以10MHz为中心带宽10MHz的频段上。

A/D变换后数字信号直接进FPGA完成解调,提取调制数据。由于采用全数字解调方式,I、Q两路数字混频器和滤波器的特性完全一致,避免了模拟解调时由于模拟器件特性的一致性和稳定性不理想而导致的I、Q通道间幅度不平衡及相位正交误差较大的现象。对于采用相干解调的接收机,由于接收到的调制信号通常会有多普勒频移和载波频差,所以解调性能的好坏主要取决于载波恢复和时钟提取的精度。

载波恢复电路采用数字COSTAS环,它将载波提取和解调结合起来,在提取载波的同时完成解调功能。这种环路具有矩形的鉴相特性,具有较小的静态相差和较大的锁定带宽;同时,其鉴相特性有四重相位模糊度,所以必须在调制时增加绝对/相对码变换电路,解调时加上相对/绝对码变换电路克服相位模糊。载波恢复电路中的核心是本地振荡源的产生,在数字电路中采用数控振荡源(NCO)产生本地载波,NCO(见图2)频率捷变速度快、相对带宽很宽、频率分辨率高,能输出完全正交的两路载波。

NCO的输出频率为:

fnco=DF·fclk/2π=FCW·fclk/2a

其中FCW是频率控制字,a是频率控制字字长,fclk是时钟频率。

时钟提取(位同步)采用超前-滞后数字锁相环电路,输入相位基准与本地参考时钟n次分频后的相位脉冲进行相位比较,产生超前或滞后脉冲,在控制电路作用下调整码元同步脉冲的相位。调整的原理是当参考相位脉冲超前于输入相位基准时,相位比较器输出超前脉冲,触发扣除门扣除一个脉冲,参考相位脉冲的相位就推后1/n周期;相反,当参考相位脉冲滞后于输入相位基准时,相位比较器输出滞后脉冲触发添加门添加一个脉冲,参考相位脉冲的相位就提前1/n周期。经过反复调整相位,即实现码元同步,产生位同步时钟。

完成载波恢复、时钟同步后,进行码元的取样判别、相对码/绝对码变换以及并/串转换,最终,输出解调数据。

软件接收机及硬件实现

在现代电子设计中,为了缩短设计周期,电子设计自动化(EDA)逐渐成为项目设计成败的关键。Quartus II是Altera公司提供的FPGA开发平台,集成了编辑、仿真、综合、芯片编程等FPGA开发所需全部工具,配合其他系统级仿真软件,可以大大缩短系统设计周期。FPGA芯片采用Altera公司的EP1S10系列,具有丰富的内部资源和齐全的外部接口。

综合后芯片主要资源占用如表1。

软件实现过程中,最关键的是要正确、有效的实现高速、复杂的组合逻辑和时序逻辑电路,用可综合的硬件描述语言程序实现系统功能。由于解调部分全部在FPGA中完成,整个系统只需要一片FPGA芯片和相应的配置芯片以及A/D转换器、模拟滤波器、射频处理电路再加上电源供给电路和信号输出接口,硬件结构非常简单。

系统仿真及实测结果

图4是系统在载波频差+20KHz时仿真结果,图5是系统硬件实测时I、Q两路在示波器上显示的解调结果。

结语

经过实际硬件测试,各功能模块工作正常,接收机完全满足系统设计要求;而且系统结构简单、功耗低、调试方便。随着大规模集成电路设计技术的不断发展,高速数字信号处理器的产生以及高效EDA工具的应用,复杂系统的模块化集成将会越来越容易。■

图4 系统仿真结果

图5 I、Q解调实测结果

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

热门文章

更多

热门文章

更多